STM32C0システム設定コントローラのプレゼンテーションへようこそ。

#### 概要

- STM32C0xx マイクロコントローラは一連の設定レジスタを備えている

- システム設定コントローラの主な目的は次の通りである

- I<sup>2</sup>C高速モードプラスの高駆動の有効化/無効化

- 赤外線タイマ(IRTIM)モジュールの設定

- PA11とPA12のGPIOのPA9とPA10への再配置

- アドレス0x0000 0000でアクセス可能なメモリの選択

- 各割込みラインからの保留中の割込みのステータス

- 安全機能の有効化/無効化

2

STM32C0マイクロコントローラは、SYSCFGモジュールにー連の設定レジスタを備えています。

システム設定コントローラでは、以下の各機能を利用できます。

- I2C高速モードプラスの高駆動の有効化/無効化

- 赤外線タイマ(IRTIM)モジュールの設定

- PA11とPA12のGPIOのPA9とPA10への再配置

- アドレス0x0000 0000でアクセス可能なメモリの選択

- 各外部割込みラインからの保留中の割込みのステータス

- 安全機能の有効化/無効化

### I2C I/O 高速モード

• STM32C0のI2Cコントローラで3つの速度をサポート

| モード           | ビットレート     | 追加の出力駆動 I/O |

|---------------|------------|-------------|

| 標準モード(Sm)     | ≤ 100 Kbps | なし          |

| 高速モード(Fm)     | ≤ 400 Kbps | なし          |

| 高速モードプラス(Fm+) | ≤ 1 Mbps   | あり          |

- SYSCFGモジュールによって追加の出力駆動を制御

- I2Cが選択されたオルタネート機能でない場合でも有効にできる

3

STM32C0に存在するI2Cコントローラは、次の3つの速度をサポートします。

- 標準モード、最大ビットレートは100Kビット/秒

- 高速モード、最大ビットレートは400Kビット/秒

- 高速モードプラス、最大ビットレートは1Mビット/秒。

高速モードプラスは高駆動機能を必要とします。これは SYSCFGモジュールで有効化されます。

高駆動はピンレベルで制御されるため、他のオルタネート機能でも使用可能です。

## I2C I/O 高速モード

| ピン   | I <sup>2</sup> C オルタネート機能 | I <sup>2</sup> C FM+ モードの有効化                             |

|------|---------------------------|----------------------------------------------------------|

| PC14 | I2C1_SDA                  | SYSCFG_CFGR1[I2C_PC14_FMP]=1 OR SYSCFG_CFGR1[I2C1_FMP]=1 |

| PA9  | I2C1_SCL                  | SYSCFG_CFGR1[i2C_PA9_FMP]=1 OR SYSCFG_CFGR1[i2C1_FMP]=1  |

| PA10 | I2C1_SDA                  | SYSCFG_CFGR1[I2C_PA10_FMP]=1 OR SYSCFG_CFGR1[I2C1_FMP]=1 |

| PB6  | I2C1_SCL                  | SYSCFG_CFGR1[i2C_PB6_FMP]=1 OR SYSCFG_CFGR1[i2C1_FMP]=1  |

| PB7  | I2C1_SDA                  | SYSCFG_CFGR1[i2C_PB7_FMP]=1 OR SYSCFG_CFGR1[i2C1_FMP]=1  |

| PB8  | I2C1_SCL                  | SYSCFG_CFGR1[i2C_PB8_FMP]=1 OR SYSCFG_CFGR1[i2C1_FMP]=1  |

| PB9  | I2C1_SDA                  | SYSCFG_CFGR1[i2C_PB9_FMP]=1 OR SYSCFG_CFGR1[i2C1_FMP]=1  |

4

I2C1ピンの高駆動機能は、I2C\_PA9-10\_FMPおよび I2C\_PB6-9\_FMPビットを介してピンごとに、またはI2C1\_FMP ビットをセットすることによってグローバルに設定できます。

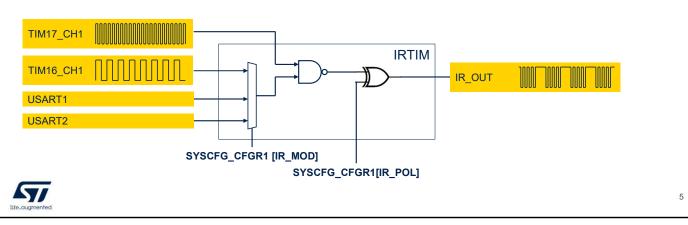

#### IRTIMモジュール設定

- 赤外線タイマ(IRTIM)モジュールは、USARTおよびタイマソースを利用して変調エンベロープを生成する

- SYSCFGモジュールはソース信号を選択するために使用される

- また、出カインバータをアクティブにするためにも使用される

赤外線タイマ(IRTIM)ユニットには、USARTまたはTIM16のいずれかによって提供される変調エンベロープ信号が必要です。 SYSCFG\_CFGR1レジスタのIR\_MODフィールドは、関連する 入力マルチプレクサを制御します。

SYSCFG\_CFGR1レジスタのIR\_POLビットは、出力信号を反転するかどうかを選択します。

#### GPIOの再配置

• PA12とPA11の2つのGPIOは、それぞれPA10とPA9に再配置できる。これにより、ピンがパッケージでネイティブに使用できない場合にそれらの機能にアクセスすることができる

life.augmented

6

SYSCFG\_CFGR1レジスタのPA11\_PA12\_RMPビットがセットされると、PA11とPA12のオルタネート機能がPA9とPA10のピンに再配置されます。

PA11とPA12には専用のI/Oパッドがないため、このオルタネート機能が必要な場合に便利です。

### GPIOマルチボンディング

- ・ パッケージ上の1つのピンがシリコン上の複数のパッドに結合

- つまり、SO8パッケージの4番ピンにはPAO、PA1、PA2、PF2-NRSTがボンディングされている

- 複数のGPIOが同じピンに内部接続されている場合、SYSCFG\_CFGR3レジスタにより1 つだけを割り当て、デジタル出力のように対応するGPIOx\_MODERレジスタによって指定 した設定を維持可能

- 他のGPIOは、対応するGPIOx MODERレジスタ設定に関係なく、強制的にデジタル入力モードになる

たとえば、パッケージ上の1つのピンをシリコン上の複数のパッドに接続できます。PAO、PA1、PA2、PF2-NRSTはSO8パッケージの4番ピンボンディングされています。

複数のGPIOが同じピンに内部接続されている場合、

SYSCFG CFGR3レジスタを使用して、対応する

GPIOx\_MODERレジスタで指定された設定を維持するように GPIOを割り当てることができます。

他のGPIOは、対応するGPIOx\_MODERレジスタ設定に関係なく、強制的にデジタル入力モードになります。

#### GPIOマルチボンディング-セキュリティ

- デフォルトの安全な設定は、FLASH\_OPTRのSECURE\_MUXING\_ENビットをクリアすることで上書き可能

- GPIOの設定が間違っている場合、接続されたGPIOで競合(短絡)が発生する可能性があるため、上書きする場合は十分に検討する必要がある

8

SECURE\_MUXING\_ENビットがFLASH\_OPTRに設定されている場合のデフォルト設定は、前のスライドで説明されています。

任意の2つのGPIOが接続され、異なる出力レベルのプッシュプル出力構成が発生することはありえないため安全です。ただし、アプリケーションによっては、複数のGPIOを結合して使用し、特定のピンの合計出力電流を増加させることで、ピンの最大出力電流を増やすことが有益な場合があります。FLASH\_OPTRでSECURE\_MUXING\_ENビットがクリアされている場合、ユーザはGPIOx\_MODERレジスタで結合されたより多くのGPIOでの出力を有効にすることができます。ユーザソフトウェアは、GPIO間に競合がないことを確認する必要があります。

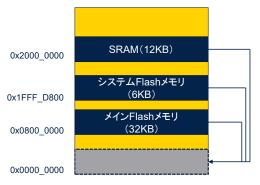

## メモリマッピング

- 3つのメモリをアドレス0x0000 0000にエイリアスできる

- メインFlashメモリ

- システムFlashメモリ

- 内蔵SRAM

SYSCFG\_CFGR1[MEM\_MODE] =0bX0:メインFlashメモリ =0b01:システムFlashメモリ =0b11:SRAM

デフォルト値は、ピンBOOTO、nBOOT1、nBOOTO、BOOT\_SELの オプションビットおよびBOOT\_LOCK制御ビットの状態によって異なる

SYSCFG\_CFGR1レジスタのMEM\_MODEフィールドは、アドレス0でアクセス可能なメモリを選択します。

メインFlashメモリ、システムFlashメモリ、SRAMの3つのメモリをアドレス0にエイリアスできます。

このフィールドのデフォルト設定は、ブートピン、オプションバイト、および制御ビットに依存することに注意してください。

9

#### 安全機能

- SYSCFG CFGR2レジスタは、安全機能を制御

- Cortex®-M0+ロックアップ発生時、TIM1/16/17ブレーク入力のアサートを有効/無効にするために1ビットを使用

- 障害またはスーパーバイザコールが優先度-1または-2で発生すると、Cortex-M0+は自動的にロックアップ状態になる

10

SYSCFG\_CFGR2レジスタには、安全性にリンクされている制御およびステータスビットが含まれています

LOCKUP\_LOCK制御ビットは、Cortex-M0+のロックアップ状態のタイマブレーク入力への接続を有効にします。

これにより、アプリケーションのクラッシュ中に、タイマ出力を既知の状態にすることができます。

一度プログラムされると、次のシステムリセットまで接続はロックされます。

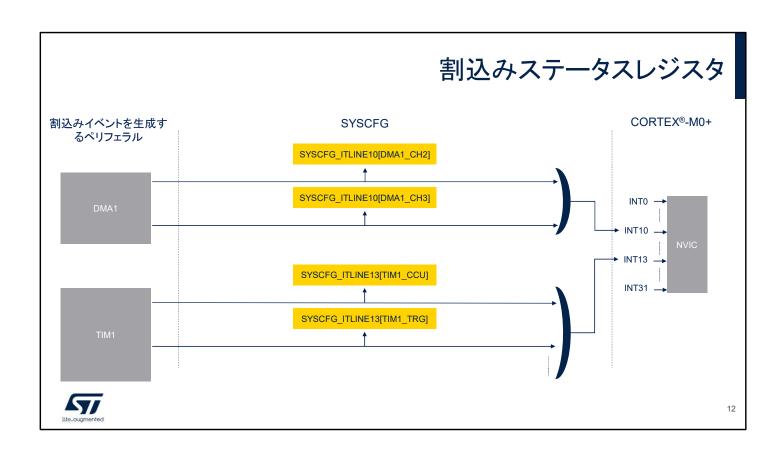

#### 割込みラインステータスレジスタ

- SYSCFGモジュールには専用の読出し専用レジスタが実装されており、各割込みラインに関連付けられたすべての保留中の割込みソースを1つのレジスタへ集める

- これにより、どのペリフェラルで処理が必要かを1回の読出し操作でチェックできる

- これらのレジスタの利点を説明するために、次のスライドではEXTIの割込みリクエストの管理について 説明

11

SYSCFGモジュールは、4個の割込みラインステータスレジスタをサポートしています。

これらは、特定の割込みラインに関連付けられたすべての保留中の割込みソースを同じレジスタ内に持つことにより、ソフトウェアがEXTI割込みの原因を簡単に見つけることができるようにします。

STM32C0には、外部割込みをアサートできるペリフェラルごとに1つの割込みラインステータスレジスタがあります。 これらの割り込みラインステータスレジスタの利点については、 次のスライドで説明します。

図の左側は、外部割込みをアサートできるペリフェラルを表します。

SYSCFG割込みステータスレジスタは図の中央に表示されます。

NVICへの外部割込みの接続は、図の右側に示されています。

## 関連ペリフェラル

- このペリフェラルにリンクされている次のトレーニングを参照:

- I<sup>2</sup>C(Inter-Integrated Circuit)

- 赤外線タイマインタフェース(IRTIM)

- 汎用入力/出力(GPIO)

- 割込み(NVIC、EXTI)

- タイマ(TIM)

13

このトレーニングに加えて、I2C、IRTIM、GPIO、割込み、タイマの各トレーニングを参照してください

### 参照

- 詳細については、次のドキュメントを参照:

- AN2606:STM32 microcontroller system memory boot mode

14

詳細については、アプリケーションノート AN2606:STM32 microcontroller system memory boot modeを参照してください。

# Our technology starts with You

© STMicroelectronics - All rights reserved.

ST logo is a trademark or a registered trademark of STMicroelectronics International NV or its affiliates in the EU and/or other countries. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>.

ありがとうございました