STM32 マイクロコントローラに搭載されている高機能制御タイマ、汎用タイマ、基本タイマのプレゼンテーションによこそ。ここでは、タイミングに関連したイベントの処理、波形生成、入力信号のタイミング特性の測定に有用な主な機能について説明します。

- 複数のタイマ・ユニットがタイミングリソースを提供

- 内部(トリガ、タイム・ベース)

- 外部、入出力用:

- 波形生成用(PWM)

- 信号の監視または測定用(周波数またはタイミング)

### アプリケーション側の利点

- 多彩な動作モードにより、CPU の負担を軽減し、インターフェース回路を最小限に抑える

- すべてのタイマインスタンスに対する單一アーキテクチャにより、スケーラビリティと使いやすさを実現

- モータ制御とデジタル電力変換のアプリケーションにも完全対応

STM32 には、ソフトウェアタスクやハードウェアタスク向けのタイミングリソースを提供する複数のタイマが搭載されています。ソフトウェアのタスクは主に、タイムベースの提供、タイムアウトイベントの生成、タイムトリガで構成されています。ハードウェアのタスクは I/O に関連しています。タイマは出力で波形を生成し、入力される信号パラメータを測定し、入力で外部イベントに反応することができます。

STM32 タイマは非常に汎用性が高く、複数の動作モードを提供することで、必要なインターフェース回路を最小限に抑え、反復的でタイムクリティカルなタスクから CPU を解放します。(低消費電力タイマを唯一の例外として)すべての STM32 タイマは、スケーラブルな同じアーキテクチャに基づいています。タイマの動作原理を一度理解すれば、それはどのタイマにも有効です。このアーキテクチャには相互接続機能が含まれており、複数のタイマを組み合わせてより大きな構成にすることができます。最後に、一部のタイマには、電気モータ制御と、照明やデジタルスイッチングモード電源などのデジタル電力変換のための専用機能が搭載されています。

# 主な機能

3

- すべてのタイマは、同じアーキテクチャに基づいており、以下の要素に関してスケーラブル：

- 入出力数(1~10)

- タイマ 1 の場合は 10: TIM1\_ETR, TIM1\_BK, TIM1\_BK2, TIM1\_CH1, TIM1\_CH1N, TIM1\_CH2, TIM1\_CH2N, TIM1\_CH3, TIM1\_CH3N, TIM1\_CH4

- 分解能(16 ビットまたは 32 ビット)

- 機能(PWM モード、DMA、同期、アップ／ダウンカウント)

- 複数のタイマのリンクと同期が可能

- 各タイマチャネルは入力または出力として個別に設定可能

- 監視とトリガの目的で、他のペリフェラルとの複数の相互接続が可能

これらは、STM32 タイマの主な機能です。すべてのタイマは、同じアーキテクチャに基づいており、このプレゼンテーションで後述する、いくつかの派生物で使用可能です。タイマは何種類もありますが、主な違いは、備えている入出力の数です。I/O を持たない純粋なタイムベースから、10 個の I/O を持つ高機能制御バージョンまで揃っています。ほとんどのタイマは 16 ビットカウンタを備えていますが、一部のカウンタは 32 ビットです。一部の機能は、最小の派生タイマには存在しないことがあります(DMA、同期、アップ／ダウンカウントモードなど)。

ほとんどのタイマは、リンクと同期を行って、より大きなタイムベースタイマを構築したり、同期波形の個数を増やしたり、複雑なタイミングと波形を処理したりすることができます。

タイマの内部では、どのチャネルもすべて入力(通常はキャプチャ用)または出力(通常は PWM 用)として、個別に設定可能です。

相互接続マトリックスにより、タイマは、たとえば ADC 変換の開始や内部クロックの監視など、他のペリフェラルのトリガとしての役目を果たすことができます。

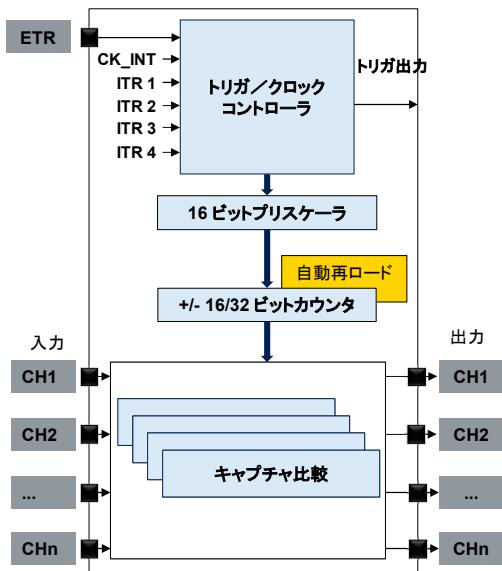

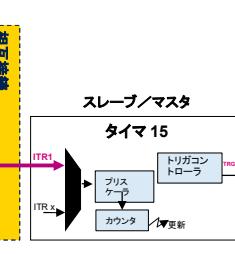

# ブロック図(TIM15)

4

このスライドは、標準的な TIM15 タイマのブロック図です。

タイマカーネルは、16 ビットアップカウンタと、カウント周期をプログラムするための自動再ロードレジスタで構成されています。2 つのタイマチャネルは、2 つのキャプチャ比較レジスタによって制御されます。

このカウンタは、タイマチェーンも担当するクロックおよびトリガコントローラによって供給されます。

内部トリガのインとアウトは相互接続マトリックスに接続されています。関連するプレゼンテーションを参照してください。たとえば、STM32G0 のタイマ 15 は ADC と DAC をトリガし、タイマ 1~3 のスレーブインターフェースを制御できます。

左側は入力ステージと入力調整回路、右側は出力ステージです。

入力と出力の両方の機能を持っていることを示すため、TIMxCH1 と TIMxCH2 が両側に示されていることに注意してください。

タイマ 15 はブレーカ入力をサポートしています。ブレーカ入力を使用すると、ブレーカイベントが発生するたびに、チャネル出力を事前定義された状態に自動的に設定することができます。

またタイマ 15 は、PWM 相補出力にデッドタイムを挿入するデッドタイムジェネレータユニット(DTG)もサポートしています。

このブロック図の各部分については、次のスライドで説明します。

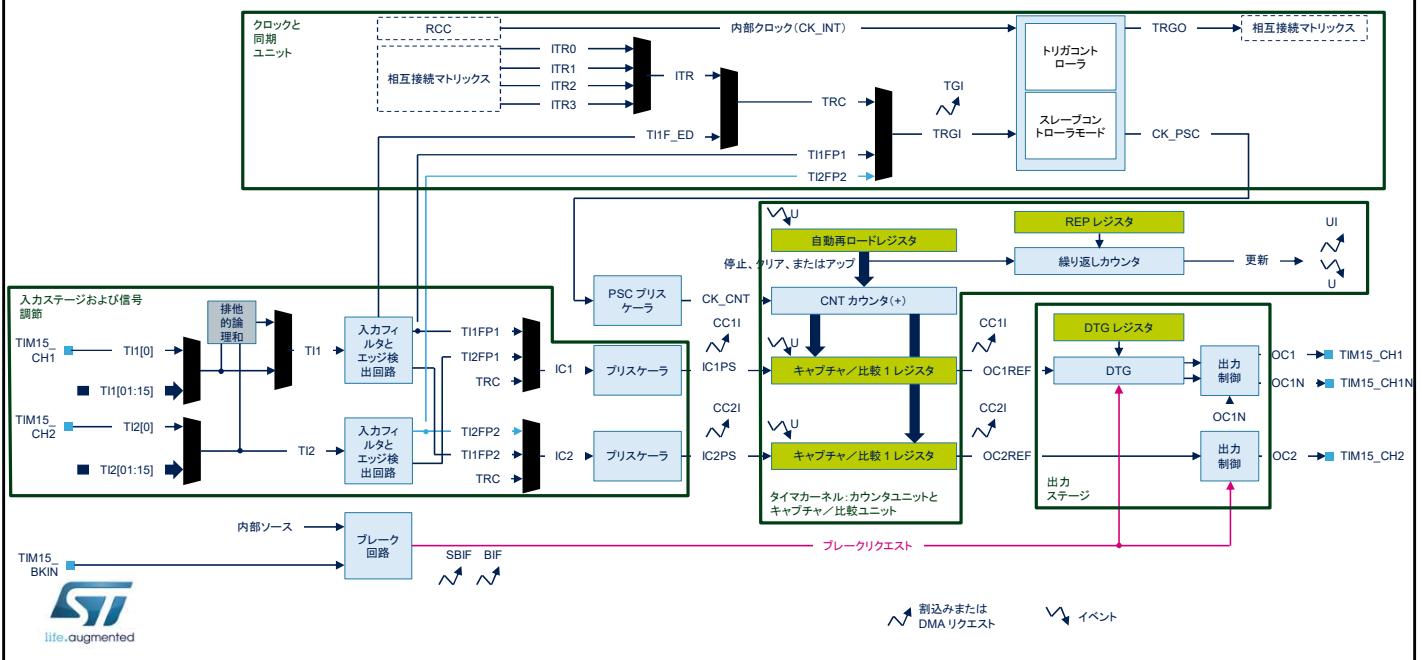

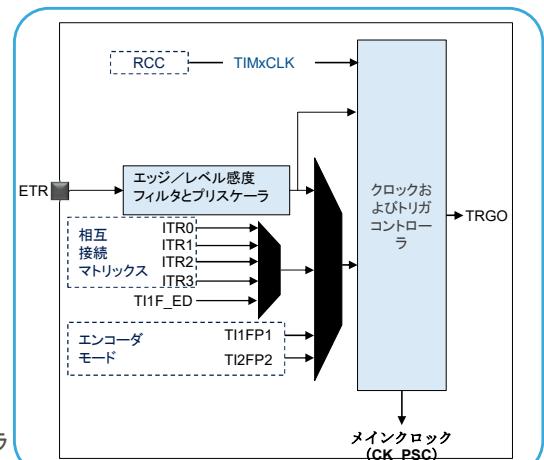

## タイム・クロック供給スキーム

5

## 複数の内部または外部クロック供給オプション

- TIMxCLK内部クロックには次のソースがある:

- APBプリスケーラ分周比が1、もしくはPCLK周波数の2倍にセットされている場合に、PCLK周波数で動作するTIMPCLK(すべてのタイマで選択可能)

- 高速タイマ1および15で選択可能なPLLQCLK

- 128MHz 最大

- 外部クロック供給ソース:

- 他のオンチップ・タイマ(ITRx入力)

- 入力ピン1および2(TI1、TI2)

- デジタル・フィルタとプログラム可能なエッジ感度を含む

- 多目的外部トリガ入力(ETR)

- デジタル・フィルタ、プログラム可能なエッジ感度、基本プリスケーラ(I2、I4、I8)を含む

- エンコーダからの直交信号

- エッジ検出回路(TI1F ED)

life... augmented

タイム 15 には複数のクロック供給オプションがあります。

タイマチェーンも担当するクロックおよびトリガコントローラが、カウンタ用クロックを処理します。

デフォルトクロックは、リセットおよびクロックコントローラから供給されます。

タイマクロック TIMPCLK は、PCI K(APB で使用される)から次のように生成されます。

- APB プリスケーラが 1 にセットされている場合、TIMPCLK 周波数は PCLK 周波数と等しくなります

- それ以外の場合、TIMPCLK 周波数は PCLK 周波数の 2 倍にセットされます。

タイマ 1 および 15 の場合は、PLLQCLK クロックを選択することもできます。この周波数は 128 MHz を超えないようにセットする必要があります。

外部タイマによるクロック供給により、外部イベントのカウントや、カウント周期を外部から調整することが可能となります。

クロックソースは、4 本の内部トリガ入力(ITR0～ITR3)の 1 本を使って、他のオンチップタイマから供給することができます。

入力ピン 1 および 2 は、外部クロックとしても機能し、オプションでスプリアスイベントを

除去するためのデジタルフィルタを使用することができます。

除去するためのデジタルフィルタを使用することができます。

外部トリガ入力(ETR)は、デジタルフィルタ、プログラム可能なエッジ感度、および必要に応じて受信信号の周波数を低減するための第1の基本的なプリスケーラステージを備えた外部クロックとして設定することができます。

TI1F\_ED エッジ検出器入力は、タイマクロックとしても使用できます。TI1F 信号の立ち上がりと立ち下がりの両方のエッジでパルスが生成されます。本来の目的ではありませんが、外部クロック(受信クロック周期ごとに 2 回カウント)で周波数 2 遅倍器として使用できます。

最後に、このプレゼンテーションで後述するように、エンコーダからの直交信号は、クロックヒルカウント方向を提供するように処理することが可能です。

# タイマ・クロック供給スキーム

6

## 複数の内部または外部クロック供給オプション

- タイマ1と15は、10ns 未満に分解能を向上させるために +100MHzでクロックが供給される

- 降圧コンバータの分解能の向上(100kHz PWMで10ビットの精度)

- 可変周波数共振コンバータの周波数ステップの低減(LLC など)、たとえば、200kHz のスイッチングで 0.4kHz の最大周波数ステップ(0.2%)

- 使用例

- タイマ1には3つの相補的なペアがある(LLCの1次側と2次側(同期整流)、境界通電モードPFC、降圧)

- タイマ15 には1つのペアのみがある(降圧、LLCの1次側)

タイマ 1 と 15 は PLLQCLK によってクロックが供給されます。PLLQCLK の周波数は 100 MHz より高くすることができます。これにより、降圧コンバータの分解能の向上と、LLC などの可変周波数共振コンバータの周波数ステップの低減が保証されます。

タイマ 1 には 3 つの相補的なペアがあり、LLC の 1 次側と 2 次側、および力率補正回路と降圧コンバータの境界通電モードをサポートするのに適しています。

タイマ 15 には、降圧電源や LLC の 1 次側コンバータで使用できる独自の相補ペアがあります。

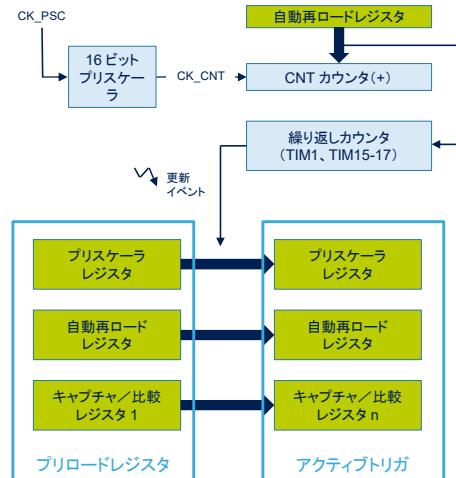

# カウント周期管理

7

## 微細かつ正確な周期設定

- 各タイマには、16ビット・リニア・プリスケーラ(1、2、3...65536)が組み込まれている

- 自動再ロード・レジスタでカウント周期を定義

- オーバーフロー／アンダーフローで更新イベント(割込みまたはDMA)を発行

- プリロード・レジスタからアクティブ・レジスタへの内容(プリスケーラ、周期、比較)の転送をトリガ

- 正確な周期変更(プリスケーラはオーバーフローでのみ更新)

- 比較レジスタ更新時のグリッチレス動作

- 一部のタイマでは、更新割込みの発行レートを繰り返しカウンタで調整可能(TIM1、TIM15-17)

- その他のタイマでは、カウンタが再ロードされるたびに更新イベントが発生

このスライドでは、タイマカウント周期の調整方法を説明します。

各タイマには、リニアクロックプリスケーラが組み込まれており、1 から 65536 までの任意の整数でクロックを分周できます。これにより、カウントペースを正確に調整できます。たとえば、APB クロックが 64 MHz の場合に 64 で分周すると、正確な 1 MHz のカウントレートが得られます。

自動再ロードレジスタでカウント周期が定義されます。ダウンカウントモードでは、カウンタがアンダーフローすると、自動的に周期値が再ロードされます。アップカウントモードでは、カウンタが自動再ロード値を超えると、ロールオーバーしてリセットされます。

カウンタがアンダーフローまたはオーバーフローして、新しい周期が開始されたときに、更新イベントが発行されます。これにより、タイマの周期に同期した割り込みや DMA リクエストのトリガとなり、リアルタイム制御に有効なタイマのパラメータを調整することができます。この更新イベントによって、複数のパラメータと、特に、クロックプリスケーラ、自動再ロード値、比較レジスタおよび PWM モードに対して、プリロードレジスタからアクティブレジスタへの転送がトリガされます。

16 ビットのプログラム可能な繰り返しカウンタによって、割込み発行レートをカウント周期から切り離して、たとえば、1 回目、2 回目、3 回目、そして最高で 256 回目の PWM 周期ごとに 1 回の割込みを得ることができます。これは、高い PWM 周波数を扱う際に特に役立ちます。STM32G0 マイクロコントローラに関しては、繰り返しカウンタはタイマ 1、タイマ 15、16、および 17 にのみ実装されています。

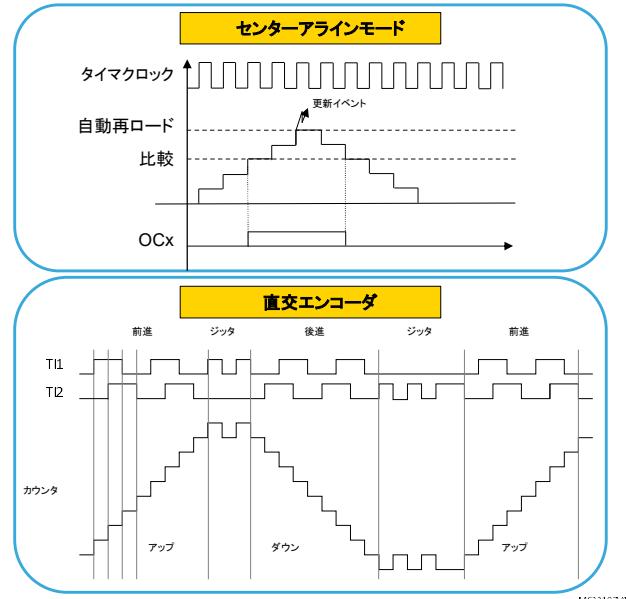

# カウントモード

8

## ・インクリメンタル／直交エンコーダとモータ駆動アプリケーションをサポート

- ・アップ／ダウン・カウント・モードをサポート

- ・TIM1、TIM2、および TIM3

- ・センター・アライン PWM の生成

- ・オーバーフローとアンダーフローで方向が変化

- ・電気モータの音響ノイズを低減

- ・直交エンコーダの組み込みサポート

- ・ロータリーエンコーダ／デジタルポテンショメータ

- ・位置センサ

- ・タイマの直接角度読出しが可能

STM32 タイマの一部(高機能制御タイマ 1 および汎用タイマ 2 および 3)は、アップ／ダウンカウントモードに対応しています。

カウント方向はソフトウェアでプログラムするか、センター・アライン PWM モードのタイマで自動管理することができます。このモードでは、カウンタのオーバーフローとアンダーフローでカウント方向が自動的に変化します。特定の PWM スイッチング周波数に対して、このモードを使用すると、有効電流リップル周波数を 2 倍にすることで音響ノイズが低減されるので、電力ステージのスイッチング損失とノイズの最適なトレードオフが得られます。

カウント方向は、タイマがエンコーダモードにあるときにも自動的に処理可能です。直交エンコーダは、通常、電気モータ内の高精度なロータ位置センシングや、デジタルポテンショメータのために使用されます。直交エンコーダセンサ(インクリメンタルエンコーダとも呼ばれる)の 2 つの出力から、タイマは、各アクティブエッジのクロックを抽出し、2 つの受信信号間の相対的な位相シフトに応じてカウント方向を調整します。タイマカウンタは、このようにモータまたはポテンショメータの角度位置を直接保持します。

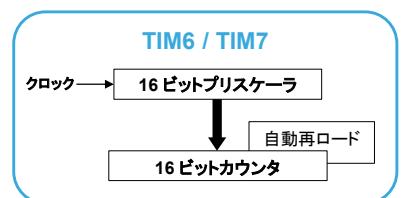

# 内部タイミング・リソースとしてのタイマ

9

## ソフトウェアとハードウェアのタイムベース用

- タイマは単純なタイムベースとして使用できる

- ソフトウェア管理用

- 他のペリフェラルに周期的トリガを与えるため

- ADC、DAC、その他のタイマ

- (カウンタオーバーフロー時の)更新イベントは割込みのトリガに使用できる

- 最もシンプルなオプションは、TIM6 と TIM7 の基本タイマ(出力なし)を使用する方法

- 汎用タイマ使用時のその他の手段

- 比較イベントを使用

- 1 周期当たり複数のイベントの生成が可能

- タイマのトリガ出力を使用

タイマの最も簡単なユースケースは、内部タイムベースの提供です。

これは、一般的に、周期的割込みの提供やシングルショットタイマアウト保護のために、ソフトウェアルーチンによって使用されます。タイマは、相互接続マトリックスを介して、ADC、DAC、その他のタイマなど、他のオンチップペリフェラルに周期的なトリガを与えることができます。

タイマからの更新イベント(通常はカウンタオーバーフロー時)は、ソフトウェアタイムベース割込みを発生させたり、周期的イベントをトリガしたりするための通常の手段です。基本タイマ TIM6 および TIM7 は、入出力チャネルのない最も単純なタイマ派生物であるため、このようなタスクに最適です。

他のタイマ、比較イベント、または他のタイマのトリガ出力を使用して、内部タイミングを生成することも可能です。複数の比較チャネルを使用して、1 つのタイマで複数のタイミングイベントを生成することができます。

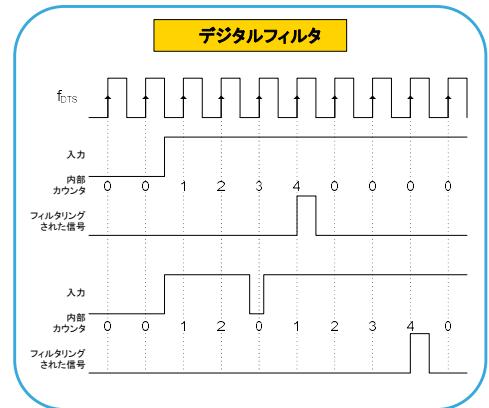

# 入力キャプチャ

10

## CPU オーバーヘッド低減のための信号の事前調整を含む

- 各チャネルは入力キャプチャとして個別に設定可能であり、次のような機能を備えている：

- 入力の再配置(1つの入力を2つのキャプチャチャネルに配置できる)

- プログラム可能なエッジ感度(立ち上がり/立ち下がり/両方)

- イベントプリスケーラ(1/2/4/8 イベントごとに1キャプチャ)

- デジタルフィルタ(デバウンスおよびノイズ除去用)

- キャプチャイベントによって、カウンタ値がキャプチャレジスタに転送され、割込みまたはDMAリクエストがトリガされる

- キャプチャレジスタが読み出されずに上書きされると、オーバーキャプチャフラグがセットされる

このスライドでは、入力キャプチャ機能について説明します。

各チャネルは入力キャプチャとして個別に設定可能であり、いくつかの信号調整オプションを備えています。1つの入力を2つのキャプチャチャネルに配置できます(通常は立ち下がリエッジキャプチャと立ち上がりエッジキャプチャを区別するため)。エッジ感度はプログラム可能であり、立ち上がりエッジ、立ち下がリエッジ、両エッジのいずれかとなります。イベントプリスケーラによって、2、4、8 イベントごとに1イベントのキャプチャが可能です。これにより、高周波信号を処理する際の CPU 負荷が軽減され、複数の入力信号周期にわたって測定が行われるため、測定精度が向上します。

ノイズやバウンスによるスプリアス遷移イベントは、プログラム可能なデジタルフィルタを使用して除去できます。この図は、フィルタ許可が 4 に設定された場合の信号のフィルタ方法を示しています。

上側のケースでは、内部カウンタ値を見れば分かるように、立ち上がりエッジから 4 サンプリング周期後に、きれいな立ち上がりエッジキャプチャがトリガされています。

下側のケースでは、グリッチのためにフィルタカウンタがリセットされ、ハイレベルの 4 サンプルが連続でカウントされた後に、キャプチャが発生しています。キャプチャトリガが発行されると、タイマのカウンタがキャプチャレジスタに転送され、割込みまたは DMA リクエストを発行できます。前回のキャプチャが読み出される前に新しいキャプチャが発生すると、キャプチャレジスタが上書きされ、必要に応じてソフトウェアがこの状態を管理するために、オーバーキャプチャフラグがセットされます。

# 高度なキャプチャオプション

11

## ソフトウェアオーバーヘッドのない直接測定

- クリア・オン・キャプチャモード

- このモードでは、キャプチャがトリガされると直ちにカウントをリセットできる

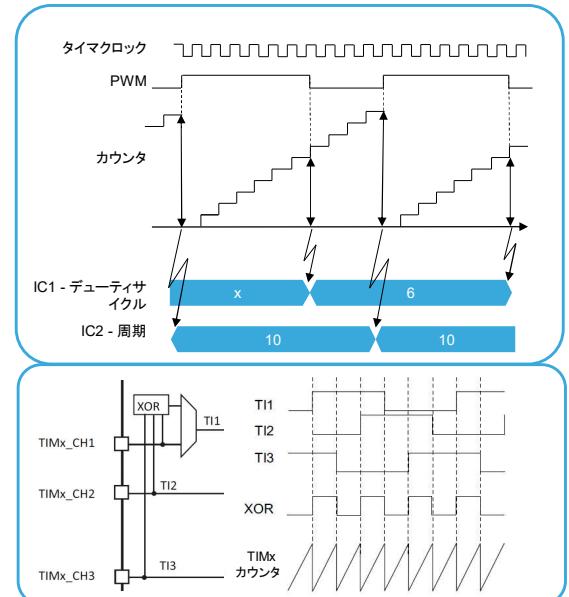

- PWM 入力モード

- タイマは、2つのキャプチャレジスタ内の信号の周期とパルス幅を直接キャプチャする

- XOR 機能付きクリア・オン・キャプチャモード

- 最大 3つの入力の任意のエッジ間のインターバルをキャプチャ可能

- 通常、電気モータのホールセンサに使用される

このスライドでは、より高度なキャプチャ関連の機能について説明します。クリア・オン・キャプチャモードでは、キャプチャがトリガされた直後にカウントがリセットされます。従来のフリーランニングカウンタでは、トリガに続く周期を得るために追加の計算が必要でしたが、これにより周期を直接測定することができます。

PWM 入力モードでは、タイマは入力された PWM 信号の周期とデューティサイクルの両方をキャプチャすることができます。入力信号は、内部で 2つのキャプチャチャネルにルーティングされます。信号の立ち上がりエッジは入力キャプチャ 2 でキャプチャされ、クリア・オン・キャプチャモードで周期値を提供します。

立ち下がりエッジはキャプチャ 1 チャネルでキャプチャされ、パルス長の持続時間を提供します。この場合、デューティサイクルは単純に、入力キャプチャ 1 と入力キャプチャ 2 の間の比率に相当します。

最後に、タイマには 3つの入力チャネルを XOR ロジックで結合する XOR 機能が含まれています。

これは通常、電気モータのホールセンサから得られる 3つの 120° 位相シフト信号を処理するために使用されます。これにより、3つの信号のすべてのエッジでクリアオンキャプチャが発生し、速度調整に直接使用できるキャプチャ値を得ることができます。

# 出力比較

12

## 単純な出力波形の場合、または周期の経過を表示する場合

### ・カウンタが比較レジスタ値に一致する場合:

- ・対応する出力ピンを次のようにプログラムできる:

- セット

- リセット

- トグル

- 変更しない

- ・割込みステータスレジスタにフラグがセットされる

- 対応するイネーブルビットがセットされている場合、割込みまたは DMA リクエストを生成する可能性がある

- ・比較レジスタは、プリロードレジスタの有無に関係なくプログラムできる

### ・プログラムされた出力モード(セット、リセット、トグル)もプリロードできる

- あるモードから別のモードへのグリッチのない移行が可能(通常は PWM から連続的にオンまたはオフ状態に移行)

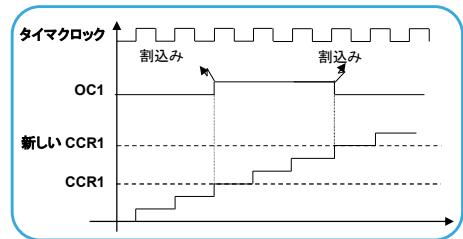

このスライドでは、出力比較機能について説明します。

カウンタが比較レジスタの値と一致した場合に、比較イベントが生成されます。このイベントは、割込みまたは DMA リクエストをトリガでき、出力セット、出力リセット、または出力トグルによって対応する出力ピンに反映できます。

比較レジスタはプリロードできます。カウント周期の間に複数の比較値を書き込む必要がある場合には、プリロードを無効にする必要があります。タイミング図では、プリロードは無効になっています。

逆に、リアルタイム制約のあるアプリケーションでは、プリロードモードの使用を優先する必要があります。これにより、ソフトウェアが比較レジスタを次の値に更新するのにより大きな時間マージンが得られるからです。プリロードからアクティブ値への転送は、カウンタがオーバーフローまたはアンダーフローしたときに更新イベントによってトリガされます。

また、出力比較モードをプリロードすることで、たとえば、PWM モードから強制オン／オフ状態へグリッチレスで移行することが可能です。

# ワンパルスモード

13

## 外部同期波形生成用

- トリガに応じてカウンタを開始しパルスを生成できる

- 長さはプログラム可能

- プログラム可能な遅延の後

- ソフトウェアでプログラム可能な 2 つの波形

- 単一パルス

- 繰り返しパルス

- 再トリガ可能オプション

- 新規トリガの場合はパルス幅が拡大

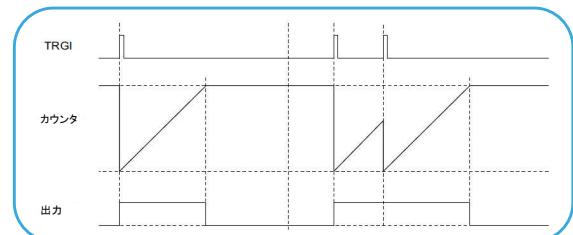

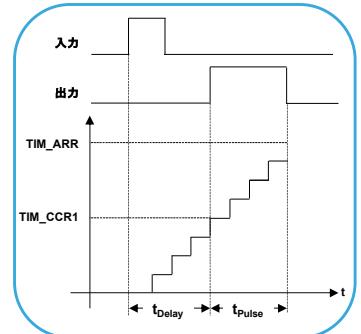

ワンパルスモードは、外部イベントに応じてプログラム可能な長さのパルスを生成するために使用されます。パルスは、入力トリガが到着し次第、またはプログラム可能な遅延の後に開始できます。比較 1 レジスタ(CCR1)の値によってパルス開始時間が定義され、自動再ロードレジスタ(ARR)の値によってパルスの終了が定義されます。したがって、有効パルス幅は、ARR と CCR1 のレジスタ値の差として定義されます。上のタイミング図を参照してください。トリガによって単一のパルスが生成されるように、または単一のトリガによって連続的なパルス列が開始されるように、波形をプログラムできます。

ワンパルスモードには、再トリガ可能なオプションも用意されています。このスライドの一番下のタイミング図は、このオプションについて説明しています。

パルスが終了する前に新しいトリガが到着すると、カウンタがリセットされ、それに応じてパルス幅が拡張されます。

STM32G0 マイクロコントローラでは、タイマ 1、2、3、15 のみが再トリガ可能なワンパルスモードをサポートしていることに注意してください。

# 各種の PWM モード

14

## 複数のアプリケーションに対応する各種の PWM モード

- 基本 PWM、エッジアラインまたはセンターライン

- 非対称センターライン PWM

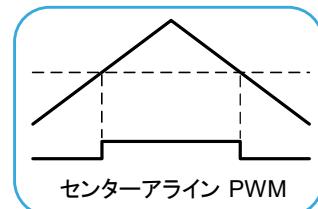

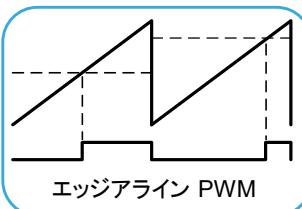

このスライドでは、PWM モードについて説明します。

標準エッジアライン PWM モードは、周期を定義する自動再ロードレジスタとデューティサイクルを定義する比較レジスタを用いてプログラムされ、カウンタはアップのみまたはダウンのみのカウントモードになっています。1 つのタイマで、個別のデューティサイクルと同一の周波数を持つ最大 6 つの PWM 信号を生成できます。

同じタイマによって複数の PWM 波形が生成される場合、すべての立ち下がりエッジが同時に発生します。そのため、エッジアラインと呼ばれます。

逆に、センターラインの PWM の立ち上がりエッジと立ち下がりエッジは、カウンタのロールオーバーと同期していないため、スイッチング時間はデューティサイクル値によって異なります。これは、カウンタをアップダウンモードでプログラミングすることによって実現されます。このモードが興味深いのは、同じタイマによって複数の PWM が生成されるときにスイッチングノイズを拡散するからです。

これは、電気モータ駆動用の 3 相 PWM 生成にとって重要な機能です。なぜならこれによって、特定のスイッチング周波数に対して電流リップルの周波数を 2 倍できるからです。たとえば、10 kHz の PWM によって、不可聴の 20 kHz の電流リップルが生成されます。これにより、PWM 周波数によるスイッチング損失を最小限に抑えつつ、PWM 動作の静音性が確保されます。

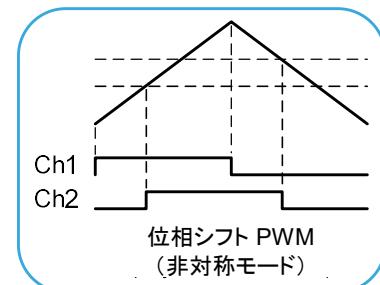

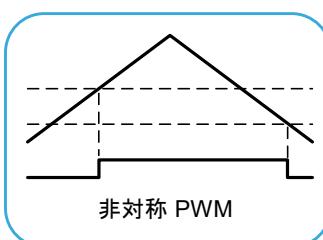

センターラインモードの変形として、非対称 PWM モードあります。このモードでは、2 つの比較レジスタによって PWM 信号のターンオンとターンオフが定義されます。これにより、ターンオン時間とターンオフ時間が個別に定義されるため、パルス幅設定の分解能が向上します。また、フルブリッジ位相シフトポロジに基づく DC/DC コンバータの駆動に必要となる位相シフト PWM 信号の生成も可能です。

この場合、タイマは、同一の周波数、50% のデューティサイクル、および 0 から 180° まで変化する位相シフトを持つ 2 つの PWM 信号を提供します。

# その他の PWM モード

15

## PWM 機能を拡張し、外部グルーロジックを回避

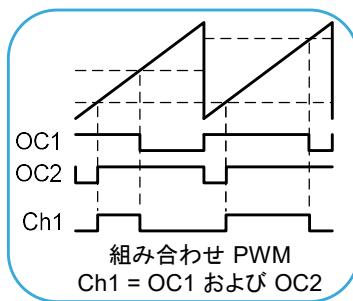

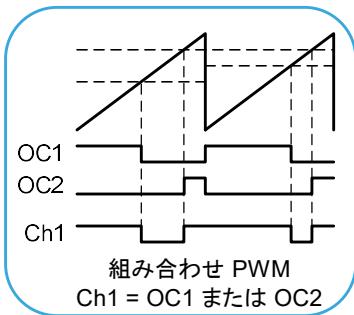

- 組み合わせ PWM モード

- 2 つのチャネルを OR または AND 関数で結合し、より複雑な波形を実現

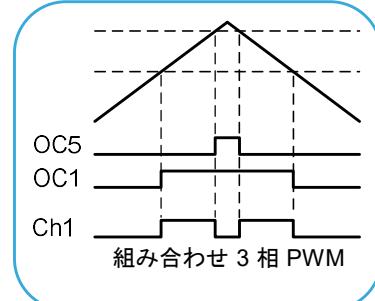

- 組み合わせ 3 相モード

- 4 番目の PWM をレギュラの 3 相 PWM と組み合わせて、ゼロベクタの挿入を可能にする

このスライドでは、組み合わせ PWM モードについて説明します。

このモードでは、隣接するチャネル（出力比較 1 と 2 または出力比較 3 と 4）によって 2 つの PWM 信号の論理結合を生成することができます。

PWM の論理和または論理積を取って複雑な波形を作成できます。通常、これにより、任意のパルス幅と任意の位相関係値を持つ 2 つの周期的なパルスを生成できます。

組み合わせ 3 相モードは、特に 3 相モータ制御アプリケーションを対象としています。この場合、タイマのチャネル 5 を 3 つのチャネル（1、2、3）のいずれかと組み合わせて、センターパターンの PWM 信号の途中にロー状態を挿入することができます。このモードでは、通常ゼロベクタ挿入と呼ばれる手法を使用することで、3 相モータ制御用の低コストの電流検出手法の実装が大幅に簡素化されます。

# 高度な PWM モード

16

## 外部制御を必要とする PWM 信号用

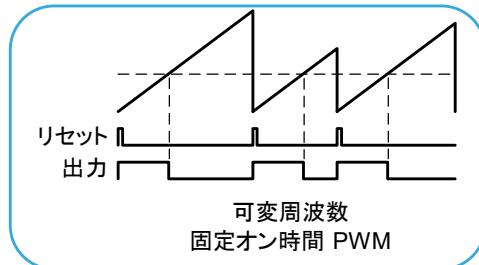

- 可変周波数 PWM

- 外部信号により駆動

- サイクルごとに制御されたデューティサイクル

- 電流ループでは、コンパレータまたは外部ピンにより駆動

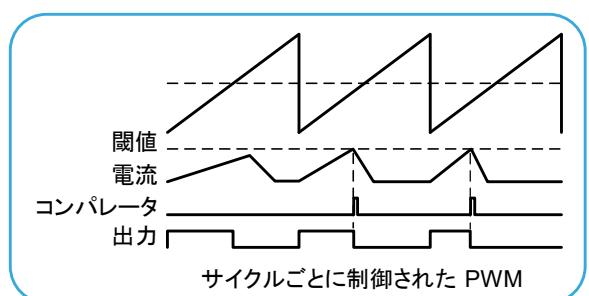

このスライドでは、周波数またはデューティサイクルを外部信号で駆動することができる、より具体的な PWM モードについて説明します。

タイマは、ETR、あるいはチャネル 1 または 2 の入力に接続された外部リセット信号を使用して、可変周波数信号を提供できます。このモードの目的は、固定されたオンまたはオフ時間と、ハードウェアによって制御される連続的に調整された周波数を持つ信号を提供することです。タイマは、比較レジスタを使用してオン(またはオフ)時間の制御を行います。一方、自動再ロードレジスタは、外部リセットがない場合でも PWM が停止しないことを保証し、これによって境界条件での安全な制御が実現されます。この手法は、主電源アプリケーション用の遷移モード PFC(力率コントローラ)や電流制御のデジタル LED 照明など、さまざまな用途に使用されます。タイマのもう 1 つのモードは、オンチップコンパレータまたはオフチップ信号のいずれかを使用して、ハードウェアによってデューティサイクルを制御するモードです。PWM は固定周波数で動作し、最大デューティサイクルは、比較レジスタとサイクルごとに制御される実際の値によって設定されます。これは電流制御の PWM を必要とするアプリケーションに使用され、通常は DC モータやソレノイドの駆動に使用されます。この場合、コンパレータは負荷へのピーク電流値を監視します。電流がプログラムされた閾値を超えるとすぐに、コンパレータは PWM 出力をリセットし、次の PWM 周期に自動的に再起動され、制御されたピーク電流値を提供します。

# タイマのカスケード 1/2

17

## スケーラブルな設計で高い柔軟性を実現

- トリガコントローラは、マスタ／スレーブ設定で複数のタイマをカスケードできる

- スレーブ: トリガコントローラは TRGI で入力を収集

- 外部トリガピン(ETR)から

- ITRx の他のオンチップリソースから

- 通常は他のタイマからの TRGO 出力

- マスタ: 内部タイマ信号を TRGO に送信

- 接続は相互接続マトリックスで行われる

- カスケード設定では特定のタイマがスレーブモードとマスタモードで同時に動作可能

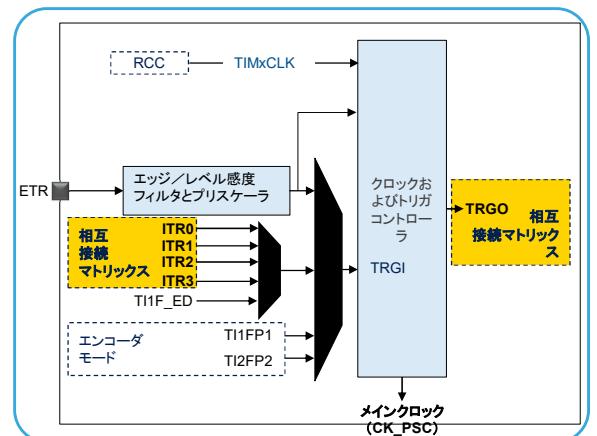

このスライドでは、タイマの同期機能について説明します。

トリガコントローラは、マスタ／スレーブ設定で複数のタイマをカスケードすることができます。タイマは、マスタタイマとして 1 つ以上のタイマを制御したり、スレーブとして他のタイマによって制御されたりすることができます。クロックおよびトリガコントローラは、タイマ間のリンクとして機能します。マスタモードでは、複数の内部制御信号を、そのタイマの外部のオンチップ TRGO トリガ出力にリダイレクトできます。スレーブモードでは、外部トリガピン(ETR)または他の TRGO 出力に接続されている 4 つの内部トリガ入力(ITR1～ITR4)の 1 つから来る TRGI(メイントリガ入力)で複数の入力を収集します。さらに、入力キャプチャ 1 と 2 のピンは、内部トリガとして使用することもできます(通常はカウンタをリセットするため)。

スレーブモードとマスタモードは、個別にプログラムすることができます。そのため、カスケード設定では特定のタイマがスレーブモードとマスタモードで同時に動作することができ、入力トリガを受けながら出力トリガを提供することができます。

マスタ同期とスレーブ同期は、タイマユニット内で個別にインスタンス化されます。すべての STM32G0 タイマの機能をまとめた、このプレゼンテーションの最後の表を参照してください。

# タイマのカスケード 2/2

18

## タイマ間で複数の信号を共有可能

- ・マスタモード:タイマは内部信号を TRGO 出力に伝播

- ・カウンタリセット、カウンタイネーブル、更新イベント、または OC1 比較一致

- ・OC1～OC6 で生成された波形のいずれか

- ・スレーブモード:タイマは TRGI 入力で制御される

- ・トリガモード:カウンタの開始が制御される

- ・リセットモード:TRGI の立ち上がりエッジでカウンタが再初期化される

- ・リセットモードとトリガモードの組み合わせ(再トリガ可能なワンパルスモード用)

- ・ゲートモード: カウンタの開始と停止の両方が制御される

- ・クロックに関連するその他のモード:

- ・3 つのエンコーダモード

- ・外部クロック

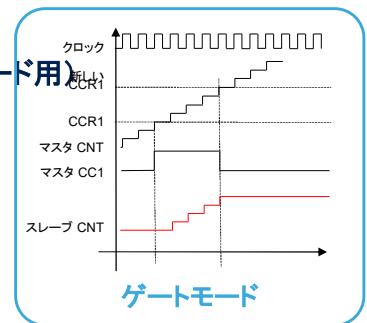

このスライドでは、さまざまな動作モードとタイマ間でやり取りされる信号を示しています。

マスタモードでは、TRGO 出力に送信されるトリガを選択するために 16 のオプションが与えられています。出力は、カウンタリセット時に発行される単一の同期パルス、カウンタ開始に対応するカウンタイネーブル、更新イベント、または比較 1 一致イベントのいずれかとなります。あるいは、TRGO 出力は、PWM 信号を含む生成された 6 つの波形のいずれかを他のタイマモジュールに送信することができます(チャネル 1～6 で比較し、すべてのチャネルのパルスを比較します)。

スレーブモードでは、タイマの動作モードは TRGI 入力によって制御されます。トリガモードでは、カウンタの開始が外部から制御されます。このモードは、複数のタイマを同時に開始する場合に使用します。リセットモードでは、カウンタは、通常、可変周波数 PWM 動作のために、TRGI 入力の立ち上がりエッジによってリセットされますリセットとトリガを含む組み合わせモードは、再トリガ可能なワンパルスモードの生成に使用できます。図に示すゲートモードでは、入力信号のレベルがハイのときにのみカウンタがアクティブになります。この信号は、入力または相互接続マトリックスから得られます。この場合、リセット、イネーブル、更新、比較一致の際に発行された同期パルスは使用できません。

最後に、スレーブモードの選択には、直交エンコーダデコーディングモードや外部クロック供給モードなどのクロック関係のモードが含まれます。

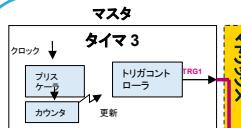

# 同期動作の例

19

## 複数のタイマを組み合わせて高い柔軟性を実現

- ・ タイマの同時開始

- ・ サイクル精度の高い同期

- ・ カスケード 48 ビットカウンタ

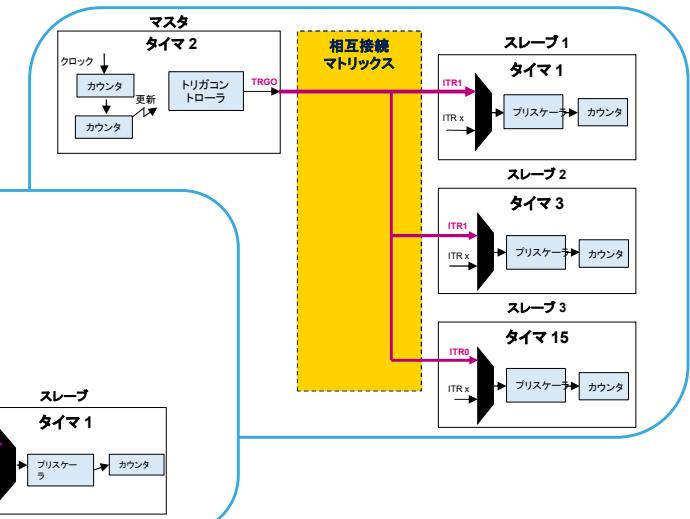

このスライドでは、同期動作の例を 2 つ示します。

1 つ目の例は、4 つのタイマを同時に開始する方法を示しています。マスター／スレーブリンクの遅延を補正するためにマスタタイマを少し遅らせて開始し、すべてのタイマをサイクル精度で同期させることができます。メカニズムは図のとおりで、タイマ 2、1、3、15 のチャネルを組み合わせることで、最大 16 個の PWM チャネルを同期させることができます。

2 つ目の例は、3 つのタイマをカスケード接続して 48 ビットタイマを作成する方法を示しています。ここでは、カウンタのロールオーバー時に生成される更新イベントを後続のスレーブタイマの入力クロックとして使用し、タイマ 3 のカウンタは最下位の 16 ビットを保持し、タイマ 15 のカウンタは中位のビット(ビット 16~31)を保持し、タイマ 1 のカウンタは上位のビット(ビット 32~47)を保持するようにしました。

## STM32 タイマはモータ駆動のあらゆる側面をカバー

- PWM の生成

- センターラインモードと組み合わせ 3 相モード

- デッドタイム挿入

- 6 ステップモード

- 保護(デュアルブレーキ緊急停止機構)

- 速度と位置のセンシング

- エンコーダ、ホールセンサ、およびタコメータジェネレータ専用モード

- ADC トリガ

このスライドは、タイマの 4 つの主な電気モータ制御機能をまとめたものです。

- タイマには、電源スイッチ制御専用の PWM モードが含まれています。上記のセンターライン PWM と組み合わせ 3 相 PWM に加えて、タイマは、相補 PWM 生成のためのデッドタイム挿入と、ブリッジレス DC モータ駆動用の 6 ステップモードを備えています。

- これには、障害発生時にハードウェアによって PWM 出力を無効にするデュアルレベルの緊急停止メカニズムを備えた電力ステージ保護回路が搭載されています。

- モータ制御システムで見られる最も一般的なセンサを扱うことができます直交エンコーダとホールセンサは粗密な位置フィードバックに使用されます。一方、タコメータジェネレータはコスト効率の良い速度フィードバックに使用され、クリア・オン・キャプチャモードのみが必要です。

- 最後に、タイマには同期 ADC トリガオプションが含まれています。これは、電圧と電流のセンシングを適切に管理し、電力ステージのスイッチングノイズによる取得の問題を回避するために必要です。

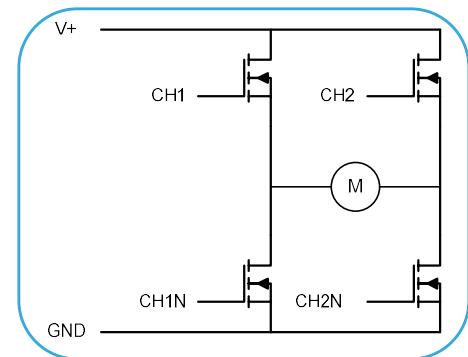

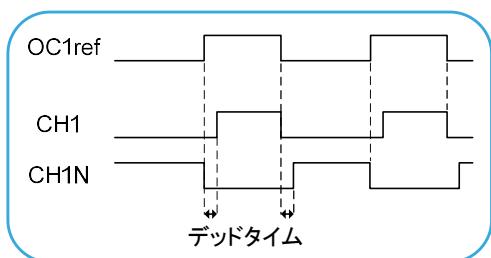

# デッドタイム挿入

21

## タイマあたり最大 3 つのハーフブリッジコンバータを直接駆動

- ハードウェア・デッド・タイム・ユニットは、重複のない相補的な PWM 信号を生成する

- 機能安全のためにデッドタイムレジスタをロック(読み出し専用)可能

- ハーフブリッジコンバータとフルブリッジコンバータのクロスコンダクションを防止

- DC/DC コンバータ、DC モータ、3 相ブラシレスモータ

フルブリッジ DC モータ駆動

このスライドでは、デッドタイム挿入機能について説明します。ハードウェアデッドタイムジェネレータは、基準 PWM 信号から 2 つの重複のない相補的な PWM を提供します。STM32 タイマには、OC1、OC2、OC3 チャネル用の最大 3 つのデッドタイムジェネレータが組み込まれています。デッドタイムの持続時間は 8 ビット値でプログラムされます。実行時にこの重要な値が破損するのを防ぐために、ユーザはこの値をロックできます。これを行うには、次の MCU リセットまでデッドタイムレジスタを読み出し専用モードに切り替える 1 回のみ書き込みロックビットをセットします。

デッドタイム挿入は、ハーフブリッジを駆動する場合に必要になります。ハーフブリッジでは、2 つの電源レールの間にトランジスタのペアが直列に接続されます。この場合、物理的なスイッチング特性を考慮して、一方のスイッチがオンになる前に少しの時間を挿入してもう一方のスイッチをオフにできるようにする必要があります。ハーフブリッジは通常、ここに示すフルブリッジトポロジを使用する DC またはステッピングモータ駆動用の DC/DC コンバータ、または 3 つの PWM ペアを備えた 3 相インバータに見られます。

# 6ステップ/ブロック転流

22

## ブラシレスDC(BLDC)モータ駆動用のCPUの負荷軽減

- 1つのタイマでホールセンサのフィードバックを処理し、同期PWM生成用の高度なタイマをトリガできる

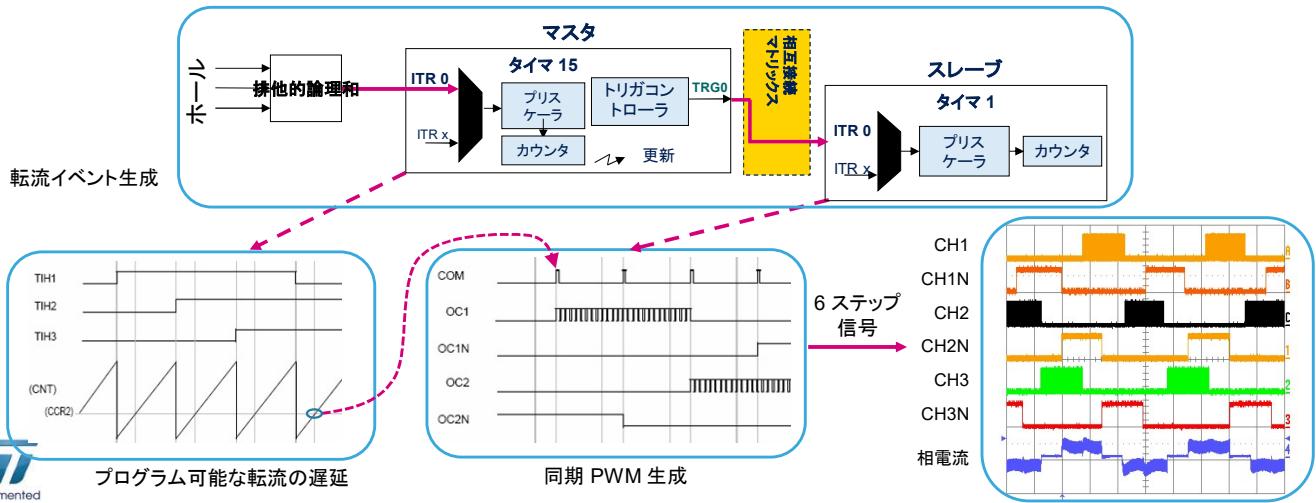

このスライドでは、STM32タイマを使用して6ステップ駆動(ブロック転流とも呼ばれる)を管理する方法について説明します。

これは、2つのタイマをチェーンすることで構成されます。1つは3つのホールセンサ信号を処理し、もう1つはロータの角度位置と同期したPWM生成を管理し、6つの連続するステップを生成します。

1つ目のタイマは、3つの入力によってトリガされるクリアオンキャプチャモードで動作します。比較レジスタ(ここでは比較2)は、元の角度位置と転流時間の間にプログラム可能な遅延を追加する役割を果たします。キャプチャレジスタ1は、連続するホールセンサエッジ間のタイミング間隔を保持し、速度調整ループに必要です。

比較2一致イベントは、TRGO出力を介してスレーブタイマに伝播されます。これらのイベントは転流イベントとして機能し、PWM生成の変化をトリガします。シーケンスの6つのステップのそれぞれについて、6つの出力の状態は、強制的にアクティブまたは非アクティブになるか、PWM信号を生成するように定義されます。あるステップから別のステップへの遷移は、転流割込みルーチンでソフトウェアによってプリロードされ、次の転流が到着したときに出力動作モードを再プログラムするためにハードウェアによって自動的に転送されます。

右の図は、2つの連続した完全な6ステップシーケンスの6つのPWM信号と、モータ相の1つの電流を示しています。

## クラス最高の保護スキーム

- ブレークイベントが PWM 出力を無効にする

- ハードウェアにより(最小遅延時間)

- 非同期(クロックレス動作、クロック関連の遅延なし)

- プログラム可能な安全状態(ハイ/ローまたはハイインピーダンス)

- 相補的な出力を持つタイマで使用可能

- タイマ 1 および 15

- タイマ 1 に 2 つのブレークチャネルを実装

- デュアルレベルの保護スキームが可能

- すべての出力がOFF、または一部の出力が強制ONで一部の出力がOFF

- デッドタイム挿入によりシートスルーのリスクがないことを保証

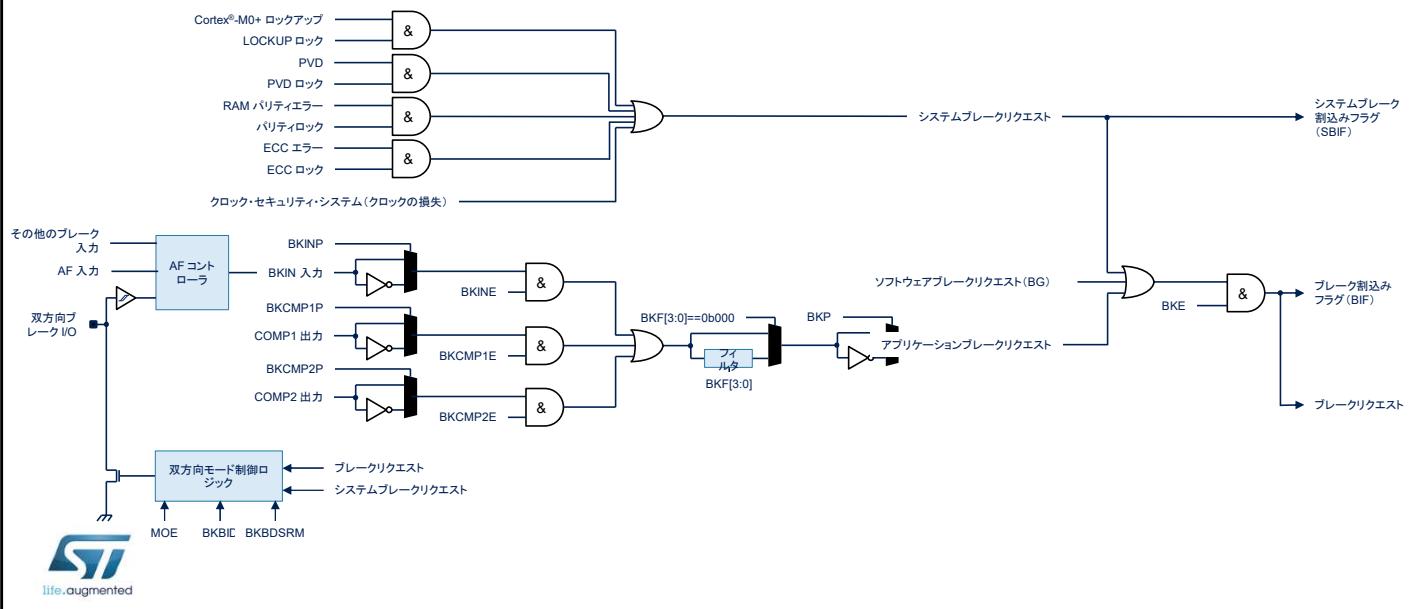

このスライドでは、ブレーク機能について説明します。

ブレークイベントが発生すると、PWM 出力を自動的に無効にするハードウェア保護メカニズムがトリガされ、PWM 出力が強制的にユーザが設定可能な状態(ハイレベルまたはローレベルでのローインピーダンス、あるいはハイインピーダンス)になります。

論理回路は、クロックを使用せずに非同期的に動作します。

これにより、システムクロックに障害が発生した場合でも機能が保証され、保護を遅らせる傾向のあるクロック関連の伝播時間が回避されます。

この機能は、電力変換タスクを実行できる相補的な PWM 出力を備えたすべてのタイマで使用できます(タイマ 1 および 15)。

タイマ 1 には 2 つの個別のブレークチャネルがあり、タイマ 15 は独自のブレークチャネルをサポートしています。

2 つのブレークチャネルをサポートすることで、デュアルレベルの保護スキームが実現されます。たとえば、すべてのスイッチがオフの優先度の低い保護を、ローサイドスイッチがアクティブの優先度の高い保護で上書きすることができます。

さらに、フォールトモードに入る直前にデッドタイム遅延を挿入して、電力ステージを安全に無効にすることができます。これにより、潜在的なシートスルー状態が防止されます。たとえば、ハイサイド PWM がオンのときに障害が発生するとします。一方、安全状態は、ハイサイドスイッチをオフにしてローサイドをオンにするようにプログラムされているとします。障害が発生すると、システムはまずハイサイド PWM を無効にしてから、ローサイドをスイッチをオンする前にデッドタイムを挿入します。

# ブレーキ機能 2/4

24

## 複数の緊急停止入力ソース(BRK 入力)

このスライドでは、ブレーキ機能について説明します。BRK2 は表示されません。

複数のブレーキソースを組み合わせて、ブレーキイベントをトリガできます。

システムブレーキリクエストは、マイクロコントローラで重大なエラー (CPU ロックアップ、電源電圧低下、RAM パリティエラー、フラッシュ ECC エラー、クロックの損失) が検出された場合に発生します。

ロック信号は、SYSCFG ペリフェラルにある 1 回のみ書き込みイネーブル ビットです。デフォルトでリセットされます (フォールトエラーはマスクされます)。一度設定 (障害検出が有効化) されると、機能安全のためにマイクロコントローラ全体がリセットされない限り、リセットできません。

アプリケーションブレーキリクエストは、ボードの障害に起因します。

マイクロコントローラのピンアウトにあるオルタネート機能コントローラで、ブレーキ入力を選択することもできます。

ブレーキ検出ユニットに移行する前に外部ソースを調整することができます。これにより、適切な極性を選択し、デジタルフィルタを使用してスプリアスグリッチを破棄できます。

通常、回復不可能なエラー状態を診断する際に、ソフトウェアでブレーキをリクエストすることも可能です。

これらのブレーキリクエストのいずれかが発生すると、割込みまたは DMA リクエストがアサートされます。

## ブレーク機能 3/4

25

- ブレーク入力は双方向になり、外部障害イベントを受け入れたり、マイクロコントローラの外部の内部障害イベントを知らせたりするようになった

- この機能により、次のことが可能になる。

- 外部のマイクロコントローラやゲートドライバが入力をシャットダウンするためのグローバルなブレーク情報を、1 本のピンで利用することができる

- 複数の内部および外部ブレーク入力を統合する必要がある場合に、内部コンパレータと複数の外部オープンドレインコンパレータ出力はまとめて論理和が取られ、ブレークイベントをトリガする

- すべての内部フォールトソース(システム、コンパレータ)を、単一の信号に統合

STM32G0 は、双方向ブレークと呼ばれる新機能を実装しています。

ブレーク I/O パッドはボードレベルの障害を報告するために使用されますが、マイクロコントローラの内部の障害を知らせるための出力としても使用できます。

双方向モードは、ブレークとブレーク 2 入力の両方で使用でき、I/O をアクティブロー極性でオープンドレインモードに設定する必要があります。

したがって、STM32G0 内で検出されたグローバルブレーク情報は、他の CPU またはゲートドライバに出力できます。

複数の内部および外部ブレークソースを統合する必要がある場合、内部ブレークソースと複数の外部オープンドレインコンパレータ出力はまとめて論理和が取られ、ユニークなブレークイベントをトリガします。

# ブレーク機能 4/4

26

## ブレーク解除のメカニズム

- ブレーク入力は、ビット BKxBID が 1 にセットされている場合、双方向モードに設定される

- 安全なブレーク解除メカニズムは、システムが完全にロックされることを防ぐ

- ブレーク入力でレベルがローになると、同じ入力でレベルをローに強制するブレークがトリガされる

- ビット BKxDSRM が 1 にセットされると、ブレーク出力が解放され、障害信号をクリアしてシステムを再設定できる

| MOE | BKxDIR | BKxDSRM<br>(DiSaRMed) | 状態              |

|-----|--------|-----------------------|-----------------|

| 0   | 0      | X                     | 設定 (BKIN は入力信号) |

| 0   | 1      | 0                     | 設定 (BKIN は双方向)  |

| 0   | 1      | 1                     | 解除              |

| 1   | X      | X                     | 設定              |

このスライドでは、ブレーク回路を設定および解除する方法について説明します。BKxBID ビットがセットされているときは双方向モードがアクティブになります。X は BK または BK2 ブレーク信号を意味します。

ブレーク IO パッドは双方向性なので、ブレーク入力でレベルがローになると、同じパッドでレベルをローに強制するブレークがトリガされます。そのため、ブレーク状態を解除するには、ブレーク解除のメカニズムが必要です。

メイン出力イネーブル(MOE)ビットは、チャネルが出力として設定されている場合に関連します。このビットは、ブレーク入力の 1 つがアクティブになると、ハードウェアによって非同期にクリアされ、OC および OCN 出力を無効にします。

ブレークイベント後に保護を再び設定するには、次のシーケンスを使用する必要があります。

- BKDSRM(BK2DSRM)ビットをセットして、出力制御を解放する必要があります。

- ソフトウェアは、システムブレーク条件(ある場合)がなくなるまで待ってから、SBIF ステータスフラグをクリアする必要があります(または再設定の前にシステムでクリアします)。

- ソフトウェアは、BKDSRM(BK2DSRM)をハードウェアによってクリアされるまでポーリングする必要があります(アプリケーションブレーク条件がなくなるとき)。

この時点から、ブレーク回路は設定されアクティブになり、MOE ビットをセットして、PWM 出力を再び有効にできます。

## ADC トリガの複数のオプション

- ADC トリガは、タイマイイベントによって生成可能

| ソース        |

|------------|

| TIM1_TRGO2 |

| TIM1_CC4   |

| TIM2_TRGO  |

| TIM3_TRGO  |

| TIM15_TRGO |

| TIM6_TRGO  |

- タイマ 1 の TRGO2 出力は ADC 専用

- 16 個の使用可能なトリガソース

- PWM 周期ごとにデュアル ADC トリガが可能

- TRGO は同期目的のために空いたまま

このスライドでは、タイマに関連する ADC トリガオプションについて説明します。

ADC は、表に示すように、ほとんどの STM32 タイマでトリガすることができます。

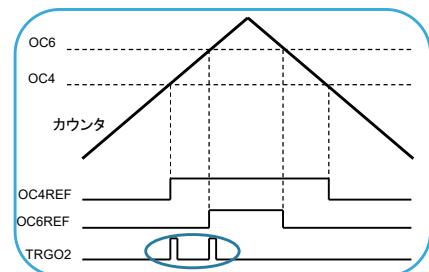

これは、比較イベントを使用して実行できます。ADC 変換は、特定の比較一致で開始されます。これは、タイマ 1 のチャネル 4 に適用されます。TRGO イベントは、特定のタイマでも使用できます。これにより柔軟性が高くなります。なぜなら、TRGO は、レジスタ更新、カウンタリセット、トリガ入力などの比較イベントまたはタイマ内部制御信号のいずれかになる可能性があるからです。一方で、これは TRGO が同期目的で使用されることを防ぎます。

このため、タイマ 1 には、ADC トリガ専用の TRGO2 出力も追加されています。

TRGO2 は、図に示すように、比較 4 と 6 のイベント、または比較 5 と 6 のイベントを組み合わせることにより、6 つの比較イベントと PWM 周期ごとにデュアルトリガを持つ可能性を含む 16 の可能性を提供します。これにより、TRGO は複数のタイマ同期スキームのために空いたままになります。

# ADC 同期の例

28

## ADC 読出し中に PWM 関連ノイズを回避

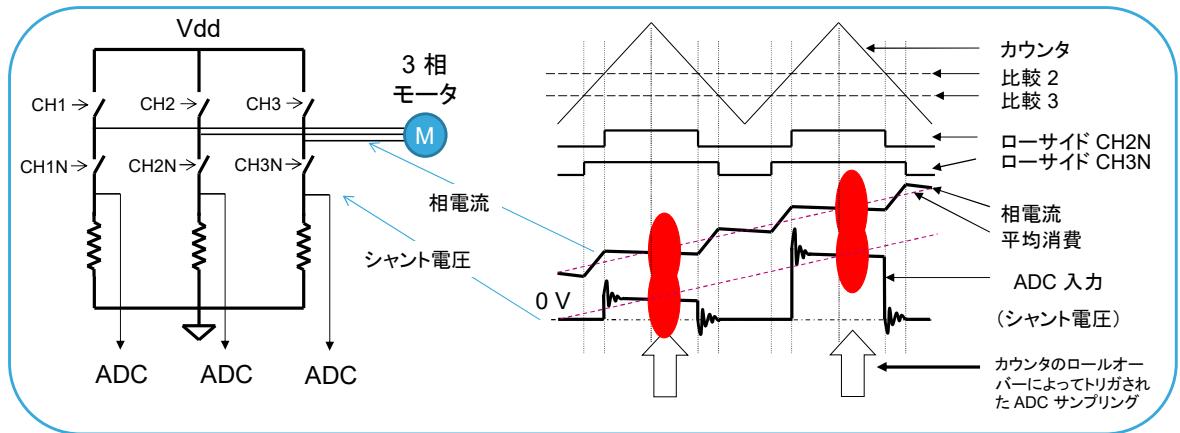

- 3 相モータ制御アプリケーションでは、カウンタオーバーフロー時の ADC トリガにより、平均電流値を取得でき、ノイズの多い ADC 変換が回避される

このスライドでは、PWM 同期 ADC トリガの例について説明します。3 相モータ制御では、電力ステージを制御するために生成される PWM と ADC の読出し値を同期させる必要があります。これにより、電流波形のリップルから平均値を抽出でき、電源スイッチに起因するリングングから十分に離れた位置で ADC の読出しが行われるようになります。ここで左側に示されているのは、3 相モータインバータです。6 つのスイッチは、デッドタイムが挿入された 3 つの相補的な PWM ペアによって制御され、モータ巻線の電流は、3 つのハーフブリッジの下側に配置されたシャント抵抗を使用して測定されます。右側には、タイマのカウンタ、比較 1 と比較 2 の値、および CH1N と CH2N によって制御されるローサイドスイッチに対応する PWM 出力が示されています。下の 2 つの波形は、モータ相の電流と、シャント抵抗に対して得られたこの電流のイメージを表しています。この低成本のトポロジーでは、ローサイドスイッチがオンの場合にのみ電圧を測定できます。ADC 入力に対して得られる信号が方形波状になるのはこのためです。この場合、ADC トリガはカウンタのロールオーバー時に生成されます。これにより、周期の途中で正確に読出しを行い、リップルの大きい信号の平均値を取得できます。さらに、PWM 同期 ADC トリガを使用することで、シャント電圧に存在するリングングノイズから離れた位置で ADC 変換が行われることが保証されます。

# 割込みと DMA

29

| イベント                                                                             | 割込み | DMA | 説明                                                                           |

|----------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------------------------|

| 更新                                                                               | はい  | はい  | カウンタがオーバーフローまたはアンダーフローした場合、あるいは強制的なソフトウェアの更新リクエストが発生した場合に発行                  |

| キャプチャ／比較 1<br>キャプチャ／比較 2<br>キャプチャ／比較 3<br>キャプチャ／比較 4<br>キャプチャ／比較 5<br>キャプチャ／比較 6 | はい  | はい  | 比較一致時またはキャプチャがトリガされた場合に発行<br>➢ 各キャプチャ／比較チャネルには、独自の割込みと DMA イネーブルビットおよびフラグがある |

| トリガ                                                                              | はい  | はい  | トリガイベント時に発行(内部トリガ入力 ITRx、TI1 エッジ検出回路、フィルタリングされた TI1/TI2 または外部トリガ入力ピンから)      |

| 転流                                                                               | はい  | はい  | タイマ 1 およびタイマ 15、16、17 のみ                                                     |

| ブレーク                                                                             | はい  | 不可  |                                                                              |

このスライドには、割込みと DMA リクエストのソースが一覧表示されています。

ほとんどのイベントは、割込みまたは DMA リクエストを生成でき、2 つを同時に生成することも可能です。カウンタがオーバーフローまたはアンダーフローすると、更新が発行されます。これは主に、PWM 周期の開始時にタイマの実行時設定をリフレッシュし、次のレジスタ更新までの間隔を最大化するために使用されます。繰り返しカウンタを使用すると、いくつかの PWM 周期をスキップして、高い PWM 周波数での割込みまたは DMA リクエストの数を減らすことができます。

6 つのキャプチャ／比較イベントにはそれぞれ独自の割込みと DMA があります。TRGI 入力時のトリガイベントも(トリガソースに関係なく)、割込みまたは DMA リクエストをトリガできます。最後に、割込みと DMA リクエストのその他のソースとして、タイマ 1、15、16、17 の転流イベントとブレークイベントがあります。

# DMA バーストモード

30

## 動作中のタイマ再設定が可能

- 1 回の DMA イベントで複数のレジスタの更新が可能

- DMA の効率的な使用(1 回のバーストが必要)

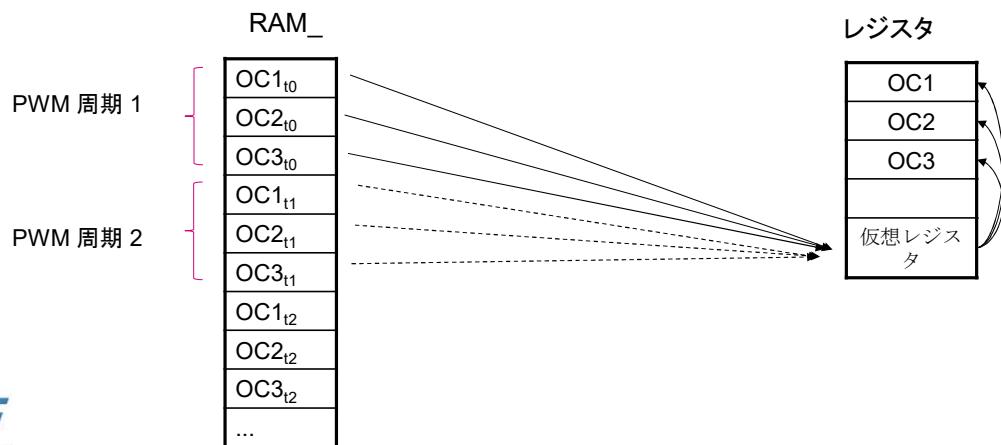

タイマには、1 回の DMA ストリームで複数のレジスタを再プログラムする DMA バーストモードが含まれています。これにより、複数の実行時パラメータを同時に変更したり(たとえば、複数のチャネルのデューティサイクルや周波数)、設定レジスタに書き込むことでタイマ設定を動的に変更したりできます。

この例では、新しい PWM 周期開始時に、3 つの比較値を含むテーブルを 1 回の DMA バーストで比較レジスタに転送する方法を示しています。

DMA は、タイマ内のユニークな場所(仮想レジスタ TIMx\_DMAR)を指して、"メモリからペリフェラル" モードでプログラムする必要があります。更新イベントが発生すると、タイマはプログラムされたバースト長に対応する回数の DMA リクエストを送信します。その後、各値は、仮想レジスタから対象となるアクティブなレジスタに自動的にリダイレクトされます。

次の更新イベントでは、3 つの新しい比較値が再度転送されます。この例では、通常であればこのような更新スキームで必

要となる 2 つの DMA ストリームが、このメカニズムにより節約されています。

# 低消費電力モード

31

| モード                | 説明                                               |

|--------------------|--------------------------------------------------|

| <b>RUN</b>         | アクティブ                                            |

| <b>SLEEP</b>       | アクティブ<br>▶ ペリフェラル割込みによりデバイスが SLEEP モードを終了する      |

| <b>低消費電力 RUN</b>   | アクティブ                                            |

| <b>低消費電力 SLEEP</b> | アクティブ<br>▶ ペリフェラル割込みによりデバイスが低消費電力 SLEEP モードを終了する |

| <b>STOP 0/1</b>    | 停止<br>▶ ペリフェラルレジスタの内容は保持される                      |

| <b>STANDBY</b>     | パワーダウン<br>▶ ペリフェラルは、STANDBY モード終了後に再初期化する必要がある   |

| <b>SHUTDOWN</b>    | パワーダウン<br>▶ ペリフェラルは、SHUTDOWN モード終了後に再初期化する必要がある  |

この表は、現在のマイクロコントローラの電力に応じた汎用タイマ(GPT)の状態を示しています。

RUN モード、低消費電力 RUN モード、SLEEP モード、および低消費電力 SLEEP モードでは、汎用タイマはアクティブです。SLEEP モードと低消費電力 SLEEP モードでは、GPT 割込みによりデバイスはそれぞれ SLEEP モードと低消費電力 SLEEP モードを終了します。

STOP 0 モードと STOP 1 モードでは、汎用タイマは停止します。ペリフェラルレジスタの内容は保持されます。これらのモードを終了する際には、GPT の再設定は必要ありません。

STANDBY モードと SHUTDOWN モードでは、汎用タイマはパワーダウンしているため、これらのモードを終了する際に再初期化する必要があります。

低消費電力の使用例向けに、LPTIMER は、STOP 0 モードと STOP 1 モードでのフル動作やウェイクアップ機能などの拡張機能を備えていることに注意してください。

## ・電力変換アプリケーションの安全なデバッグが可能

- ・ タイマごとに、DBGMCU モジュールの DBG\_TIMx\_STOP 設定ビットによって、マイクロコントローラがデバッグモードに移行(Cortex®-M0+ コアが停止)したときのタイマの動作を設定することができる

- DBG\_TIMx\_STOP = 0

- TIMx カウンタの動作を維持

- DBG\_TIMx\_STOP = 1

- コアの停止時にカウンタのクロックを停止

- 相補的な出力を持つタイマの場合、出力は無効になる

デバッグモードでのタイマの状態は、1 つのタイマにつき 1 つの設定ビットで設定することができます。

- デバッグビットがリセットされている場合、ブレークポイントの間、タイマクロックが維持されます。

- デバッグビットがセットされている場合、コアが停止するとすぐにタイマのカウンタが停止します。さらに、相補的な出力を持つタイマの出力は無効になり、強制的に非アクティブ状態になります。この機能は、タイマが電源スイッチや電気モータを制御しているアプリケーションに非常に役立ちます。これにより、過電流によって電力ステージが損傷したり、ブレークポイント到達時にモータが制御不能の状態になるのを防ぎます。

- PWM 周波数セットアップ

- 自動再ロード(TIMx\_ARR の ARR)とクロックプリスケーラ(TIMx\_PSC の PSC)で定義:

- 実際には、PSC = 0 (プリスケーラなし)で始める必要がある:

- 16 ビット(または 32 ビット)の範囲を超える値が得られる場合は、ARR が適合するまで PSC を増やす必要がある:

このスライドでは、タイマの PWM 周波数の設定方法について説明します。

このパラメータは、TIMx\_ARR レジスタでプログラムされた自動再ロード値(ARR)と、TIMx\_PSC レジスタでプログラムされたクロックプリスケーラを使用して定義されます。

PWM 周波数は、タイマ動作周波数( $f_{\text{TIM}}$ )を、 $(ARR + 1) \times (\text{クロックプリスケーラ} + 1)$ で割ることで求められます。

実際には、両方のレジスタの値を見つけるのは繰り返し処理となり、 $PSC = 0$  (クロック分周なし)で始める必要があります。これにより、PWM の分解能が可能な限り細かいものになることが保証されます。

この場合、ARR 値は単純にタイマクロック周波数と PWM 周波数の比率から 1 を引いたものになります。

この式で、タイマの ARR 範囲(選択したタイマに応じて 16 ビットまたは 32 ビットの値)を超える ARR 値が得られる場合は、次の順序で、より高いプリスケーラ値を使用して計算を再実行する必要があります。

$ARR \text{ 値} = (2 \text{ 分周したタイマクロック周波数を PWM 周波数で割って } 1 \text{ を引いたもの})$ 、次は  $ARR \text{ 値} = (3 \text{ 分周したタイマクロック周波数を PWM 周波数で割って } 1 \text{ を引いたもの})$ 、という順番で、ARR 値がプログラム可能な範囲内に収まるまで続けます。

- デューティサイクルセットアップ

- 自動再ロード(TIMx\_ARR の ARR)と比較値(TIMx\_CCRx の PSC)で定義:

$$\text{Duty Cycle} = \frac{CCRx + 1}{ARR + 1} \Rightarrow CCRx = (\text{Duty Cycle} \times (ARR + 1)) - 1$$

- PWM 分解能

- この分解能は、考えられるデューティサイクル値の数を与え、PWM 信号の制御をどの程度細かくするかを示す:

$$Res_{(steps)} = \frac{f_{TIM}}{f_{PWM}}$$

- DAC コンバータの出力解像度を示す場合と同様に、ビット単位で表現する方法もある:

$$Res_{(bits)} = \log_2 \left( \frac{f_{TIM}}{f_{PWM}} \right)$$

このスライドでは、特定の PWM 周波数のデューティサイクルをプログラムする方法について説明します。

このパラメータは、TIMx\_ARR レジスタでプログラムされた自動再ロード値(ARR)と、TIMx\_CCRx レジスタでプログラムされた比較値を使用して定義されます。

デューティサイクルは、PWM 周波数に依存せず、(比較値 +1)を、(自動再ロード値 +1)で割って求められます。

もう 1 つの役立つ指標は PWM 分解能です。

これは、考えられるデューティサイクル値の数を与え、PWM 信号の制御をどの程度細かくするかを示します。この分解能は、デューティサイクルステップの数で表され、単純にタイマクロック周波数と PWM 周波数の比率から 1 を引いたものになります。

DAC コンバータの出力解像度を示す場合と同様に、ビット単位で表現する方法もあります。この場合、分解能はタイマクロック周波数と PWM 周波数の比率の底 2 の対数から 1 を引いたものになります。

# アプリケーション例: LED の調光

35

- これは、電流が定格出力電流を超えない限り、PWM 出力を使用して直接行うことができる

- PWM 周波数: 1 kHz

- 周波数:  $ARR = \frac{f_{TIM}}{f_{PWM}} - 1 = \frac{128MHz}{1kHz} - 1 = 127999$

- ARR が 16 ビットの最大値を超えていている

- プリスケーラを 1 にセットする必要がある

- $ARR = \frac{f_{TIM}/2}{f_{PWM}} - 1 \Rightarrow ARR = \frac{128MHz/2}{1kHz} - 1 = 63999$

- 開始時のデューティサイクル = 20%

- $Duty\ Cycle = \frac{CCRx+1}{ARR+1} \Rightarrow CCRx = ((ARR + 1) \times Duty\ Cycle) - 1 = ((64000) \times 0.2) - 1 = 12799$

- 調光分解能

- $64000$  ステップまたは  $\log_2(64000) = 15.9$  ビット

このスライドでは、PWM の簡単な実用例として、低消費電力 LED を調光する例を示しています。

これは、電流が定格出力電流を超えない限り、PWM 出力を使用して直接行うことができます。

最初のステップでは、周波数を 1 kHz に設定するようにプログラムします。プリスケーラを使用せず、タイマの動作周波数を 128 MHz にして ARR 値の計算を行うと、結果は 127999 になります。これは、タイマ 1 で使用できる 16 ビットの範囲を超えてています。

タイマを 64 MHz で動作させるには、タイマプリスケーラを 1 にセットする必要があります。これにより、ARR レジスタの有効な値は 63999 になります。

2 番目のステップでは、デューティサイクルが 20% となるように比較レジスタの値を計算します。これにより、12799 の値が得られます。

最後に、調光分解能は前のスライドで示した式から計算できます。64 MHz で動作するタイマの場合、1 kHz PWM で 640000 調光ステップが得られます。これは、15.9 ビットの等価分解能に相当します。

## アプリケーションのヒントとコツ

36

- ・ タイマは全部設定、カウンタが開始され、PWM モードは有効になっており、対応する出力も有効だが、依然としてピンが動作しない…。

→ MOE ビットと CCxE ビットをセットすることを検討したか？

- ・ デッドタイムジェネレータを備えたタイマ(タイマ 1 および 15)の場合、TIMx\_BDTR レジスタのメイン出力イネーブル(MOE)ビットが、すべての出力を制御し、ブレーク入力で障害が検出された場合に回路遮断器として機能する(すべての PWM 出力をグローバルに無効にする)

→ 出力を有効にするには、MOE ビットをセット(設定)する必要がある

→ これは、タイマがデッドタイム挿入なしで使用されている場合でも有効

このスライドでは、「タイマは全部設定した。カウンタが開始された。PWM モードは有効になっている。対応する出力もそうなっている。しかし、依然としてピンが動作しない」というよくあるサポート事例について説明します。

通常、これは MOE ビットまたは CCxE ビットがセットされていないことが原因です。

TIMxCCER レジスタの CCxE ビットは、CCx チャネルの設定を入力または出力として定義します。CH1 チャネルで PWM 信号を取得するには、CC1E ビットをセットする必要があります。

デッドタイムジェネレータを搭載したタイマ(タイマ 1 および 15)の場合、TIMx\_BDTR レジスタのメイン出力イネーブル(MOE)ビットが、すべての出力を制御し、ブレーク入力で障害が検出された場合に回路遮断器として機能します(すべての PWM 出力をグローバルに無効にします)。

出力を有効にするには、MOE ビットをセット(設定)する必要があります。

これは、タイマがデッドタイム挿入なしで使用されている場合でも有効であり、タイマは汎用アプリケーションに使用されます。

# STM32G0 タイマ・インスタンス機能

37

| 機能       | TIM1<br>(高機能制御)                                                                            | TIM2                                       |                                        | TIM3                        |     | TIM6   |             | TIM7                        |                           | TIM14            |                  | TIM15            |                  | TIM16            |     | TIM17            |     |   |  |

|----------|--------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------|-----------------------------|-----|--------|-------------|-----------------------------|---------------------------|------------------|------------------|------------------|------------------|------------------|-----|------------------|-----|---|--|

|          |                                                                                            | (汎用)                                       |                                        | (基本)                        |     | (汎用)   |             | (基本)                        |                           | (汎用)             |                  | (基本)             |                  | (汎用)             |     | (基本)             |     |   |  |

| クロックソース  | CK_INT<br>外部入力ピン<br>外部トリガ入力 ETR                                                            | CK_INT<br>外部入力ピン<br>外部トリガ入力 ETR<br>内部トリガ入力 |                                        | CK_INT<br>外部入力ピン<br>内部トリガ入力 |     | CK_INT |             | CK_INT<br>外部入力ピン<br>内部トリガ入力 |                           | CK_INT<br>外部入力ピン |                  | CK_INT<br>外部入力ピン |                  | CK_INT<br>外部入力ピン |     | CK_INT<br>外部入力ピン |     |   |  |

| 分解能      | 16 ビット                                                                                     | 32 ビット                                     |                                        | 16 ビット                      |     | 16 ビット |             | 16 ビット                      |                           | 16 ビット           |                  | 16 ビット           |                  | 16 ビット           |     | 16 ビット           |     |   |  |

| プリスケーラ   | 16 ビット                                                                                     |                                            |                                        |                             |     |        |             |                             |                           |                  |                  |                  |                  |                  |     |                  |     |   |  |

| カウンタ方向   | アップ、ダウン、アップ&ダウン                                                                            |                                            | アップ、ダウン、アップ&ダウン                        |                             | アップ |        | アップ         |                             | アップ                       |                  | アップ              |                  | アップ              |                  | アップ |                  | アップ |   |  |

| 繰り返しカウンタ | ✓                                                                                          |                                            | -                                      |                             | -   |        | -           |                             | -                         |                  | -                |                  | -                |                  | ✓   |                  | ✓   |   |  |

| 同期       | マスタ                                                                                        | ✓                                          |                                        | ✓                           |     | ✓      |             | ✓                           |                           | -                |                  | -                |                  | -                |     | ✓                |     | ✓ |  |

|          | スレーブ                                                                                       | ✓                                          |                                        | ✓                           |     | -      |             | -                           |                           | -                |                  | -                |                  | ✓                |     | -                |     | - |  |

| チャネル数    | 6:<br>➢ CH1/CH1N<br>➢ CH2/CH2N<br>➢ CH3/CH3N<br>➢ CH4<br>➢ CH5 および CH6 出力のみ、外部では<br>使用できない |                                            | 4:<br>➢ CH1<br>➢ CH2<br>➢ CH3<br>➢ CH4 |                             | 0   |        | 1:<br>➢ CH1 |                             | 2:<br>➢ CH1/CH1N<br>➢ CH2 |                  | 1:<br>➢ CH1/CH1N |                  | 1:<br>➢ CH1/CH1N |                  | -   |                  | -   |   |  |

| トリガ入力    | ✓                                                                                          |                                            | ✓                                      |                             | -   |        | -           |                             | -                         |                  | -                |                  | -                |                  | -   |                  | -   |   |  |

このスライドでは、STM32G0 マイクロコントローラに搭載されているタイマインスタンスの一覧を示しています。

タイマ 1 はフル装備のタイマで、モータ制御に対応しており、すべての PWM オプションと、3 相 PWM 信号を同時に生成して 2 つの独立した ADC トリガを生成するための 6 個の比較チャネルを搭載しています。

タイマ 15、16、17 は汎用タイマです。タイマ 15 のみが、相補チャネルと高度な PWM モードをサポートします。

タイマ 2 および 3 は、高度な PWM モード、アップダウンカウント機能、および 4 チャネルを備えた汎用タイマです。タイマ 2 は、さらに 32 ビットのカウント範囲を提供します。

タイマ 14 は軽量型のタイマで、標準の PWM のみをサポートし、1 つのチャネルとアップカウントモードのみを備えています。これらは、追加の独立したタイムベースが必要な場合に他のタイマを補完します。

最後に、タイマ 6 と 7 は出力を持たない純粋なタイムベースで、主に DAC コンバータのトリガやソフトウェアのタイムベースとして使用されます。

# STM32G0 タイマ・インスタンス機能

38

| 機能               | TIM1<br>(高機能制御)                               | TIM2               | TIM3 | TIM6 | TIM7 | TIM14 | TIM15              | TIM16 | TIM17 |

|------------------|-----------------------------------------------|--------------------|------|------|------|-------|--------------------|-------|-------|

| 入力キャプチャモード       | ✓                                             | ✓                  |      | -    |      | ✓     |                    | ✓     |       |

| PWM 入力モード        | ✓                                             | ✓                  |      | -    |      |       | ✓                  | -     |       |

| 強制出力モード          | ✓                                             | ✓                  |      | -    |      | ✓     |                    | ✓     |       |

| 出力比較モード          | ✓                                             | ✓                  |      | -    |      | ✓     |                    | ✓     |       |

| PWM              | 標準<br>非対称<br>組み合わせ<br>組み合わせ 3 相<br>6 ステップ PWM | 標準<br>非対称<br>組み合わせ |      | -    |      | 標準    | 標準<br>非対称<br>組み合わせ | 標準    |       |

| プログラム可能なデッドタイム   | ✓(CH1-3)                                      | -                  |      | -    |      | -     | ✓(CH1)             | -     |       |

| ブレーク入力           | 2 双方向                                         | 0                  |      | 0    |      | 0     | 1 双方向              |       |       |

| ワンパルスモード         | ✓                                             | ✓                  |      | -    |      | ✓     |                    | ✓     |       |

| 再トリガ可能なワンパルスモード  | ✓                                             | ✓                  |      | -    |      | -     | ✓                  | -     |       |

| エンコーダインターフェースモード | ✓                                             | ✓                  |      | -    |      | -     |                    | -     |       |

| タイマ入力 XOR 機能     | ✓                                             | -                  |      | -    |      | -     | ✓                  | -     |       |

| DMA              | ✓                                             | ✓                  |      | ✓    |      | -     |                    | ✓     |       |

このスライドは、STM32G0 に存在する各タイマに実装されている機能を示しています。

入力キャプチャと出力比較は、タイマ 6 と 7 ではサポートされていません。

プログラム可能なデッドタイムは、タイマに相補出力がある場合に意味があります。これに該当するのは、タイマ 1(チャネル 1~3)とタイマ 15(チャネル1)です。

タイマ 1、15、16、17 はブレーク入力をサポートしています。

再トリガ可能なワンパルスモードは、タイマ 14、16、17 ではサポートされていません。

タイマ 1、2、3 のみがエンコーダインターフェースを備えています。チャネルを結合する XOR 機能は、タイマ 1 および 15 でのみ使用可能です。

タイマ 14 は DMA リクエストをアサートできません。

- タイマにリンクされている次のペリフェラルのトレーニング資料を参照

- ADC

- タイマはインジェクト変換とレギュラ変換をトリガする

- PWM はアナログウォッチドッグによって停止できる

- DAC

- タイマは変換をトリガする

- 相互接続マトリックス

- ペリフェラル間の直接接続を制御

- RCC

- RCC はタイマ内部クロックリファレンスを提供

- COMP

- コンパレータ出力はブレークイベントをトリガできる

タイマは、複数のオンチップペリフェラルにリンクされています。ADC および DAC コンバータのトリガソースとして機能します。相互接続マトリックスにより、マスタインタフェースとスレーブインターフェースを使用したタイマ同士の直接接続、およびタイマと他のペリフェラル間の直接接続が可能になります。RCC と呼ばれるリセットおよびクロック制御ユニットは、すべてのタイマの内部クロックリファレンスを提供します。最後に、コンパレータユニットは、異常な温度または電圧状態を検出し、タイマブレークイベントを発生させることができます。

- 詳細については、次のソースを参照：

- AN2592

- How to achieve 32-bit timer resolution using the link system in STM32F10x and STM32L15x microcontrollers (includes software: STSW-STM32009)

- AN4013

- STM32 cross-series timer overview

- AN4507

- PWM resolution enhancement through dithering technique for STM32 advanced-configuration, general-purpose and lite timers (includes software: STSW-STM32151)

- AN4776

- General-purpose timer cookbook

以下の 3 つのアプリケーションノートがリファレンスマニュアルのタイマセクションを補完します。

AN2592 は、同期した 2 つの 16 ビットタイマで構成される 32 ビットタイマの実用的な実装方法を示しており、タイマ同期メカニズム全体の理解を深めるのに役立ちます。ソフトウェア例も付属しています。

AN4013 には、すべてのタイマ機能の詳細な概要と、使用可能なファームウェアの例が記載されています。

AN4507 には、ディザリング技術を用いた PWM 分解能の向上の実装方法が示されています。ソフトウェア例も付属しています。

AN4776 は、タイマの動作原理に関する注意点から始まり、標準的なタイマの使用例がいくつか記載されています。ソフトウェア例も付属しています。