# STM32G4 – DMA & DMAMUX

ダイレクト・メモリ・アクセス(DMA)コントローラ

DMA リクエスト・マルチプレクサ(DMAMUX)

1.0版

STM32G4 ダイレクトメモリアクセス コントローラ(DMA)のプレゼンテーションへようこそ。

ここでは、新しい DMA リクエストマルチプレクサ(DMAMUX)モジュールによって強化された、DMA コントローラモジュールの主要な機能の説明を行います。

- それぞれ次の処理が実行可能なDMAコントローラx2:

- 独立に設定可能でプログラム可能な同時8チャネル・ブロック転送

- プログラム可能なチャネル・ベースの優先度

- AHBマスタポート経由のデータ転送

- DMAリクエストルータ(DMAMUX) x1

- プログラム可能なリクエスト・ソース選択

- DMAモードでペリフェラルから

- トリガからと内部生成

- 同期モード: リクエスト・カウンタを用いて、同期入力から

- リクエスト連鎖: リクエスト・カウンタを用いて、別のリクエスト/チャネルへの入力トリガ、あるいは同期であるイベントを生成

### アプリケーション側の利点

メモリマップされたソースからメモリ・マップされたデスティネーションへのデータ転送。CPU負荷のオフロード

アプリケーションにとってのDMAの主な利点は、あらゆるメモリマップされた転送元からあらゆるメモリマップされた転送先へのデータ転送にCPU負荷をオフロードすることです。

### STM32G4 DMAの機能:

- 2 DMAコントローラ。DMAコントローラごとに次の処理が可能:

- ❖ プログラム可能な同時8チャネルブロック転送(チャネルごとに独立設定可能)

- ❖ プログラム可能なチャネルベース優先度

- ❖ (バスマトリックスに接続された)AHBマスタポート経由のデータ転送

- DMAリクエストルータ(DMAMUX)の機能:

- ❖ プログラム可能なリクエストソース選択: DMAモードでペリフェラルから、あるいは、トリガ後に内部生成

- ❖ 同期モード: DMAMUXリクエストカウンタを用いて同期入力(ハードウェアイベント)から

- ❖ リクエスト連鎖: DMAMUXリクエストカウンタを用いて、別のリクエスト/チャネルへの入力トリガあるいは同期であるイベントを生成

# STM32G4 DMA と DMAMUX 例

3

| DMAMUX の機能     | DMAMUX |

|----------------|--------|

| ペリフェラル・リクエストの数 | 115    |

| リクエスト・ジェネレータの数 | 4      |

| トリガの数          | 21     |

| 同期の数           | 21     |

| 出力DMAリクエストの数   | 16     |

| DMA の機能 | DMA1 |

|---------|------|

| チャネル数   | 8    |

| DMA の機能 | DMA2 |

|---------|------|

| チャネル数   | 8    |

ペリフェラルリクエストは 115 本、DMAMUX リクエストジェネレータは 4 個あります。

トリガと同期入力は 21 本あります。

DMA チャネル/リクエストは 16 本あります。

# DMA コントローラ (1/3)

4

- 1 個の DMA コントローラに個別に設定可能なチャネル

- チャネルは、メモリからペリフェラルまたはペリフェラルからメモリへの転送において、ペリフェラルからの DMA ハードウェア・リクエストに割当て可能

- あるいは、メモリ間転送におけるソフトウェア・リクエストにチャネルを割り当てる

- チャネルは優先順位レベルを付けてプログラムされる

- チャネルはブロック・レベルでのデータ転送回数に対してプログラムされる

- ソフトウェアは、ブロック転送完了、ハーフブロック転送完了、転送エラーなどのプログラム可能なイベントに対する個別の割込みやフラグを通じてチャネルを制御

- バス・アクセス・エラーの場合、障害のあるチャネルは自動的に無効となる

DMA コントローラに焦点を合わせて説明します。

DMA コントローラのチャネルごとに個別に設定可能：

- チャネルは、ペリフェラルからメモリまたはメモリからペリフェラルへのデータ転送において、ペリフェラルからの DMA ハードウェア・リクエストに割当て可能です。

- あるいは、メモリ間データ転送におけるソフトウェア・リクエストにチャネルを割り当てます。

- チャネルは優先順位レベル付きでプログラムされます。

- チャネルはブロックレベルでのデータ転送回数に対してプログラムされます。

ソフトウェアは、ブロック転送完了、ハーフブロック転送完了、転送エラーなどのプログラム可能なイベントに対する個別の割込みやフラグを通じてチャネルを制御可能です。

バスアクセスエラーの場合、障害のあるチャネルは自動的に無効となります。

## DMA コントローラ (2/3)

5

- ブロック・レベルでのプログラム可能なデータ転送

- 転送元と転送先のデータ・サイズは独立 : 8bit、16bit、32bit

- 転送元と転送先の開始アドレスは独立

- 転送元と転送先のアドレスインクリメントは独立 : 連続インクリメントまたは固定アドレス

- プログラム可能なブロック内転送データ数

- 最大 65,535 個の転送元データ

- ハードウェアにより自動デクリメント

- サーキュラバッファ・モード(ペリフェラルとの連続データ転送)におけるブロック転送完了時:

- 次のプログラムされた情報がハードウェアにより自動で再ロード:

- ブロック内で転送されるデータ量

- 転送元と転送先の開始アドレス

チャネルはブロックレベルでのデータ転送回数に対してプログラムされます。

- 転送元と転送先のデータサイズは独立

- 転送元と転送先の開始アドレスは独立

- 転送元と転送先のアドレスインクリメントは独立(連続インクリメントまたは固定アドレス)

- プログラム可能なブロック内転送データ数

- ❖ 最大 65,535 個の転送元データ

- ❖ ハードウェアにより自動デクリメント

サーキュラバッファモード(ペリフェラルとの連続データ転送)におけるブロック転送完了時:

- プログラムされたブロック内転送データ数は、ハードウェアによって自動的に再ロードされます。

- 転送元と転送先の開始アドレスも同様です。

## DMA コントローラ (3/3)

6

- メモリ間モード:

- チャネルがこのモードで有効(ハードウェアリクエストなし)になると、直ちにブロック転送が開始される

- ペリフェラルからメモリ・モードおよびメモリからペリフェラル・モード:

- 1) チャネルが有効になり、かつ2) ペリフェラルが DMA ハードウェアリクエストを送信すると、直ちにブロック転送が開始される

- DMA ハードウェア・リクエストによって、DMA データ転送が(1つだけ)特定される

- 各データが転送先に正常に転送されると、DMA ハードウェア・リクエストごとに DMA による速度調整と許可が行われる

- 全モード:

- データ転送ごとにチャネル・アビトレーションが再評価される

メモリ間モードでチャネルが有効(ハードウェアリクエストなし)になると、直ちにブロック転送が開始されます。

その一方で、ペリフェラルからメモリモードおよびメモリからペリフェラルモードにおいて:

- 1) チャネルが有効になり、かつ2) ペリフェラルが DMA ハードウェアリクエストを送信すると、直ちにブロック転送が開始されます。

- DMA ハードウェアリクエストによって、DMA データ転送が(1つだけ)特定されます。

- 各データが転送先に正常に転送されると、DMA ハードウェアリクエストごとに DMA による速度調整と許可が行われます。

どのモードでも、データ転送ごとにチャネルアビトレーションが再評価されます。

- チャネルごとの割込みイベント

| 割込みイベント  | 説明                                     |

|----------|----------------------------------------|

| 1/2 転送   | データ・ブロックの半分が転送されたときにセット                |

| 転送完了     | ブロック転送が完了したときにセット                      |

| 転送エラー    | データ転送中にエラーが発生したときにセット                  |

| グローバル割込み | 1/2 転送、転送完了、または転送エラーのイベントが発生したときに常にセット |

DMA チャネルごとに、次の 4 種類の起こり得るイベントによってトリガされた割込みをソフトウェアに通知可能です。

- ハーフブロック転送完了

- ブロック転送完了

- 転送エラー

- 上記 3 イベントのいずれか(グローバル)

# DMAMUX ブロック図

8

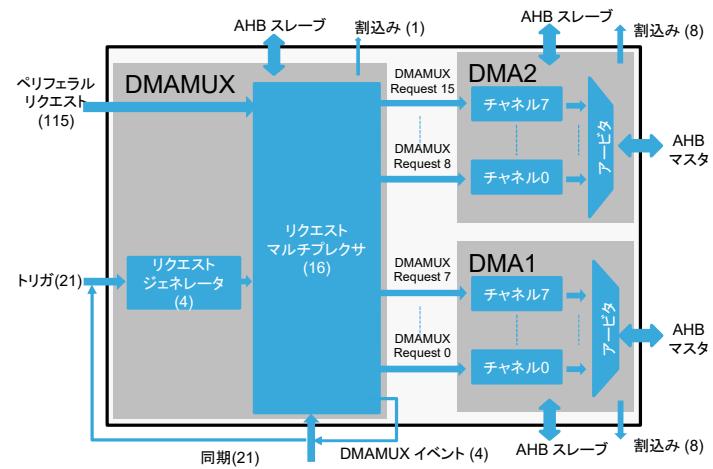

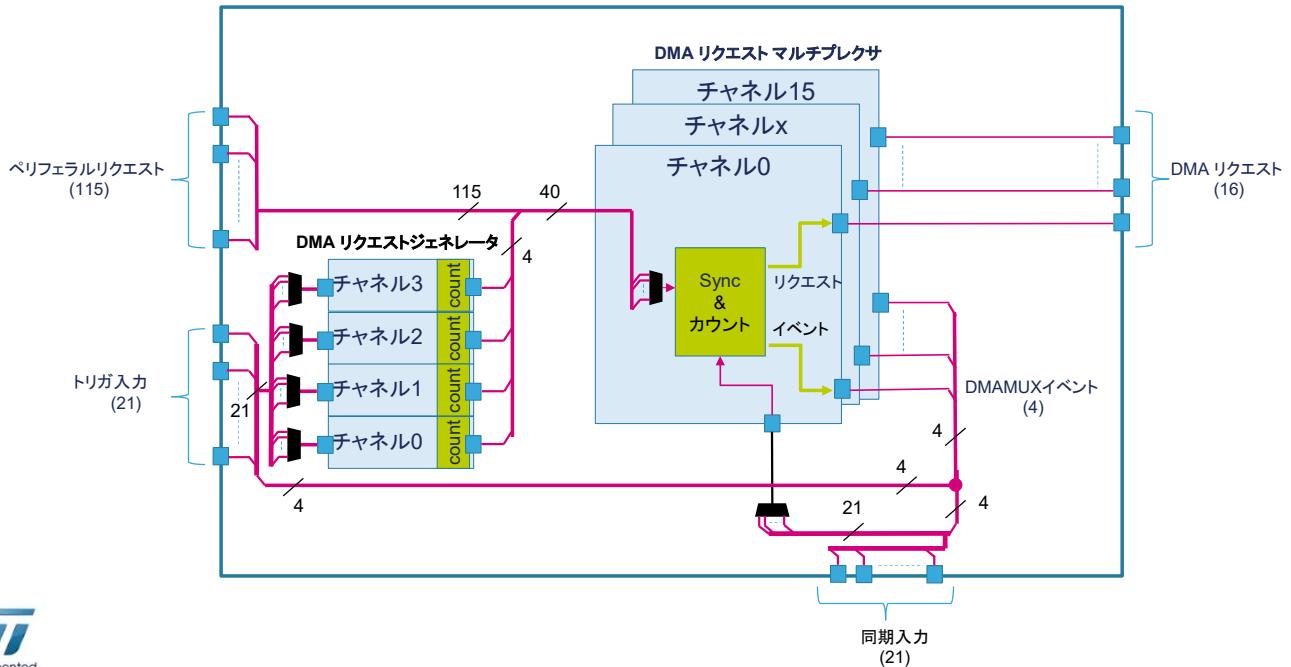

DMAMUX には、リクエストマルチプレクサとリクエストジェネレータの 2 つの主なサブブロックがあります。

DMAMUX リクエストマルチプレクサにより、ペリフェラルから DMA コントローラへの DMA リクエストをルーティングすることができます。

ルーティング機能は、プログラム可能なマルチチャネル DMA リクエストマルチプレクサにより保証されます。

各チャネルは、DMAMUX 同期入力のイベントで無条件に、または同期的に一意の DMA リクエストを選択します。

DMAMUX は、入力トリガ信号のプログラム可能なイベントからの DMA リクエストジェネレータとしても使用できます。

DMA リクエストマルチプレクサチャネルは、DMA コントローラに対するリクエストと、同期入力としてもトリガ入力としても使用可能なイベントの両方を生成します。

DMA リクエストジェネレータチャネル(0~3)のことを、DMA リクエストマルチプレクサチャネル(0~13)と混同しないようにしてください。

# DMAMUX リクエスト・マルチプレクサ (1/6)

9

- 各マルチプレクサ・チャネルに対して

- 設定レジスタ: DMAMUX\_CxCR

- プログラム可能な入力リクエスト選択(DMAREQ\_ID フィールド経由)

- DMA モードで動作しているペリフェラルからのリクエストごとに、DMAREQ\_ID が割り当てられる

- DMAREQ\_ID = 0 は、DMA リクエストが選択されていない状態に相当する

- このチャネルと、それがルーティングされる DMA コントローラが設定された後に、DMA チャネルが有効になることが可能

- 同じ DMA リクエスト入力を 2 つの異なるチャネルに設定することは出来ない

マルチプレクサチャネルごとに設定レジスタがあります。

DMAMUX\_CxCR:

- プログラム可能な入力リクエスト選択(DMAREQ\_ID フィールド経由)

- DMA モードで動作しているペリフェラルからのリクエストごとに、DMARAQ\_ID が割り当てられます。

- DMAREQ\_ID = 0x00 は、DMA リクエストが選択されていない状態に相当します。

- このチャネルと、それがルーティングされる DMA コントローラが設定された後に、DMA チャネルの有効化が可能となります。同じ DMA リクエスト入力を 2 つの異なるチャネルに設定することはできません。

## DMAMUX リクエスト・マルチプレクサ (2/6)

10

- 各マルチプレクサ・チャネルに対して

- 内蔵 DMA リクエスト・カウンタ

- プログラム可能(NBREQ フィールド経由)

- 処理された DMA リクエストによって、プログラムされた DMA リクエスト・カウンタがデクリメントされる。アンダーラン時には:

- NBREQ フィールドにプログラムされた値にDMA リクエストカウンタが自動的に再ロードされる

- アンダーラン時には、DMAMUX イベントの生成が可能

- 有効化されている場合(EGE フィールド経由)

- (チャネル 0 から3までの)4つの DMAMUX イベントがループバックされ、トリガ入力および同期入力として DMAMUX に接続

- これによって、同期やトリガを通じて、リクエストが別の異なる DMA チャネルに連鎖できる

各マルチプレクサチャネルに対して:

- 内蔵 DMA リクエストカウンタが(NBREQ フィールド経由で)プログラム可能です。

- 処理された DMA リクエストによって、プログラムされた DMA リクエストカウンタがデクリメントされます。アンダーラン時には、NBREQ フィールドにプログラムされた値に DMA リクエストカウンタが自動的に再ロードされます。

- アンダーラン時には、有効化されている場合(EGE フィールド経由)、DMAMUX イベントの生成が可能です。

- (チャネル 0 から 3 までの)4 つの DMAMUX イベントがループバックされ、トリガ入力および同期入力として DMAMUX に接続されます。これによって、同期やトリガを通じて、リクエストが別の異なる DMA チャネルに連鎖できます。

## DMAMUX リクエスト・マルチプレクサ (3/6)

11

- 各マルチプレクサ・チャネルに対して

- (SE フィールド経由でプログラムされた)2 種類の動作モード

- 無条件モード: 入力リクエストがそのまま出力

- 同期モード: いくつかのリクエストがグループ化されて遅延／同期される

各マルチプレクサチャネルに対して、(SE フィールド経由でプログラムされた)2 種類の動作モードがあります。

- 無条件モード: 入力リクエストがそのまま出力されます。

- 同期モード: いくつかのリクエストがグループ化されて遅延/同期されます。

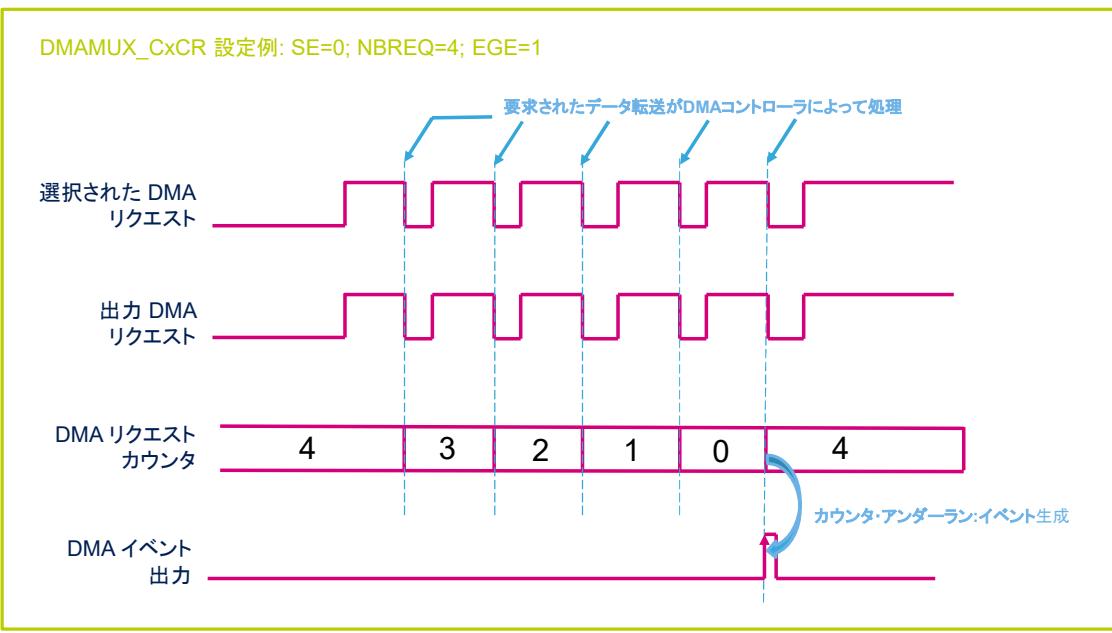

## DMAMUX リクエスト・マルチプレクサ (4/6) 無条件モード

12

リクエストマルチプレクサチャネルが無条件(SE=0)に設定されている場合、DMA リクエストはそのまま、DMA コントローラによって速度調整された通りに送信されます。

DMA コントローラがデータ転送を完了すると、DMA リクエストがデアサートされて、内蔵 DMA リクエストカウンタがデクリメントされます。

カウンタのアンダーラン時には、EGE フィールド経由で有効化されている場合、イベントの生成が可能です。

# DMAMUX リクエスト・マルチプレクサ (5/6)

## 同期モード

13

- 同期モードでは、追加で

- リクエストが次のもので条件付けされる

- プログラム可能な同期入力選択(SYNC\_ID フィールド経由)

- プログラム可能な同期イベント:なし/立ち上がりエッジ/立ち下がりエッジ/両エッジ(SPOL フィールド経由)

- イベント生成にも使用可能な単一の内蔵リクエスト・カウンタ(NBREQ フィールド経由)

- 同期イベント後

- 出力 DMA リクエストは保留中の入力リクエストに接続

- カウンタアンダーラン時

- DMA 出力リクエストはマルチプレクサ・チャネル入力から切断

- 同期オーバーランフラグ(DMAMUX\_CSR の SOFx)が報告された

- カウンタアンダーランの前に新しい同期イベントが発生した場合

- (SOIE フィールド経由で)有効になっている場合に割込みを生成

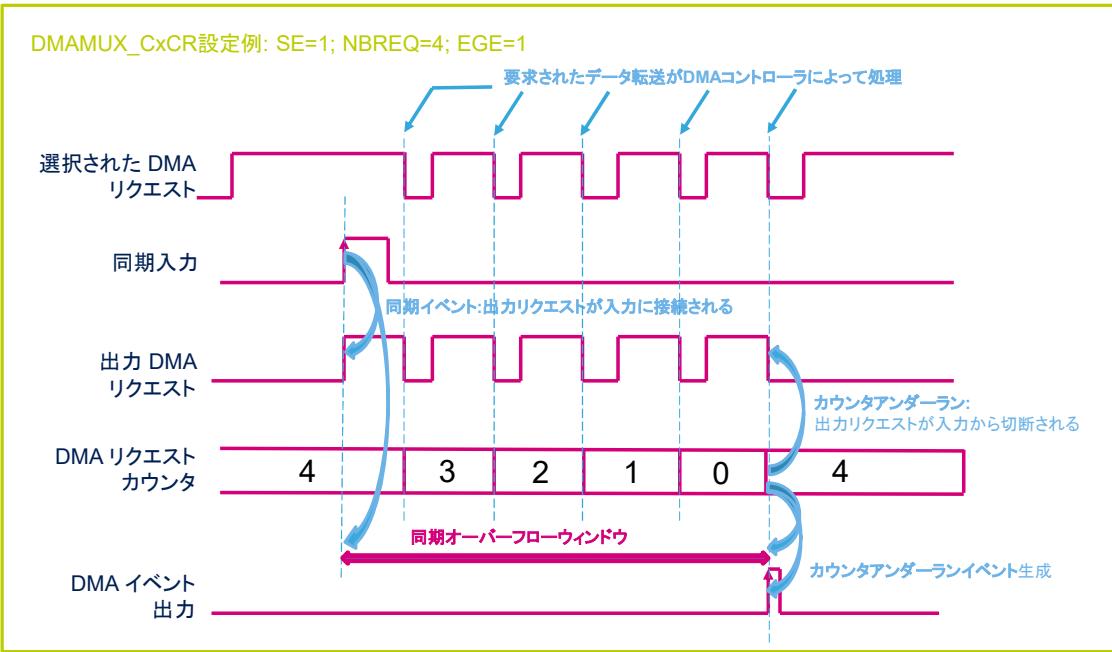

同期モードでは、追加で:

- リクエストが条件付けされる:

- ❖ プログラム可能な同期入力選択(SYNC\_ID フィールド経由)

- ❖ プログラム可能な同期イベント:なし/立ち上がりエッジ/立ち下がりエッジ/両エッジ(SPOL フィールド経由)

- ❖ イベント生成にも使用可能な単一の内蔵リクエストカウンタ(NBREQ フィールド経由)

- 同期イベント後:

- ❖ 出力 DMA リクエストは保留中の入力リクエストに接続

- カウンタアンダーラン時:

- ❖ DMA 出力リクエストはマルチプレクサチャネル入力から切断

- 最後に、同期オーバーランフラグ(DMAMUX\_CSR の SOFx)が報告される:

- ❖ カウンタアンダーランの前に新しい同期イベントが発生した場合

- ❖ (SOIE フィールド経由で)有効になっている場合に割込みを生成

# DMAMUX リクエスト・マルチプレクサ (6/6)

14

同期モード

DMAMUX チャネルが同期モードに設定されている場合、その動作は以下のようになります。

リクエストマルチプレクサ入力(ペリフェラルからの DMA リクエスト)は保留とすることが可能であり、同期イベントを受け取るまでは DMAMUX リクエストマルチプレクサ出力に転送されません。

その後、リクエストマルチプレクサはその入力と出力を接続し、すべてのペリフェラルリクエストが転送されます。

転送と許可が行われた DMA リクエストごとに、(規定されたプログラム値に設定されている)リクエストマルチプレクサカウンタをデクリメントします。カウンタがゼロに達すると、DMA コントローラとペリフェラルの間の接続は切断され、新しい同期イベントを待ちます。

カウンタがアンダーランするたびに、リクエストマルチプレクサがオプションのイベントを生成して、2 番目の DMAMUX リクエストマルチプレクサチャネルの同期やトリガを行なうことができます。

同じイベントが、CPU の介入なくシステムを STOP モードに戻す一部の低電力シナリオで使用することができます。

同期モードは、たとえば、データ転送をタイマに自動同期させたり、同期入力としてマッピングされているあらゆるペリフェラルイベントからの転送を条件づけたりするために使用することができます。

加えて、同期オーバーフローによって、プログラムされている数の DMA リクエストが 2 つの同期イベントの間に完了していない場合に、ソフトウェアへの通知を行えます。

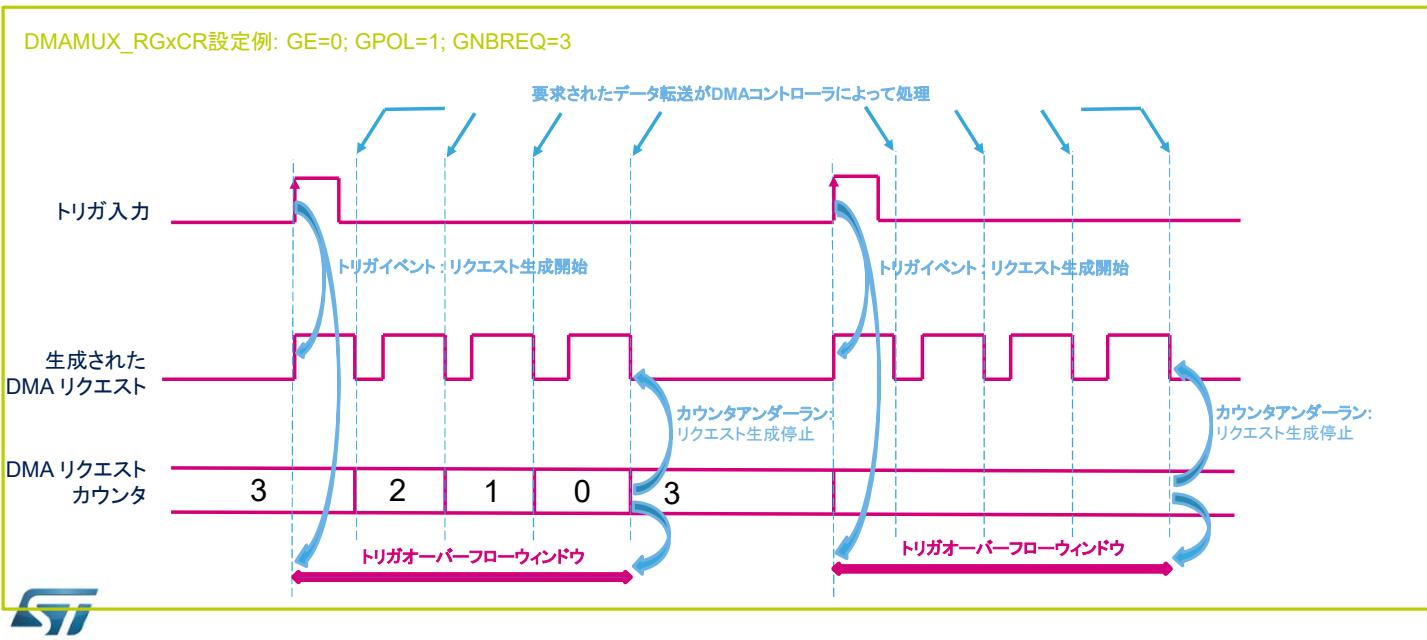

# DMAMUX リクエスト・ジェネレータ

15

- 各チャネルに対して

- DMA リクエストがトリガイベントの後に生成可能。DMAMUX リクエスト・マルチプレクサ・チャネルの入力として選択される。(DMAMUX\_CxCR の DMAREQ\_ID フィールド経由)

- (GE フィールドによって)有効化されている場合、設定レジスタ DMAMUX\_RGxCR 経由で次のものによってリクエストが生成される

- プログラム可能なトリガ入力選択(SIG\_ID フィールド経由)

- プログラム可能なトリガ・イベント:なし/立ち上がりエッジ/立ち下がりエッジ/両エッジ(GPOL フィールド経由)

- 内蔵リクエスト・カウンタ(GBREQ フィールド経由)

- 処理された DMA リクエストによって、プログラムされたリクエスト・カウンタがデクリメントされる

- アンダーラン時には:

- GNBREQ フィールドにプログラムされた値にリクエスト・カウンタが自動的に再ロードされる

- リクエスト・ジェネレータは、リクエストの生成を停止

- トリガ・オーバーラン・フラグ(DMAMUX\_RGSR の OFx)が報告される

- カウンタアンダーランの前に新しいトリガイベントが発生した場合

- (OIE フィールド経由で)有効になっている場合に割込みを生成

各リクエストジェネレータチャネルに対して:

- DMA リクエストがトリガイベントの後に生成可能であり、DMAMUX リクエストマルチプレクサチャネルの入力として選択されます(DMAMUX\_CxCR の DMAREQ\_ID フィールド経由)。

- (GE フィールドによって)有効化されている場合、設定レジスタ DMAMUX\_RGxCR 経由で次のものによってリクエストが生成されます。

- プログラム可能なトリガ入力選択(SIG\_ID フィールド経由)

- プログラム可能なトリガイベント:なし/立ち上がりエッジ/立ち下がりエッジ/両エッジ(GPOL フィールド経由)

- 内蔵リクエストカウンタ(GBREQ フィールド経由)

- 処理された DMA リクエストによって、プログラムされたリクエストカウンタがデクリメントされます。

- アンダーラン時には:

- GNBREQ フィールドにプログラムされた値にリクエストカウンタが自動的に再ロードされます。

- リクエストジェネレータは、リクエストの生成を停止します。

- トリガオーバーランフラグ(DMAMUX\_RGSR の OFx)が報告されます。

- カウンタアンダーランの前に新しいトリガイベントが発生した場合

- (OIE フィールド経由で)有効になっている場合に割込みを生成

# DMAMUX リクエスト・ジェネレータ

16

トリガイベント発生時に、プログラムされた数の DMA リクエスト (GNBREQ+1) が生成されます。

GNBREQ+1 回のリクエストの前にトリガイベントが 2 回発生し、データ転送が完了した場合、トリガオーバーフローが発生することがあります。

# DMAMUX リクエスト・マルチプレクサ入力

17

| DMAREQ_ID | リソース            | DMAREQ_ID | リソース       | DMAREQ_ID | リソース         |

|-----------|-----------------|-----------|------------|-----------|--------------|

| 1         | dmamux_req_gen0 | 44        | TIM1_CH3   | 87        | TIM20_CH2    |

| 2         | dmamux_req_gen1 | 45        | TIM1_CH4   | 88        | TIM20_CH3    |

| 3         | dmamux_req_gen2 | 46        | TIM1_UP    | 89        | TIM20_CH4    |

| 4         | dmamux_req_gen3 | 47        | TIM1_TRIG  | 90        | TIM20_UP     |

| 5         | ADC1            | 48        | TIM1_COM   | 91        | AES_IN       |

| 6         | DAC1_CH1        | 49        | TIM8_CH1   | 92        | AES_OUT      |

| 7         | DAC1_CH2        | 50        | TIM8_CH2   | 93        | TIM20_TRIG   |

| 8         | TIM6_UP         | 51        | TIM8_CH3   | 94        | TIM20_COM    |

| 9         | TIM7_UP         | 52        | TIM8_CH4   | 95        | HRTIM_MASTER |

| 10        | SPI1_RX         | 53        | TIM8_UP    | 96        | HRTIM_TIMA   |

| 11        | SPI1_TX         | 54        | TIM8_TRIG  | 97        | HRTIM_TIMB   |

| 12        | SPI2_RX         | 55        | TIM8_COM   | 98        | HRTIM_TIMC   |

| 13        | SPI2_TX         | 56        | TIM2_CH1   | 99        | HRTIM_TIMD   |

| 14        | SPI3_RX         | 57        | TIM2_CH2   | 100       | HRTIM_TIME   |

| 15        | SPI3_TX         | 58        | TIM2_CH3   | 101       | HRTIM_TIMF   |

| 16        | I2C1_RX         | 59        | TIM2_CH4   | 102       | DAC3_CH1     |

| 17        | I2C1_TX         | 60        | TIM2_UP    | 103       | DAC3_CH2     |

| 18        | I2C2_RX         | 61        | TIM3_CH1   | 104       | DAC4_CH1     |

| 19        | I2C2_TX         | 62        | TIM3_CH2   | 105       | DAC4_CH2     |

| 20        | I2C3_RX         | 63        | TIM3_CH3   | 106       | SPI4_RX      |

| 21        | I2C3_TX         | 64        | TIM3_CH4   | 107       | SPI4_TX      |

| 22        | I2C4_RX         | 65        | TIM3_UP    | 108       | SAI1_A       |

| 23        | I2C4_TX         | 66        | TIM3_TRIG  | 109       | SAI1_B       |

| 24        | USART1_RX       | 67        | TIM4_CH1   | 110       | FMAC_Read    |

| 25        | USART1_TX       | 68        | TIM4_CH2   | 111       | FMAC_Write   |

| 26        | USART2_RX       | 69        | TIM4_CH3   | 112       | Cordic_Read  |

| 27        | USART2_TX       | 70        | TIM4_CH4   | 113       | Cordic_Write |

| 28        | USART3_RX       | 71        | TIM4_UP    | 114       | USBPD_RX     |

| 29        | USART3_TX       | 72        | TIM5_CH1   | 115       | USBPD_TX     |

| 30        | UART4_RX        | 73        | TIM5_CH2   |           |              |

| 31        | UART4_TX        | 74        | TIM5_CH3   |           |              |

| 32        | UART5_RX        | 75        | TIM5_CH4   |           |              |

| 33        | UART5_TX        | 76        | TIM5_UP    |           |              |

| 34        | LPUART1_RX      | 77        | TIM5_TRIG  |           |              |

| 35        | LPUART1_TX      | 78        | TIM15_CH1  |           |              |

| 36        | ADC2            | 79        | TIM15_UP   |           |              |

| 37        | ADC3            | 80        | TIM15_TRIG |           |              |

| 38        | ADC4            | 81        | TIM15_COM  |           |              |

| 39        | ADC5            | 82        | TIM16_CH1  |           |              |

| 40        | QUADSPI         | 83        | TIM16_UP   |           |              |

| 41        | DAC2_CH1        | 84        | TIM17_CH1  |           |              |

| 42        | TIM1_CH1        | 85        | TIM17_UP   |           |              |

| 43        | TIM1_CH2        | 86        | TIM20_CH1  |           |              |

この表には、STM32G4のあらゆるチャネルに対するDMAMUX リクエストマルチプレクサ入力のマッピングが示されています。リクエスト入力の割当ては、あらゆる DMAMUX リクエストマルチプレクサチャネルに対する DMAREQ\_ID (DMAMUX\_CxCR レジスタ)によりプログラムされます。同じリクエスト入力は、異なる 2 つのチャネルに配置することはできません。

# DMAMUX トリガ & 同期入力

18

| SIG_ID<br>SYNC_ID | リソース      | SIG_ID<br>SYNC_ID | リソース        |

|-------------------|-----------|-------------------|-------------|

| 0                 | EXTIライン0  | 12                | EXTIライン12   |

| 1                 | EXTIライン1  | 13                | EXTIライン13   |

| 2                 | EXTIライン2  | 14                | EXTIライン14   |

| 3                 | EXTIライン3  | 15                | EXTIライン15   |

| 4                 | EXTIライン4  | 16                | dmamux_evt0 |

| 5                 | EXTIライン5  | 17                | dmamux_evt1 |

| 6                 | EXTIライン6  | 18                | dmamux_evt2 |

| 7                 | EXTIライン7  | 19                | dmamux_evt3 |

| 8                 | EXTIライン8  |                   |             |

| 9                 | EXTIライン9  |                   |             |

| 10                | EXTIライン10 |                   |             |

| 11                | EXTIライン11 |                   |             |

この表には、あらゆるチャネルに対するトリガ入力と同期入力の STM32G4 のマッピングが示されています。

トリガ入力の割当ては、あらゆる DMAMUX リクエストジェネレータ x (DMAMUX\_RGxCR レジスタ) の SIG\_ID フィールドによりプログラムされます。

同期入力の割当ては、あらゆる DMAMUX リクエストマルチプレクサチャネル x (DMAMUX\_CxCR レジスタ) の SYNC\_ID フィールドによりプログラムされます。

# DMAMUX 割込み

19

- 各リクエスト・ジェネレータ・チャネルに対する割込みイベント

| 割込みイベント                 | 説明                                                                                   |

|-------------------------|--------------------------------------------------------------------------------------|

| リクエスト・ジェネレータ・トリガ・オーバーラン | トリガ入力オーバーランが検出されたときにセット<br>(その前に、DMAMUX リクエスト・ジェネレータにより生成されたプログラムされた数の DMA リクエストが完了) |

- 各リクエスト・マルチプレクサ・チャネルに対する割込みイベント

| 割込みイベント               | 説明                                                                                |

|-----------------------|-----------------------------------------------------------------------------------|

| リクエスト・マルチプレクサ同期オーバーラン | 同期入力オーバーランが検出されたときにセット<br>(その前に、プログラムされた数の送信された DMA リクエストまたは生成された DMAMUX イベントが完了) |

DMAMUX リクエストジェネレータチャネルごとに、トリガオーバーランをソフトウェアに通知可能です。

DMAMUX リクエストマルチプレクサチャネルごとに、同期オーバーランをソフトウェアに通知可能です。

# 低電力モードでの DMA/DMAMUX

20

| モード         | 説明                                                 |

|-------------|----------------------------------------------------|

| RUN         | 有効                                                 |

| 低電力 RUN     | 有効                                                 |

| SLEEP       | 有効 DMA/DMAMUX割込みが CPU をウェイクアップ可能                   |

| 低電力 SLEEP   | 有効 DMA/DMAMUX割込みが CPU をウェイクアップ可能                   |

| STOP0/STOP1 | クロックトオフ & 停止 DMA/DMAMUX レジスタは保持                    |

| STANDBY     | パワーダウン状態 DMA/DMAMUX は、STANDBYモード終了後に再初期化する必要 がある   |

| SHUTDOWN    | パワーダウン状態 DMA/DMAMUX は SHUTDOWN モード終了後に再初期化する必要 がある |

この表には、電源モードに対応する DMA コントローラと DMAMUX の状態が示されています。

SLEEP モードと低電力 SLEEP モードでは、DMA コントローラと DMAMUX は有効のままであり、たとえば、UART や I2Cで受信した文字をメモリに転送した後に CPU をウェイクアップするためなどに使用できます。