STM32G4システム設定コントローラのこのプレゼンテーションへようこそ。

- STM32G4xxマイクロコントローラは、システム設定レジスタを備えている

- システム設定コントローラの主な目的は以下の通り:

- メモリ領域の再マッピング

- GPIO外部割込みの管理

- 「堅牢性」機能の管理

- CCM RAM書込み保護とソフトウェア消去の設定

- FPU割込み

- I<sup>2</sup>C高速モード・プラスの設定

STM32G4マイクロコントローラは、SYSCFGモジュール内に配置 されたシステム設定レジスタを備えています。

システム設定コントローラーは、以下の機能にアクセスできます。

- メモリ領域の再マップとアドレス0x0000\_0000でアクセス可能 なメモリの選択

- GPIO外部割込みの管理

- 「堅牢性」機能の管理

- CCM RAM書込み保護とソフトウェア消去の設定

- FPU割込み

- I2C高速モードプラスの設定

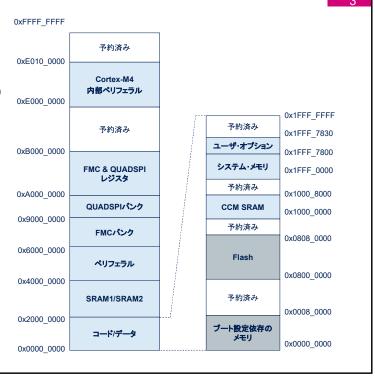

### STM32G474メモリ・マップ

- Flashメモリ:最大512キロバイト、デュアル・バンク

- FB MODE = 0 SYSCFG MEMRMP:

- バンク 1 @0x0800 0000(エイリアス0x0000 0000)

- バンク 2 @0x0804 0000

- FB\_MODE = 1 SYSCFG\_MEMRMP

- バンク 2 @0x0800 0000(エイリアス0x0000 0000)

- バンク 1 @0x0804 0000

- SRAM:128キロバイト3パーツに分割:

- SRAM1: 80キロバイト@2000 0000

- SRAM2: 16キロバイト@0x2001 8000

- CCM SRAM: 32キロバイト@0x1000 0000

- D-codeとl-codeを通じてアクセス

ここでは、STM32G474マイクロコントローラのメモリマップについて 説明します。

STM32G474とSTM32G431の違いは、このプレゼンテーションの後半で説明されています。

Flashメモリのサイズは、デュアルバンク構成で最大512キロバイトです。

FB\_MODEビットは、バンク1と2のアドレスマッピングを決定し、アドレス0にエイリアスされるバンクを選択します。

SRAMの合計サイズは128キロバイトです。それは3つの部分に分かれています:

- SRAM1サイズはアドレス0x2000 0000から80キロバイトです。

- SRAM2サイズはアドレス0x2001 8000から16キロバイトです。

- コア結合メモリ(CCM)SRAMサイズは、アドレス0x1000\_0000から 32キロバイトです。

SRAM1およびSRAM2メモリは、SRAM専用の通常のArm V7-Mメモリ空間に配置され、CCM SRAMはD-codeおよびI-code AHBバスを介してアクセスされます。

このアーキテクチャにより、CCM SRAMおよびSRAM1またはSRAM2 メモリへの同時アクセスが可能になります。

### パフォーマンス向上

- アドレス0x0000 0000再配置オプション

- メインFlashメモリ

- システムFlashメモリ(ブートローダ)

- FMCバンク1(NOR/PSRAMモード)

- SRAM1

- QUADSPI

- ▶ システム・バス・アクセスの代わりのI-Code/D-Codeアクセスによる性能向上

- FB MODE SYSCFG MEMRMP

- スワップFlashメモリ・バンク1&2

アドレス0でのメモリ再配置は、システムバスを使用する代わりに、 専用のI-CODEバスアクセスとD-CODEバスアクセスにより、コー ド実行パフォーマンスを向上させます。

アドレス0のメモリリマップは、アドレス0でアクセス可能なメモリを 選択します。

メインのFlashメモリ、システムFlashメモリ、FMCバンク1、SRAM1、またはQUADSPIのいずれかです。

FMCバンク1は、外部のNOR FlashメモリまたはPSRAMメモリをマッピングします。

システム構成再マップレジスタのFB\_MODEビットでは、Flashメモリバンク1と2の間でスワップが可能です。

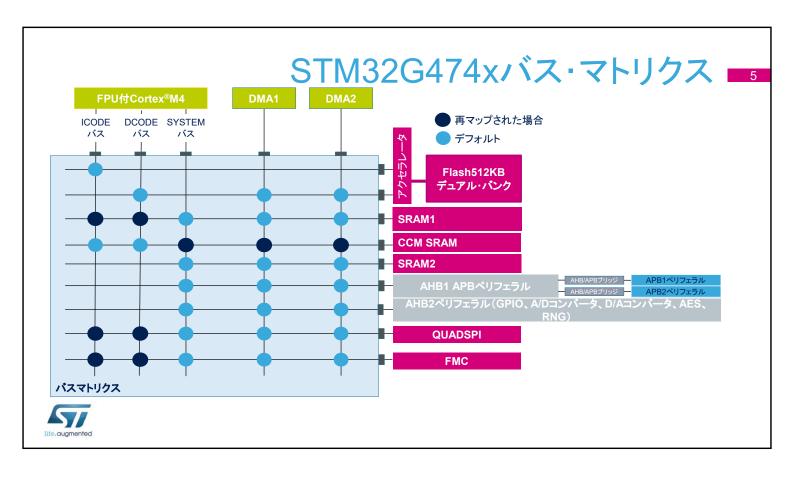

STM32G4バスマトリクスを示しています。

バスマスタは最上部に示され、その3つのAHBマスタインタフェースI-CODE、D-CODE、システムと2つのDMAコントローラを備えたCortex-M4コ アがあり

バススレーブは、内部および外部のメモリとペリフェラルが接続されています。

Flashメモリはアクセラレータを介して読み取られます。

Cortex-M4コアがCODEまたはDATAアドレス範囲内のデータにアクセスする場合、D-CODEバスが使用されます。

Cortex-M4コアがCODEまたはDATAアドレス範囲内の命令にアクセスする場合、I-CODEバスが使用されます。

SRAM1はデフォルトでシステム・バスを介してアクセスされ、パフォーマンスを向上させるためにアドレス0で再配置されるときに、I-CODEバスおよびD-CODEバスを介してアクセスできます。

CCM SRAMメモリは常にIバスとDバスを介してアクセスされ、待機時間が0でコードの実行が可能です。

Quad-SPIおよびFMCバンクはデフォルトでシステムバスを通じて読み取りおよび実行でき、またアドレス0で再配置してパフォーマンスを向上させることができます。

2つのDMAコントローラは、すべてのメモリとペリフェラルにアクセスできます。

### パフォーマンス

|                         | Flashメモリから実行                                |             |                                             |             | SRAMから実行    |             |                              |                                     |

|-------------------------|---------------------------------------------|-------------|---------------------------------------------|-------------|-------------|-------------|------------------------------|-------------------------------------|

|                         | > ARTオン<br>> I-Cache<br>> D-Cach<br>> プリフェ・ | eオン<br>eオン  | > ARTオ:<br>> I-Cache<br>> D-Cache<br>> プリフェ | eオン<br>neオン | > ARTオ:     | 7           | > SRAM1<br>上に<br>コードと<br>データ | > CCM SRAM<br>上にコード<br>> SRAM1上にデータ |

| CoreMark/MHz<br>@150MHz | デュアル<br>パンク                                 | シングル<br>バンク | デュアル<br>バンク                                 | シングル<br>バンク | デュアル<br>バンク | シングル<br>バンク |                              |                                     |

|                         | 3.26                                        | 3.36        | 3.23                                        | 3.32        | 1.05        | 1.47        | 2.37                         | 3.42                                |

| @170MHz                 | 3.23                                        | 3.35        | 3.20                                        | 3.31        | 0.94        | 1.36        | 2.37                         | 3.42                                |

この表では、EEMBC CoreMarkベンチマークを実行しながら、150MHzと170MHzでのコード実行パフォーマンスの比較です。

CCM SRAMでコードを実行し、データをSRAM1に配置すると、最大のパフォーマンスが得られます。SRAM1がアドレス0で再配置された場合、SRAM1のコードとSRAM2のデータを使用して最大のパフォーマンスに到達することもできます。

Flashメモリから実行すると、ARTアクセラレータが有効になると CoreMarkの最大パフォーマンスに達し、170MHzで8ウェイト、 150MHzで7ウェイト必要とするFlashアクセス時間のためにパ フォーマンスが低下することはほとんどありません。

プリフェッチバッファを有効にすると、シングルバンクモードの場合は3.36CoreMark / MHzというスコアがやや高くなります。

## STM32G431デバイスとの違い **■**7

- 多層AHBマトリクス

- QUADSPIスレーブ無し

- FMCスレーブ無し

- SRAMサイズ

• SRAM1: 16キロバイト、SRAM1全体でパリティ・チェック

SRAM2: 6キロバイト

• CCM SRAM: 10キロバイト、CCM SRAM全体でパリティ・チェック

- メモリマッピング

- CCM SRAMはアドレス0x2000\_5800でエイリアスされ、SRAM1/SRAM2による連続アドレス 空間が可能

- Flash

- シングル・バンクFlash

STM32G431とSTM32G474マイクロコントローラの主な違いを示しています。

STM32G431ラインには、クアッドSPIおよびFMCユニットは含みません。

STM32G431ラインは、16キロバイトSRAM1と10キロバイトCCM SRAMの両方がパリティをサポートし、6キロバイトSRAM2という SRAMメモリが小さくなっています。

マッピングに関しては、CCM SRAMはアドレス0x2000\_5800でエイリアスされ、SRAM1およびSRAM2メモリを持つ連続RAMアドレス範囲が可能になります。

最後に、STM32G431はシングルのフラッシュメモリバンクを持っています。

## ブートモード

| BOOT_LOCKビット | nBOOT1ビット | BOOT0ピン | nSWBOOT0ビット | nBOOT0ビット | ブートモード・エリアの選択   |

|--------------|-----------|---------|-------------|-----------|-----------------|

| 0            | Х         | 0       | 0           | х         | メインFlashメモリ     |

| 0            | 1         | 1       | 0           | х         | システム・メモリ        |

| 0            | 0         | 1       | 0           | х         | 内蔵SRAM          |

| 0            | Х         | Х       | 1           | 1         | メインFlashメモリ     |

| 0            | 1         | Х       | 1           | 0         | システム・メモリ        |

| 0            | 0         | Х       | 1           | 0         | 内蔵SRAM          |

| 1            | х         | х       | Х           | Х         | メインFlashメモリ(強制) |

- 他のオプションビットに関係なくBOOT LOCKビットはFlashメモリからブート

- SYSCFG\_MEMRMP[MEM\_MODE]フィールドは、ソフトウェアによって物理的な再配置を選択するために使用され、BOOTピンとオプションビット設定をバイパスする

• リセット後これらのビットはBOOT0ピン(またはオプションビットnSWBOOT0)とBOOT1オプションビットで選択された値を取る

BOOT0ピンまたはnBOOT0ビット(nSWBOOT0ビットがクリアされている場合)とnBOOT1ビットによって選択される3つのブートモードがあります。

BOOT0ピンがローレベルになると、STM32G4マイクロコントローラはユーザーフラッシュメモリから起動します。

BOOT0ピンがハイレベルになると、nBOOT1ビットによってブートモードが決まります。nBoot1が1の場合、ブートは、ST独自のブートコードを含むシステムメモリから実行されます。

もう1つのオプションは、SRAM1メモリ領域からの起動です。

BOOT\_LOCKビットが1の場合、ブートはメインFlashメモリから強制的に実行されます。

ソフトウェアは、SYSCFG\_MEMRPレジスタのMEM\_MODEフィールドをプログラミングすることにより、アドレス0に表示されるメモリを動的に選択できます。

このフィールドのデフォルト値は、ブート・ピンの状態および関連 するオプション・バイト値、BOOT\_LOCKおよびnSWBOOT0によっ て異なります。

# ブートローダ

| a |  |

|---|--|

| プロトコル | 1/0とコメント                                                    |

|-------|-------------------------------------------------------------|

| USART | USART1 PA9/PA10ピン<br>USART2 PA2/PA3ピン<br>USART3 PC10/PC11ピン |

| USB   | USB DFUインタフェース PA11/PA12ピン                                  |

| SPI   | SPI1 PA4/PA5/PA6/PA7ピン<br>SPI2 PB12/PB13/PB14/PB15ピン        |

| I2C   | I2C2 PC4/PA8ピン<br>I2C3 PC8/PC9ピン<br>I2C4 PC6/PC7ピン          |

オンチップのブートローダを使用すると、ペリフェラルのシリアル 通信を介してSTM32G4にダウンロードされたイメージでFlashメモ リをプログラムできます。

サポートされているプロトコルは、USART、USB、CAN、SPI、およ びľCです。

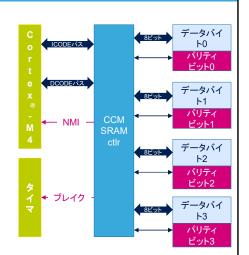

## CCM SRAM機能

#### 10

### パフォーマンス、整合性、セーフティ(Class B、SIL)

- D-codeとI-codeを介したアクセスを持つ32キロバイト CCM SRAM:

- 再配置を使用せず、コード実行を最大パフォーマンスに

- HWパリティチェック:ワードあたり4ビット

- SRAM PEの有効 ユーザ・オプション・バイト

- パリティ・エラーでNMIの生成

- オプションのブレイク・トゥ・タイマ、システム障害時のHRTIM停止

- デフォルトで無効

- パリティ・チェックはSRAM1の最初の32キロバイトにも実装

CCM SRAMの32キロバイトは、パフォーマンス、整合性、セーフティに特に適しています。

CCM SRAMは、D-CODEバスとI-CODEバスを介してアクセスされ、 メモリの再配置せずにゼロウェイトでのコード実行が可能になりま す。

CCM SRAMはパリティチェックをサポートします。データバスの幅は32ビットで、たとえばクラスBまたはSIL規格によってメモリの堅牢性を高めるために、4ビットがパリティチェック(1 ビット/バイト)に使用できます。クラスBおよびSILは機能安全です。クラスBは家電製品用、SILは安全整合性レベルです。

パリティビットはSRAMに書き込むときに計算され、格納されます。 次に、読み取り時に自動的にチェックされます。少なくとも1ビットで 障害が発生すると、ノンマスカブル割り込み(NMI)が生成されます。 同じエラーは、タイマのブレーク入力とHRTIMシステム障害入力に もリンクできます。

パリティチェックは既定で無効になっています。

SRAM1の下位32キロバイトもパリティ生成と検査をサポートします。

### セキュリティで保護されたSRAM

- 1キロバイト単位の書込み保護機能

- SYSCFG SWPR書き込み保護レジスタでプログラム可能

- 32ビット、キロバイトあたり1ビット

- RDPによる読出し/書込み保護

- ▶ RDPがレベル1からレベル0に変化した場合に消去

- ソフトウェア・リセットとシステム・リセット時のハードウェア・リセット(オプション)

- SYSCFG SCSRのレジスタCCMERビットにセットされると消去

- ユーザーオプションのバイトのCCMSRAM\_RSTを用いたシステム・リセットで消去

CCM SRAMは、セキュアなアプリケーションにも適しています。 CCM SRAMは1KB単位で書込み保護可能です。

また、RDPオプション・バイトによって読出し保護を行うこともできます。保護時にはCCM SRAM、およびFlashメインメモリとバックアップレジスタは、デバッグモードまたはブートRAMまたはブートローダからコードが実行されている場合に、完全にアクセスできません。

読み出し保護がレベル1からレベル0に変更されると、CCM SRAMは消去されます。

CCM SRAMは、CCM SRAMシステム設定コントローラおよびステータスレジスタにCCMERビットを設定することにより、ソフトウェアによって消去できます。

CCM SRAMは、ユーザオプションバイトのCCMSRAM\_RSTオプションビットに応じて、システムリセットを使用して消去することもできます。

### 安全性と堅牢性

・ 設定レジスタ2の安全性と堅牢性の機能

| SYSCFG_CFGR2フィールド      | 説明                                                  |  |  |  |

|------------------------|-----------------------------------------------------|--|--|--|

| SPF(SRAMパリティ・フラグ)      | SRAMおよびCCM SRAMパリティ・エラーが検出された場合にセット                 |  |  |  |

| ECCL(ECCロック)           | =0:タイマの中断またはHRTIMの障害はない                             |  |  |  |

| PVDL(PVDロック)           | =1:ECC、PVD、SRAMパリティ、またはプロセッサのロックアップ状態が              |  |  |  |

| SPL(SRAM1とCCMパリティ・ロック) | 原因でTIM1/8/15/16/17/20ブレーク入力とHRTIMシステム障害入力のアサーションが発生 |  |  |  |

| CLL(Cortex®-M4ロックアップ)  |                                                     |  |  |  |

• パワーエレクトロニクスの制御に使用するタイマは、STM32G4マイクロコントローラで検出された回復不能な障害の場合に安全な状態に設定可能

システム設定レジスタ2には、CCM SRAMパリティエラーフラグなどの安全性と堅牢性に関連するコントロールビットとステータスビット、およびエラー検出イベントをタイマのブレーク入力に送るコントロールビットが含まれています。

これにより、アプリケーションのクラッシュ時にタイマ出力を既知の状態に配置できます。プログラムが完了すると、次のシステムがリセットされるまで、接続はロックされます。これらの内部イベントには、Flashエラーコード修正イベント、電源電圧検出器イベント、SRAM1およびCCM RAMパリティエラーイベント、およびCortex M4ハードフォールトが含まれます。

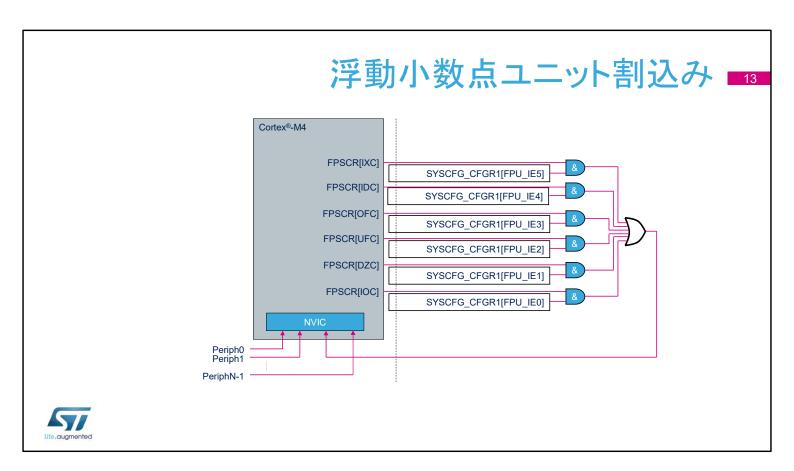

Cortex-M4コアに存在する浮動小数点ユニット(FPU)は、FPv4アーキテクチャに従って、各命令に必要なFPSCRレジスタの累積例外ステータスフラグを設定します。

FPUはユーザモードトラップをサポートしません。この例外は、 FPSCRのゼロ読み取りビットを有効にし、書き込みは無視されま す。

このプロセッサーには、累積例外フラグの1つの状況をそれぞれ 反映する6つの出力ピン(IXC、FC、OFC、DZC、IDC、IOC)もあり ます。

SYSCFG\_CFGR1レジスタ内の対応するイネーブルビットが設定されている場合、フラグが設定されると割り込みが要求されます。 割り込みサービスルーチンは、どのフラグが設定されているかを決定します。 • STM32G4の4つのI<sup>2</sup>Cコントローラは3つの速度をサポート

| モード           | ビットレート      | 20mA出力ドライブI/O |

|---------------|-------------|---------------|

| 標準モード(Sm)     | ≤100キロビット/秒 | No            |

| 高速モード(Fm)     | ≤400キロビット/秒 | No            |

| 高速モードプラス(Fm+) | ≤1メガビット/秒   | Yes           |

- エクストラハイドライブはSYSCFGモジュールによって制御される

- I<sup>2</sup>Cが選択されていない他の機能でも有効にすることが可能

STM32G4マイクロコントローラに組み込まれた4つのI2Cコント ローラは、3つの速度をサポートします。

- 標準モード、最大ビットレートは100キロビット/秒

- 高速モード、最大ビットレートは400キロビット/秒

- 高速モードプラス、最大ビットレートは1メガビット/秒 高速モードプラスは、SYSCFGモジュールで有効にされ、かつ高 いドライブ機能を必要とします。

ハイドライブはピンレベルで制御されるため、他の代替機能でも 使用できます。

## I<sup>2</sup>C I/O高速モード ■15

| ピン                       | I <sup>2</sup> C代替え機能 | I <sup>2</sup> C FM+モード・イネーブル |  |

|--------------------------|-----------------------|-------------------------------|--|

| PA13、PA15、 <b>PB8</b>    | I2C1_SCL              | SVSCEC CECRATICOA EMPI-A      |  |

| PA14、 <b>PB7、PB9</b>     | I2C1_SDA              | SYSCFG_CFGR1[I2C1_FMP]=1      |  |

| PA9、PC4、PF6              | I2C2_SCL              | SYSCFG_CFGR1[I2C2_FMP]=1      |  |

| PA8、PF0                  | I2C2_SDA              |                               |  |

| PA8、PC8、PF3、PG7          | I2C3_SCL              | CVCCEC CECD4U2C2 EMDI-4       |  |

| PB5、PC9、PC11、PF4、PG8     | I2C3_SDA              | SYSCFG_CFGR1[I2C3_FMP]=1      |  |

| PA13、PC6、PF14、PG3        | I2C4_SCL              | SVSOFO OFORGINGA FMDI-4       |  |

| <b>PB7</b> 、PC7、PF15、PG4 | I2C4_SDA              | SYSCFG_CFGR1[I2C4_FMP]=1      |  |

| ピン  | 代替機能                                                                                                                                          | FM+モード・イネーブル                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| PB6 | TIM16_CH1N、TIM4_CH1、TIM8_CH1、TIM8_ETR、TIM8_BKIN2、USART1_TX、COMP4_OUT、CAN2_TX、LPTIM1_ETR、HRTIM_SCIN、HRTIM_EEV4、SAI_FS_B、EVENTOUT、UCPD_CC1      | SYSCFG_CFGR1[I2C_PB6_FMP]=1 |

| PB7 | TIM17_CH1N、TIM4_CH2、TIM8_BKIN、TIM3_CH4、I2C4_SDA、I2C1_SDA、USART1_RX、COMP3_OUT、CAN2_TXFD、LPTIM1_IN2、FMC_NL、HRTIM_EEV3、UART4_CTS、EVENTOUT、PVD_IN | SYSCFG_CFGR1[I2C_PB7_FMP]=1 |

| PB8 | TIM16_CH1、TIM4_CH3、SAI_CK1、 <b>I2C1_SCL</b> 、USART3_RX、COMP1_OUT、CAN1_RX、TIM8_CH2、TIM1_BKIN、HRTIM_EEV8、SAI_MCLK_A、EVENTOUT                    | SYSCFG_CFGR1[I2C_PB8_FMP]=1 |

| PB9 | TIM17_CH1、TIM4_CH4、SAI_D2、 <b>I2C1_SDA</b> 、IR_OUT、USART3_TX、COMP2_OUT、CAN1_TX、TIM8_CH3、TIM1_CH3N、HRTIM_EEV5、SAI_FS_A、EVENTOUT                | SYSCFG_CFGR1[I2C_PB9_FMP]=1 |

各I2Cコントローラは、SYSCFG CFGR1レジスタに高速モードとド ライブ許容モードを有効にする制御ビットを持っています。

各ピンPB6、PB7、PB8、PB9には、選択されたペリフェラルに依 存せず、高速モードプラス向けのドライブ能力をアクティブにする 独自のI2C PB FMP制御ビットを持っています。

GPIOピンでFM+モードがアクティブ化されると、GPIOx OSPEEDR レジスタにプログラムされたGPIOの速度設定は無視されます。

場合によっては、FM+モードをアクティブ化する方法が2つありま す。たとえば、I2C1 FMPまたはI2C PB8 FMPビットが SYSCFG\_CFGR1レジスタ内の1に設定されている場合、PB8ピン はFM+をサポートI2C1\_SCLとして設定されます。

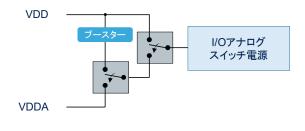

# GPIOアナログスイッチ 16

| VDD     | VDDA    | BOOSTEN                                              | ANASWVDD                    |

|---------|---------|------------------------------------------------------|-----------------------------|

| -       | > 2.4 V | 0                                                    | 0<br>▶ VDDAが提供するI/Oアナログスイッチ |

| > 2.4 V | < 2.4 V | ► I/OアナログスイッチはVDDA電圧で供給                              | 1<br>➤ VDDが提供するI/Oアナログスイッチ  |

| < 2.4 V | < 2.4 V | 1<br>▶ I/Oアナログスイッチは専用の電圧ブースタ<br>(VDDによって供給)によって供給される | 0<br>▶ ブースタが提供するI/Oアナログスイッチ |

SYSCFG\_CFGR1レジスタの2ビットBOOSTENとANASWVDDは、I/Oアナログスイッチの電源を選択するために使用されます。これらは、VDDとVDDAの電源の電圧に応じて初期化する必要があります。

VDDA電圧が2.4Vより大きい場合、I/OアナログスイッチはVDDAによって電源を供給する必要があります。

VDDA電圧が2.4Vより低く、VDDが2.4Vより高い場合、I/OアナログスイッチはVDDによって電力を与えられなくてはいけません。 VDDとVDDAの両方の電圧が2.4Vより低い場合、I/OアナログスイッチはVDDブースターの出力によって電源を供給されます。

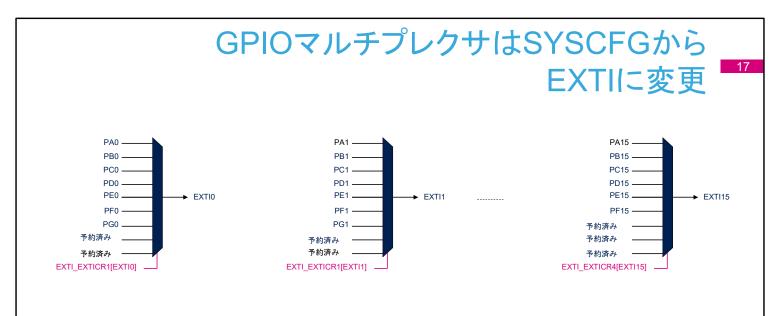

・異なるポートに同じ番号を持つ2つ以上のGPIOパッドは、EXTI構成可能イベントと同時に選択できない

STM32G4マイクロコントローラには7つのIOポートがあり、ポートAからFは16ピン幅のポート、ポートGは11ピン幅のポートです。 GPIOポートに関連する16のEXTI構成可能イベントのそれぞれは

独立したマルチプレクサを持っています。

EXTIマルチプレクサ出力は、EXTI\_IMRおよびEXTI\_EMRレジスタで定義されたマスクとは別に使用できます。

- 詳細は、以下を参照してください。

- STM32G4マイクロコントローラ・リファレンス・マニュアル

- このペリフェラルに関連するペリフェラル・トレーニング

- 拡張割り込みおよびイベント・コントローラ(EXTI)

- Arm Cortex®-M4コア(CM4)

- メモリ保護(MEMPROTECT)

- タイマ(TIM)

- 高分解能タイマ(HRTIM)

システム設定モジュールの詳細については、STM32G4マイクロコントローラリファレンスマニュアルを参照してください。 必要に応じて、次のトレーニングも参照してください。

- 拡張割り込みおよびイベント・コントローラ

- アームコルテックス-M4コア

- タイマ

- ・ 高分解能タイマ