こんにちは、STM32マイクロコントローラに内蔵されて4いる高機能、汎用および基本タイマについてのプレゼンテーションへようこそ。

タイミングに関連するあらゆるイベントの処理、波形の生成、入力信号のタイミング特性の測定などに役立つ主な機能をカバーしています。

### 概要 複数のタイマ・ユニットがタイミング・リソー スを提供 内部(トリガ、タイムベース) • 入出力用の外部: • 波形生成用(PWM) • 信号のモニタリングまたは測定用(周波数またはタイ 出力 アプリケーション側の利点 ► CH1 • 汎用性の高い動作モードでのCPU負荷を軽減し、回 → CH2 路との接続ニーズを最小限に すべてのタイマ・インスタンスに対する単一のアーキテ クチャにより、スケーラビリティと使いやすさを実現 → CHn

モータ制御およびデジタル電力変換アプリケーション

STM32は、ソフトウェアまたはハードウェア・タスクのタイミングリソースを 提供する複数のタイマを内蔵します。

にも対応

ETR

入力

CH2

CH1

CHn

CK\_INT →

ITR0-1

トリガ 出力

自動リロード

トリガ/クロック コントローラ

16ビットプリスケーラ

+/-16/32ビットカウンタ

キャプチャ・コンペア

ソフトウェアタスクは、主にタイムベースの提供、タイムアウトイベント生成、およびタイムトリガで構成されます。

ハードウェアタスクはI/Oに関連しており、タイマは出力に波形を生成し、 入力信号パラメータを測定し、入力上の外部イベントに反応することが できます。

STM32タイマは非常に汎用性が高く、接続回路の必要性を最小限に抑えながら、CPUを反復的でタイムクリティカルなタスクから解放し、インタフェース回路の必要性を最小限に抑えます。

すべてのSTM32タイマ(低電力タイマと高分解能タイマを除く)は、同じスケーラブルなアーキテクチャに基づいています。

タイマの動作原理がわかれば、タイマのどれに対しても有効です。

このアーキテクチャには相互接続機能が含まれており、複数のタイマをより大きな構成に組み合わせることが出来ます。

最後に、一部のタイマは、モータ制御と照明やデジタルスイッチング電源などのデジタル電力変換のための特定の機能を備えています。

### 主な機能・

- すべてのタイマは同じアーキテクチャに基づいており、次の点でスケーラブル

- 入力/出力の数(0から11まで)

- タイマ1の11の場合:TIM1\_ETR、TIM1\_BKIN、TIM1\_BKIN2、TIM1\_CH1、TIM1\_CH1N、TIM1\_CH2、TIM1\_CH2N、TIM1\_CH3、TIM1\_CH3N、TIM1\_CH4、TIM1\_CH4N

- 分解能(16ビットまたは32ビット)

- 機能(PWMモード、DMA、同期、アップ/ダウンカウント)

- 複数のタイマをリンクおよび同期可能

- 各タイマ・チャネルは、入力または出力として個別設定可能

- 他のペリフェラルと複数の相互接続が可能で、監視またはトリガ目的に利用可能

STM32タイマの主な機能は次のとおりです。

すべてのタイマは同じアーキテクチャに基づいており、このプレゼンテーションの後半に記載されているいくつかの派生製品で利用できます。 タイマは主に、I/Oのない純粋なタイマベースから11個のI/Oを備えた高度な制御可能なバージョンまで、それぞれ入力と出力の数が異なります。 ほとんどのタイマは16ビットカウンタを備えていますが、一部には32ビットカウンタがあります。

最小のタイマ(DMA、同期、アップ/ダウンカウントモードなど)には、一部の機能が存在しない場合があります。

ほとんどのタイマはリンクして同期させることにより、より大きなタイムベースタイマを構築したり、同期した波形の数を増やしたり、複雑なタイミングや波形を処理することができます。

タイマ内では、各チャネルを入力(通常はキャプチャ用)または出力(通常はPWM用)として個別に構成できます。

タイマは相互接続マトリックスを使用して、例えば、A/Dコンバータ変換を開始したり、内部クロックを監視したりするために、他のペリフェラルのトリガとして機能します。

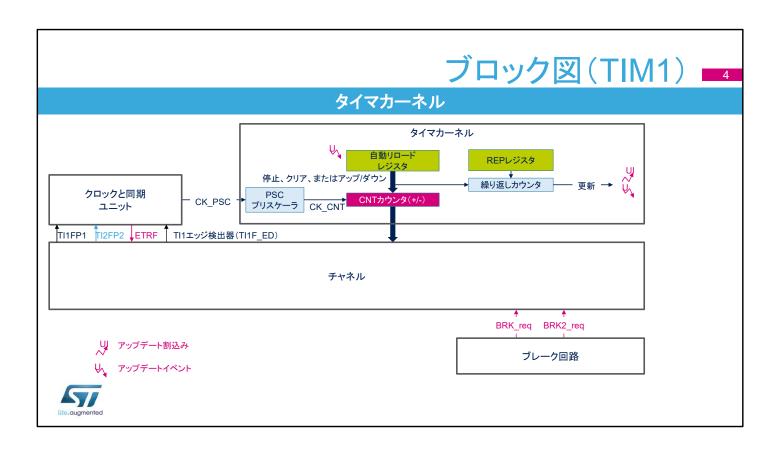

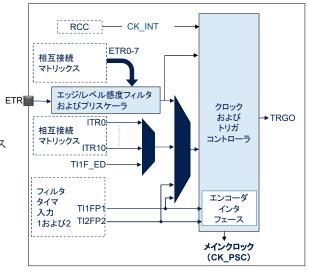

このスライドは、TIM8およびTIM20と同じアーキテクチャーを持つTIM1タイマの ブロック図を示しています。

タイマカーネルは、16ビットのアップ/ダウンカウンタで構成され、カウント期間を プログラムするための自動リロードレジスタと組み合わせたものです。

繰り返しカウンタが使用される場合、繰り返しカウンタレジスタでプログラムされた回数に対してアップカウントが繰り返された後に更新イベントが生成されます。 それ以外の場合は、各カウンタのオーバーフロー時に更新イベントが生成されます。

コンフィギュレーションレジスタの内容を更新するために、プリロードレジスタが 実装されています。

プリロードレジスタの内容は、恒久的に、または各更新イベントごとにシャドウレ ジスタに転送されます。

たとえば、この同期メカニズムを使用して、この図に示されているオートリロードレジスタの内容を更新できます。

タイマブロックの他のユニットは次のとおりです。

- タイマクロックとトリガの提供を担当するクロックと同期ユニット

- 担当チャネル、入力キャプチャ、出力コンペア、PWM生成、およびワンパルスモード出力

- タイマの出力信号をユーザーが安全に選択可能な構成にするためのブレーク回路を担当

これらの他のユニットについては、次のスライドで説明します。

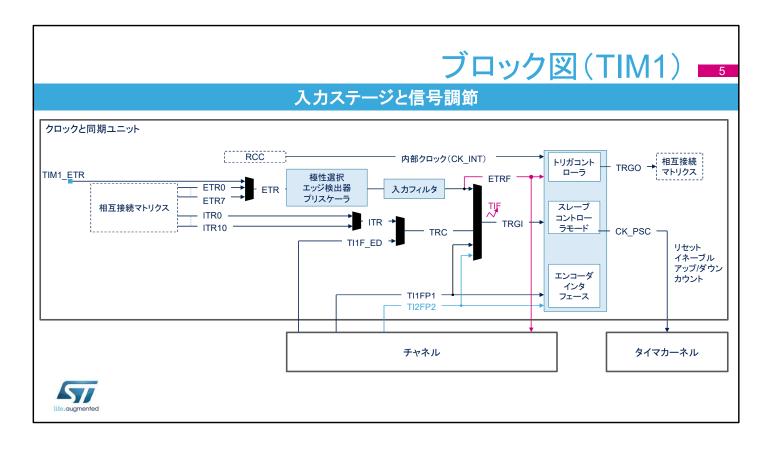

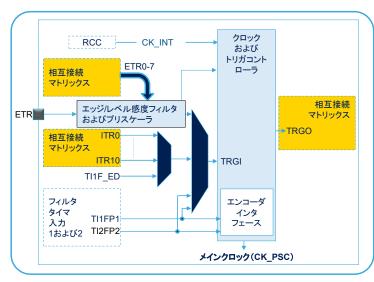

クロックとの同期ユニットは、CK\_PSCと呼ばれるタイマカーネルに基準 クロックを提供します。

カウンタクロックは、以下のクロックソースによって提供されます。 内蔵クロック(CK INT)

- 外部クロックモード1:外部入力端子、選択された入力または内部トリガの立ち上がりまたは立ち下がりエッジをカウントします。

- 外部クロックモード2:外部トリガ入力ETRまたはトリガ

- チャネルからのTI1FP1とTI2FP2をベースにしたエンコーダ・モード ETRは、A/Dコンバータアナログ・ウォッチドッグ、コンパレータ、または ETR入力によってアサートされるトリガです。

ITRは、他のタイマによってアサートされることができるトリガです。 内部トリガのインとアウトは相互接続マトリックスに接続されています。 関連するプレゼンテーションを参照してください。

選択されたトリガ入力(TRGI)の立ち上がりエッジでTIFフラグがセットされます。

1つのタイマがマスタモードで設定されている場合、スレーブモードで設定されている別のタイマのカウンタをリセット、スタート、ストップ、クロックすることができます。

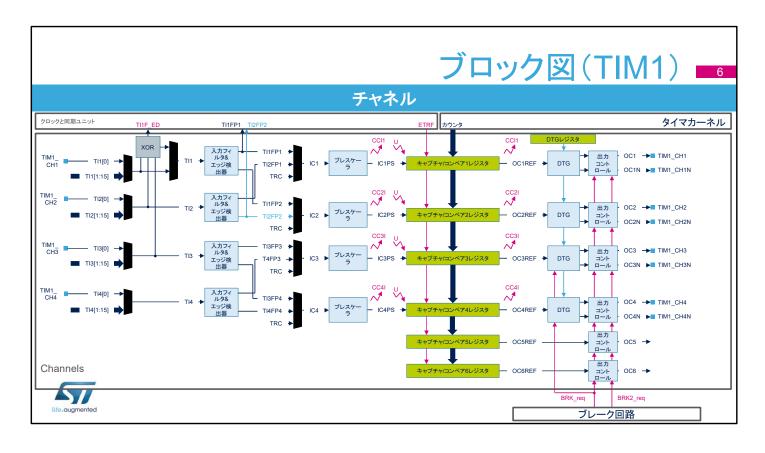

TIM1は、次の6つの独立したチャネルをサポートします。

- 入力キャプチャ(チャネル5と6を除く)

- 出力比較

- PWM生成(エッジおよびセンターアライメントモード)

- ワンパルスモード出力

キャプチャまたはコンペアイベントが発生すると、対応するCCIフラグが 設定されます。

左側に表示されているのは入力ステージと入力コンディショニング回路で、右側には出力ステージがあります。

なお、TIM1CH1~4ピンは両側に表示され、入力と出力の両方が可能であることを示しています。

チャネル1~4はピンで出力可能で、チャネル5とチャネル6はマイクロコントローラ内でのみ利用可能です(例えば、複合波形生成やA/Dコンバータトリガ用)。

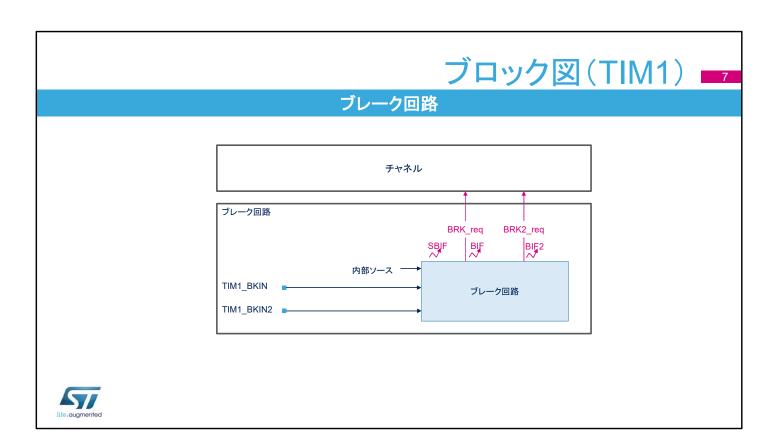

タイマ1は、ブレークイベントが発生したときに、チャネル出力を自動的に所定の状態に設定するために使用できるブレーク入力をサポートします。

タイマ1は、チャネル1~4のPWM補完出力にデッドタイムを挿入するデッドタイムジェネレータユニット(DTG)もサポートしています。

このブレーク機能の目的は、PWM信号によって駆動される電源スイッチを保護することです。

2つのブレーク入力は、通常、パワーステージと3相インバータの故障出力に接続されます。

このブレーク回路がアクティブになると、PWM出力をシャットダウンし、事前に定義された安全な状態に強制的に遷移します。 出力のシャットダウンをトリガするために、多数の内部MCUイベントを選択することもできます。

ブレークは2つのチャネルを備えています。

ブレークチャネルは、システムレベルの障害(クロック障害、パリティエラーなど)とアプリケーション障害(入力ピンと内蔵コンパレータ)の両方を収集し、デッドタイムの後、出力を事前に定義されたレベル(アクティブまたは非アクティブ)に強制的に遷移することができます。

ブレークチャネル2は、アプリケーション障害のみを収集し、出力を非アクティブ状態に遷移することができます。

# タイマ・クロッキング・スキーム

#### 複数の内部または外部クロッキング・オプション

- CK INT内部クロックはAPBクロックPCLK

- 外部クロッキングは以下のことが可能

- 他のオンチップ·タイマ(ITRx入力)への入力

- 入力ピン1および2(TI1、TI2)への入力

- デジタル・フィルタとプログラム可能なエッジ感度を含む

- 多目的外部トリガ入力(ETR)

- デジタル・フィルタ、プログラマブル・エッジ感度、基本的なプリスケーラ(/2、/4、/8)を搭載

- エンコーダからの直交信号

- エッジ検出器(TI1F\_ED)

高機能タイマと汎用タイマは、複数のクロッキングオプションを備えています。 タイマチェーンを担当するクロックおよび同期ユニットは、カウンタのクロックを処理します。

デフォルトのクロックは、リセットとクロックコントローラから供給されます。

このタイマクロックCK INTはAPBクロックPCLKです。

外部タイマクロックにより、外部イベントをカウントしたり、カウント期間を外部で調整 したりすることができます。

クロックソースは、11の内部トリガ入力(ITR0~ITR10)のうちの1つを使用して、他のオンチップタイマから供給することができます。

入力ピン1と2は外部クロックとしても使用でき、スプリアスイベントを除去するための デジタルフィルタをオプションで追加することができます。

外部トリガ入力(ETR)は、デジタルフィルタ、プログラム可能なエッジ感度、および必要に応じて入力信号の周波数を低減するための第1の基本的なプリスケーラステージを備えた外部クロックとして構成することができます。

外部トリガはETRピンに加えてA/Dコンバータウォッチドッグとコンパレータによって生成することができます。

TI1F\_EDエッジ検出器入力は、タイマクロックとしても使用できます。

TI1F信号の立ち上がりと立ち下りの両方のエッジでパルスが生成されます。

外部クロック(受信クロック周期ごとに2回カウント)で周波数倍増器としての役割を果たすこともできます。

最後に、エンコーダからの信号は、本プレゼンテーションで後述するように、クロックおよびカウント方向を設定することができます。

# カウント期間の管理

#### 細かく正確なピリオド設定

- 各タイマには16ビットのリニアプリスケーラが内蔵 (1,2,3...65536)

- 自動リロード・レジスタは、カウント期間を定義

- オーバーフロー/アンダーフローで更新イベント(割込みまたはDMA)が発行

- プリロードからシャドウへのレジスタ内容の転送をトリガ(プリスケーラ、ピリオド、コンペア)

- 正確なピリオド変更(オーバーフロー時のみプリスケーラが更新される)

- コンペア・レジスタ更新時のグリッチレス動作

- 一部のタイマでは、更新割込みの発生率を繰り返しカウンタで調整することが可能

その他の更新イベントは、カウンタが再読み込みされるたびに発生

ife, augmented

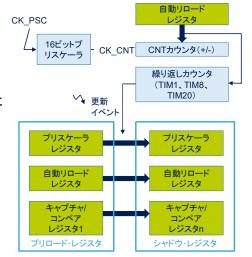

このスライドでは、タイマのカウント期間を調整する方法を説明しています。

各タイマは、クロックを1から65536までの任意の整数で割ることができるリニアクロックプリスケーラを内蔵しています。

したがって、カウントペースは正確に調整することができます。

たとえば、APBクロックが64MHzの場合、64で除算すると、正確な1MHzカウントレートが得られます。

自動リロードレジスタは、カウント期間を定義します。

ダウンカウントモードでは、カウンタがアンダーフローになると、カウンタは周期値で自動的に 再ロードされます。

アップカウントモードでは、カウンタは自動リロード値を超えるとロールオーバーされ、リセットされます。

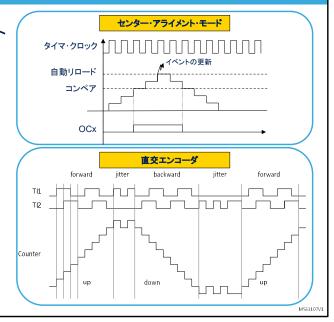

センターアラインメントモード(アップ/ダウンカウント)では、カウンタは0からオートリロード値からマイナス1までカウントし、カウンタオーバーフローイベントを発生させ、次にオートリロード値からマイナス1までカウントし、カウンタアンダーフローイベントを発生させます。その後、0からのカウントを再開します。

カウンタがアンダーフローまたはオーバーフローし、新しいピリオドが開始されると、更新イベントが発行されます。

タイマパラメータをその周期に同期して調整するために使用される割り込みやDMAリクエストをトリガし、リアルタイム制御に役立ちます。

この更新イベントは、複数のパラメーター、特にクロックプリスケーラ、自動リロード値、コンペアレジスタ、およびPWMモードに対して、プリロードからシャドウレジスタへの転送をトリガします。

16ビットのプログラム可能な繰り返しカウンタにより、割込み発行レートをカウント期間から切り離すことができ、例えば、1回目、2回目、3回目、256回目までのPWM期間ごとに1つの割り込みを発生させることができます。これは、高いPWM周波数を扱う場合に特に便利です。

# カウント・モード

### インクリメンタル/直交エンコーダおよびモータ駆動アプリケーションのサポート

- アップカウントとダウンカウント・モードをサポート

- TIM1~5/8/20

- センター・アライメントPWM生成

- オーバーフローとアンダーフローの方向変更

- 電気モータの音響ノイズを低減

- 直交エンコーダの組み込みサポート

- ロータリ・エンコーダ/デジタル・ポテンショメータ

- 位置センサ

- タイマで直接角度の読み取りを可能に

STM32タイマの中には、アップ/ダウンカウントモードを備えているものがあります:高機能タイマ1/8/20と汎用タイマ2/3/4/5です。

カウントの方向は、ソフトウェアでプログラムしたり、センターアラインド PWMモードでタイマが自動管理したりすることができます。

このモードでは、カウンタのオーバーフロー、アンダーフロー時に自動的にカウント方向が変化します。

特定のPWMスイッチング周波数に対して、このモードは、有効電流リップル周波数を2倍にすることで音響ノイズを低減し、パワーステージのスイッチング損失とノイズの間で最適なトレードオフを提供します。

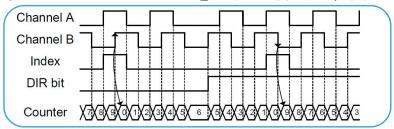

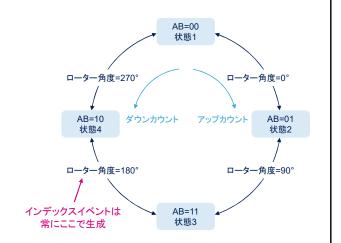

タイマがエンコーダーモードの場合、カウント方向も自動的に処理できます。

直交エンコーダは、電動モータの高精度ロータ位置センシングやデジタルポテンショメータに通常使用されます。

直交エンコーダセンサ(インクリメンタルエンコーダとも呼ばれる)の2つの出力から、タイマは各アクティブエッジのクロックを抽出し、2つの入力信号間の相対的な位相シフトに応じてカウント方向を調整します。タイマカウンタは、このようにしてモータまたはポテンショメータの角度位置を直接保持します。

#### カウント・モード

- x1エンコーディング・モードの追加

- 高速回転アプリケーションでのCPU負荷を減少

• スレーブ・モード選択プリロードにより、実行時エンコーダ・モードの更新が可能

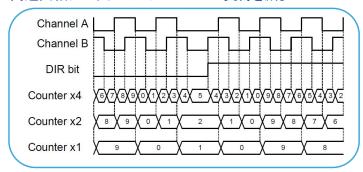

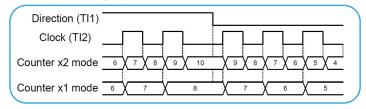

STM32G4に存在するタイマは、エンコーダインタフェースが使用されるときに新しいカウントモードを実装します。

x2、x4モードに加えて、x1モードにも対応しています。

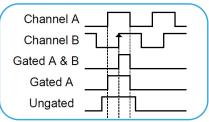

タイミング図に示すように、x1モードでは、方向に応じて、1つの クロックエッジでカウンタ値が更新されます。

ここでは、DIRが0に等しい場合はチャネルAの下向きのエッジが使用され、DIRが1に等しい場合はチャネルAの立ち上がりエッジが使用されます。

実行時にエンコーダモードを切り替える必要がある場合があります。

これは、一般的に高速で行われ、x4からx2からx1モードに切り替えることで、更新割込みレートを低下させることができます。このため、モードを選択するSMSフィールドをプリロードできます。

### 2つの新しいエンコーダ・モード

- インクリメンタル・エンコーダ(モータ制御、デジタル・ポテンショ・メータ)のサポート強化

- クロックプラス方向

• 方向クロック

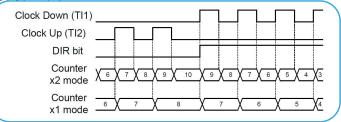

直交エンコーダモードに加えて、タイマはエンコーダの他の2種類のサポートを提供しています。

上のタイミング図に示す「クロックプラス方向」モードでは、TI1 入力で方向を強制的に設定しながら、TI2でクロックを1つのラインで供給します。

下のタイミング図に示す「方向クロック」モードでは、アップカウントのクロックラインとダウンカウントのクロックラインが1本ずつあるように、方向に応じて1本ずつ2本のラインでクロックが用意されています。

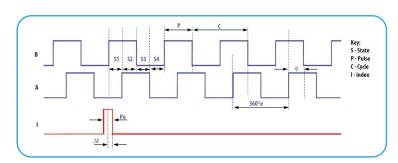

### エンコーダ・インデックス

• 2つのチャネルAとBに加えて、インデックス(ゼロとも呼ばれる)パルスが利用可能で、これは1回転に1回発生し、通常は機械の基準運転(ゼロポイント較正)に使用可能

• インデックスを使用しない場合、シャフトの絶対位置には外部の割込みとソフトウェアが必要であり、 CPUの負荷が増加

モータの駆動にはエンコーダの2種類があります。

- インクリメンタルエンコーダは基準位置を提供しません。

- アブソリュートエンコーダは、絶対基準位置を示すインデックス信号を提供します。

インデックス信号でカウンタをリセットすることができます。 インデックス信号はTIMx\_ETR入力に接続する必要があります。 デジタル入力フィルタを使用してフィルタリングすることができ ます。

インデックス機能付きエンコーダには3つの出力があります。カウンタとインデックスのインクリメント/デクリメントを制御するために使用されるAとBで、1回転に1回アサートされます。

タイミング図では、シャフトが特定の位置に到達したときにゼロパルスが発生します。

明示的なインデックスがないと、インデックスを計算するために割り込みやソフトウェアが必要となり、CPUの負担が大きくなります。

エンコーダのインデックスのハードウェア・サポート

すべてのエンコード・モードをサポート(以下の直交モード)

任意のゲート・オプションをサポート

life, augmented

インデックス機能は、すべてのエンコーダモード(直交、クロック プラス方向、方向クロック)でサポートされています。

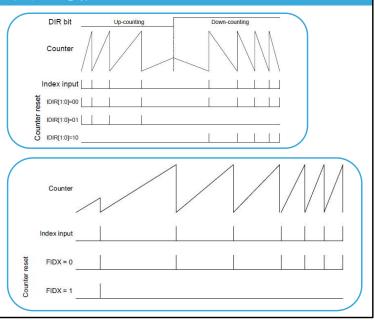

上段のタイミング図は、直交モードを使用することを前提としています。

インデックスパルスを検出すると、カウンタはリセットされます。 市販のエンコーダーは、インデックスパルスコンディショニング のためのいくつかのオプションを提案されています。

·AとBでゲーティング:パルス幅は1チャネルの周期の1/4で、AとBの両方のエッジに合わせて配置されています。

·Aでゲーテッド(またはBでゲーテッド):パルス幅は1チャネルの周期の1/2で、チャネルAの2つのエッジに合わせて(チャネルBに合わせて)配置されます。

·Ungated(アンゲート):パルス幅は1チャネルの周期までで、エッジへのアラインメントはありません。

#### インデックス検出

- 2ビット(IPOS[1:0])は、どの状態でインデックスが検出されるかを定義

- インデックス検出は、速度反転時に対称的な動作を保証するために、カウント方向に応じて異なる方法で行われる

- カウンタはアップカウント中にリセット (DIRビット=0)

- カウンタはカウントダウン時にTIMx ARRに設定

TIMx\_ECRレジスタのIPOSビットフィールドを使用して、どのエンコーダ状態(チャネルAとチャネルBの状態の組み合わせ)でインデックスを同期させなければならないかを定義する必要があります。

インデックス検出イベントは、速度反転時の対称動作を確保するために、カウント方向によって異なる動作をします。 ・カウンタはアップカウント中にリセットされます(DIRビット=0)。 ・カウンタはカウントダウン時にTIMx\_ARRに設定されます。 これにより、計数方向に関して、非常に同じ機械的角度位置でインデックスを生成できます。

### インデックス入力の後処理

- Z信号を方向に応じて調整することが 可能

- リセットは一方向でのみ発生

最初のインデックスだけを取ることが 可能

タイマユニットは、インデックス入力の後処理をサポートしています。

- ・方向インデックス感度が有効な場合、インデックスは選択されたカウント方向にのみアクティブになります。

- 上のタイミング図は、IDIRフィールド値に応じたインデックスと カウンタリセットイベントの関係を示しています。

- 例えばIDIR=01の場合、インデックスはアップカウントのみの場合にカウンタをリセットします。

- 2番目の後処理オプションでは、下のタイミング図に示すように、インデックスを1回だけ取得できます。

FIDX=1の場合、最初のインデックスが到着すると、それ以降のインデックスは無視されます。

エンコーダ・エラーの検出

- 直交位相エラー検出

- ・ 誤った遷移(例:01~10)の場合

- 位置カウンタ・エラー検出

- カウンタ値がTIMx\_ARRから0にデクリメントされた場合、またはインデックス・イベントなしに0から TIMxARR値にインクリメントされた場合、インデックス位置エラーとして報告

外部ノイズ、配線の問題、埃の多いセンサなどのために、いくつかのパルスが追加された/欠落したことを示す

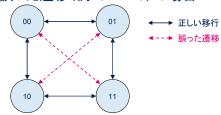

タイマユニットは、2種類のエンコーダエラーを検出します。

2つの直交信号が利用可能なエンコーダ構成の場合、遷移エラーを検出することが可能です。

2つの入力の読み取りは、状態図として表現できる2ビットのグレーコードに対応しています。

一度に1ビットが変化することが予想されます。

誤った遷移が発生した場合、遷移エラー割込みが発生します。 インデックス信号を持つエンコーダでは、1回転あたりのパルス数 が過多になる異常動作を検出することができます。

1回転あたりNパルスのエンコーダは、1回転あたり4xNカウントを提供します。

インデックス信号は、4xNクロック周期ごとにカウンタをリセットします。

カウンタ値が0から自動リロード値までインクリメントされた場合、またはインデックスイベントが発生しないままオートリロード値から0までデクリメントされた場合は、インデックス位置エラーとして報告されます。

このエラーが発生した場合、割込みを発生させることができます。

# 内部タイミング・リソースとしてのタイマー

###

- タイマは、単純なタイムベースとして使用することが可能

- ・ ソフトウェア管理用

- 他のペリフェラルへの定期的なトリガを提供

- A/Dコンバータ、D/Aコンバータ、または他のタイマへ

- 更新イベント(カウンタ・オーバーフロー時)を使用して割込みをトリガすることが可能

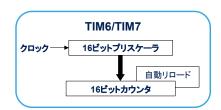

- 最もシンプルなオプションで、TIM6とTIM7の基本タイマ(出力なし)も使用可能

- 基本タイマを使用する場合のその他の手段

- コンペア・イベントの使用

- ピリオドごとに複数のイベントを持つことが可能

- タイマのトリガ出力を使用

タイマの最もシンプルな使用例は、内部のタイムベースを提供する ことです。

これはソフトウェアルーチンで一般的に使用され、周期的な割込みまたは単発のタイムアウト保護を提供するために使用されます。タイマは、相互接続マトリクスを介して、A/Dコンバータ、D/Aコンバータ、および他のタイマなどの他のオンチップペリフェラルに周期的なトリガを提供することもできます。

タイマからの更新イベント(通常はカウンタオーバーフロー時)は、 ソフトウェアのタイムベース割込みを持っているか、または周期的 なイベントをトリガするための通常の手段です。

基本的なタイマTIM6とTIM7は、入出力チャネルを持たない最もシンプルなタイマであるため、このようなタスクに最適です。

また、他のタイマを使用したり、コンペアイベントを使用したり、他のタイマのトリガ出力を使用して内部タイミングを生成することも可能です。

複数の比較チャネルを使用して、1つのタイマで複数のタイミングイベントを生成することができます。

#### 入力キャプチャ CPUオーバーヘッドを低減するための信号前処理を含む • チャネル1~4は、以下の特徴を持つ入力キャプチャと \_\_ TI IC1 T2FP1 出哭 して個別に設定することが可能 TRC ▶ 入力フィル タ&エッジ検 • 入力再マッピング(1つの入力を2つのキャプチャ・チャネルに TI1FP2 TI2 プリス TI2FP2 マッピング可能) • プログラマブル・エッジ感度(立ち上がり/立ち下がり/両方) デジタル・フィルタ イベント・プリスケーラ(1,2,4,8イベントごとに1キャプチャ) デジタル・フィルタ(デバウンス、ノイズ除去用) キャプチャ・イベントにより、カウンタの値がキャプチャ・ Internal レジスタに転送され、割込みやDMA要求をトリガ キャプチャ・レジスタが読み込まれずに上書きされた場合、オー バーキャプチャ・フラグがセットされる

Input Internal counter Filtered

Ó

このスライドでは、入力キャプチャの機能について説明します。

チャネル1~4は、多数の信号調整オプションを備えた入力キャプチャとして個別に構成することができます。

入力は、2つのキャプチャチャネルにマッピングすることができます(通常は立ち上がりエッジと立ち下がりエッジのキャプチャを区別するため)。

TRC入力は、キャプチャトリガとして選択することができ、ITR入力の1つに接続されている(タイマ間相互接続)。

エッジ感度はプログラム可能で、立ち上がりエッジ、立ち下がりエッジ、または両方のエッジを設定できます。

イベントプリスケーラにより、2、4、8イベントごとに1イベントをキャプチャすることができます。 これにより、高周波信号を処理する際のCPU負荷が軽減され、複数の入力信号期間にわ たって実行されるため、測定をより正確に行うことができます。

ノイズやバウンスによるスプリアスなトランジションイベントは、プログラム可能なデジタルフィルタを使用して除去することができます。

フィルタの受け入れを4に設定した場合の信号のフィルタリングの様子を示しています。 上のケースでは、内部カウンタ値を見てわかるように、クリーンな立ち上がりエッジのキャ プチャは立ち上がりエッジの4サンプリング周期後にトリガされます。

下のケースでは、グリッチによりフィルタカウンタがリセットされ、ハイレベルの4つのサンプルが連続してカウントされた後にキャプチャが行われます。

キャプチャトリガが発行されると、タイマのカウンタがキャプチャレジスタに転送され、割込みやDMA要求を発行することができます。

前のキャプチャが読み込まれる前に新たなキャプチャが発生した場合、キャプチャレジスタが上書きされ、必要に応じてソフトウェアがこの状態を管理するためのオーバーキャプチャフラグがセットされます。

# 高度なキャプチャ・オプション

20

### ソフトウェアのオーバーヘッドがない直接測定

- クリアオン・キャプチャ・モード

- このモードでは、キャプチャがトリガされた直後にカウンタをリセットすることが可能

- PWM入力モード

- タイマは、2つのキャプチャ・レジスタに信号の周期とパルス幅を直接キャプチャ可能

- XOR機能付きクリアオン・キャプチャ・モード

- 最大3つの入力の任意のエッジ間の間隔をキャプチャ が可能

- 電子モータのホールセンサに使用される

このスライドでは、より高度なキャプチャ関連機能の一部を紹介しています。 クリアオンキャプチャモードでは、キャプチャがトリガされた直後にカウンタがリセットされます。

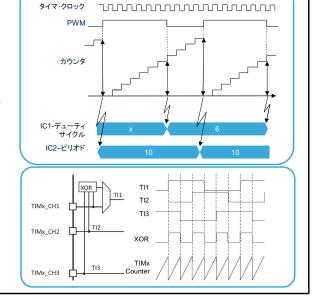

従来のフリーランニングカウンタでは、トリガに続く周期を得るために追加の計算が必要でしたが、これにより周期を直接測定することができます。PWM入力モードでは、タイマは入力されたPWM信号の周期とデューティサイクルの両方をキャプチャすることができます。

入力信号は内部的に2つのキャプチャ・チャネルにルーティングされます。 信号の立ち上がりエッジは入力キャプチャ2でキャプチャされ、クリアオンキャプ チャモードで周期値を提供します。

立ち下りエッジはキャプチャ1チャネルでキャプチャされ、パルス長の持続時間 を提供します。

デューティサイクルは、入力キャプチャ1と入力キャプチャ2の間の比率に単純に対応します。

最後に、タイマには3つの入力チャネルをXORロジックで結合するためのXOR機能が含まれています。

これは通常、電動モータのホールセンサから来る120°位相シフトした3つの信号を処理するために使用されます。

これにより、3つの信号の各エッジで発生している明確なキャプチャが可能になり、速度規制に直接使用可能なキャプチャ値を得ることが出来ます。

#### 単純な出力波形の場合、ピリオドの経過を表示する場合

- カウンタがコンペア・レジスタの値と一致した場合

- 対応する出力端子をプログラムすることが可能

- セット、リセット、トグル、変更しない

- 割り込みステータス・レジスタにフラグがセットされる

- 対応するイネーブル・ビットがセットされている場合、割込みまたは DMAリクエストを発生可能

- コンペア・レジスタは、プリロード・レジスタの有無に関わらずプログラム可能

- プログラムされた出力モード(セット、リセット、トグル) をプリロードすることも可能

- 1つのモードから他のモードへのグリッチレスな移行が可能 (通常はPWMから連続的にオンまたはオフ状態に移行)

このスライドでは、出力コンペアの特徴を紹介しています。 カウンタがコンペアレジスタの値と一致したときにコンペアイベント が発生します。

このイベントは、割込みやDMA要求をトリガすることができ、出力セット、出力リセット、出力トグルにより対応する出力ピンに反映されます。

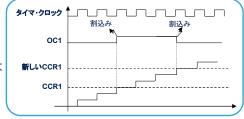

コンペアレジスタはプリロードすることができます。

カウント期間中に複数のコンペア値を書き込む必要がある場合は、 プリロードを無効にする必要があります。

タイミング図では、プリロードは無効になっています。

逆に、リアルタイム制約を持つアプリケーションでは、次の値で比較レジスタを更新するソフトウェアの時間の余裕が高くなるので、プリロードモードの使用が好ましい場合があります。

プリロードからアクティブ値への転送は、カウンタがオーバーフローまたはアンダーフローすると、更新イベントによってトリガされます。また、出力コンペアモードは、例えば、PWMモードから強制的なオンまたはオフ状態へのグリッチレスな遷移を可能にするために、プリロードすることができます。

# ワンパルス・モード

#### 外部同期波形生成用

- 入力に応答しカウンタを開始し、パルスを生成することが出来る

- プログラム可能な遅延の後

- プログラム可能な長さ

- 2つのソフトウェア・プログラム可能な波形

- ・シングル・パルス

- 繰り返しパルス

- 再トリガ可能オプション

- パルス幅は新しいトリガの場合に拡張

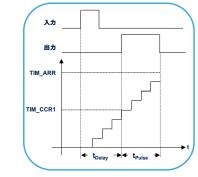

ワンパルスモードは、外部イベントに応答してプログラム可能 な長さのパルスを生成するために使用されます。

パルスは、入力トリガが到着してすぐに、またはプログラム可能な遅延時間の後に開始することができます。

コンペア1レジスタ(CCR1)の値はパルス開始時間を、オートリロードレジスタ(ARR)の値はパルス終了時間を定義します。そして、実効パルス幅は、ARRレジスタ値とCCR1レジスタ値の差として定義されます。上のタイミング図を参照してください。波形は、トリガによって生成される単一のパルス、または単一のトリガによって開始される連続的なパルス列を持つようにプログラムすることができます。

ワンパルスモードでは、再トリガ可能なオプションも用意されています。

このスライドの一番下のタイミング図は、このオプションについて説明しています。

パルスの終了前に新たなトリガが到来すると、カウンタがリセットされ、それに応じてパルス幅が拡張されます。

# いくつかのPWMモード

23

### 複数のアプリケーションに対応する多彩なPWMモード

基本的なPWM、エッジまたはセンター・アライン

Center-aligned PWM

非対称センター・アラインPWM

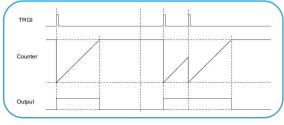

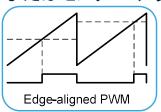

このスライドでは、PWMモードの一部を紹介しています。

標準的なエッジアラインメントPWMモードは、自動リロード・レジスタでピリオドを定義し、コンペア・レジスタでデューティ・サイクルを定義しプログラムされ、カウンタはアップのみまたはダウンのみのカウント・モードになっています。1つのタイマで最大6つのPWM信号を独立したデューティサイクルで同一周波数で生成することができます。

同じタイマで複数のPWM波形が生成される場合、すべての立下りエッジが同時に発生するため、エッジアラインドと呼ばれています。

逆に、センターアラインドPWMの立ち上がりエッジと立ち下がりエッジは、カウンタのロールオーバーに同期していないため、スイッチング時間はデューティサイクル値によって変化します。

これは、カウンタをアップダウンモードでプログラミングすることで実現されます。

このモードは、同じタイマで複数のPWMを発生させたときにスイッチングノイズが分散されます。

これは、与えられたスイッチング周波数に対して電流リップルの周波数を2倍にすることができるため、電動モータ向け3相PWM発生の大きな特徴となっています。

例えば、10kHzのPWMでは、20kHzの電流リップルが発生します。

これにより、PWM周波数によるスイッチング損失を最小限に抑えつつ、PWM動作の静音性を実現しています。

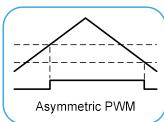

センターアラインメント・モードの変形として、非対称PWMモードがあり、2つのコンペアレジスタでPWM信号のオン/オフを定義します。これにより、ターンオン時間とターンオフ時間が個別に定義されるため、パルス幅設定の分解能が向上します。

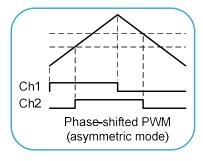

また、フルブリッジ位相シフトトポロジーに基づいてDC/DCコンバータを駆動するために必要な位相シフトされたPWM信号を生成することができます。

右下のタイミング図では、タイマは同一周波数、50%のデューティサイクル、0~180°の位相シフトを持つ2つのPWM信号を提供しています。

#### PWM機能を拡張し、外部に接続されるロジックを回避

- 組合せPWMモード

- 2つのチャネルをORまたはAND関数で結合し、より複雑な波形を実現

- 3相モードの組合せ

- ゼロ・ベクトル挿入のために、通常の3相PWMと組み合わせて4番目のPWMを可能

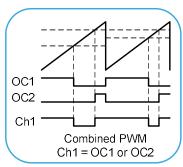

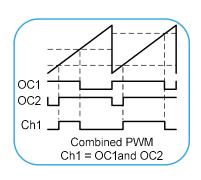

このスライドでは、組み合わせたPWMモードを紹介しています。

このモードでは、隣接するチャネルで2つのPWM信号を論理的に組み合わせて生成することができます(出力コンペア1と2、または出力コンペア3と4)。

PWMは、複雑な波形を作成するためにORまたはAND結合することができます。

これにより、任意のパルス幅と任意の位相関係の値で生成された2つの 周期的なパルスを実現することができます。

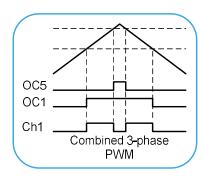

3相PWMモードを組み合わせることで、1~3つのセンターアラインメント PWM信号を、パルスの途中で1つのプログラマブル信号ANDで生成する ことができます。

このモードは、特に3相モータ制御アプリケーションを対象としています。 この場合、タイマのチャンル5は、3チャネル(1、2、3)のいずれかと組み 合わせて、センタリングパターンのPWM信号の途中にローレベル状態を 挿入することができます。

このモードは、通常ゼロベクトル挿入と呼ばれる技術を使用して、3相モータ制御のための低コストの電流検出技術の実装を大幅に簡素化します。

# 高度なPWMモード

25

#### 外部制御を必要とするPWM信号の場合

- 可変周波数PWM

- 外部信号で駆動

- サイクル・バイ・サイクル制御された デューティ・サイクル

- コンパレータまたは外部ピンによって駆動される電流ループの場合

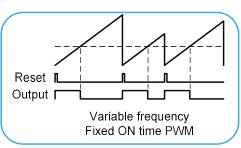

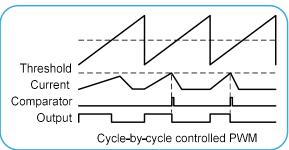

このスライドでは、周波数やデューティサイクルを外部信号で駆動することができる、より具体的なPWMモードを紹介します。

タイマは、ETR、またはチャネル1または2入力に接続された外部リセット信号を使用して、可変周波数信号を供給することができます。

このモードの目的は、固定されたオンまたはオフ時間と、ハードウェアによって制御された連続的に調整された周波数を持つ信号を提供することです。タイマはコンペアレジスタを使用してオン(またはオフ)時間の制御を行い、自動リロードレジスタは外部リセットが欠落してもPWMが停止しないことを保証するため、境界条件での安全な制御を提供します。

この技術は、主電源アプリケーションのトランジションモードPFC(力率改善回路)や電流制御型デジタルLED照明など、様々な用途に使用されています。タイマのもう一つのモードは、オンチップコンパレータまたはオフチップ信号のいずれかで、デューティサイクルをハードウェアで制御することです。

PWMは一定の周波数で動作し、最大デューティサイクルはコンペアレジスタと 実際の値制御サイクルバイサイクルによって設定されます。

これは電流制御PWMを必要とするアプリケーションに使用され、通常はDCモータやソレノイドの駆動に使用されます。

この場合、コンパレータは負荷へのピーク電流値を監視します。

電流がプログラムされた閾値を超えるとすぐに、コンパレータはPWM出力をリセットし、次のPWM期間に自動的に再起動し、制御されたピーク電流値を提供します。

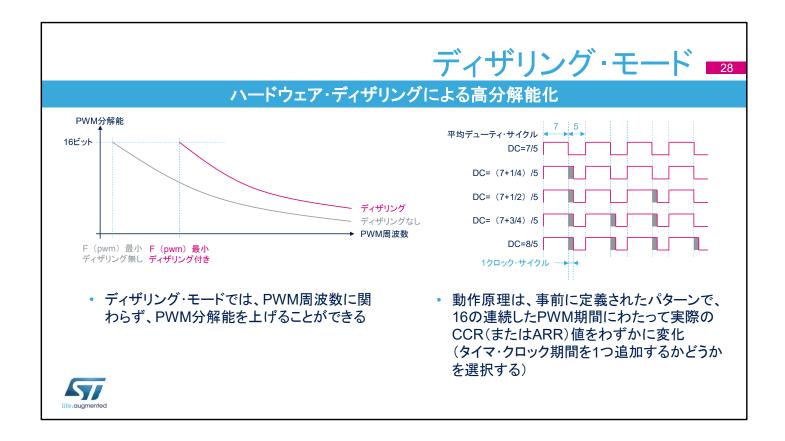

#### ハードウェア・ディザリングによる高分解能

- PWM周波数に相当するスイッチング周波数とPWM分解能との間には密接な関係がある

- PWM分解能を上げることは、タイマ・クロック周波数を一定に保ちながらPWM周波数を下げることを意味する

- このトレードオフを克服するために、PWMディザリング技術では、一定のPWM周波数を維持しつつ、ベース・タイマ・クロック周波数を増加させることなく、PWM分解能を向上させることを提案

16ビットの分解能を持つタイマの場合、分解能を上げると周波数が下がることになります。

PWMクロック周波数が指定されている場合、

-タイマの14ビットを使用する場合、PWM周期は2<sup>14</sup>クロックサイクルで、分解能はPWM周期を2<sup>14</sup>で割った値となります。 -タイマの13ビットを使用した場合、PWM周期は2<sup>13</sup>クロックサイクル、分解能はPWM周期を2<sup>13</sup>で割った値となります。 ディザリングモードを有効にすることで、PWMモードの有効分解能を上げることができます。

# ディザリング・モード

### 16サイクルディザリングパターン

- 基本的な考え方は、6.66ns(@150MHz)からサブnsレンジ(6.66/16ns=416ps平均)に行くために4ビットを追加

- 周期とデューティ・サイクルの両方に適用可能で、プログラミングに応じて+0/+1クロック・サイクル を加算

- 整数部は0から4095まで、端数部は0から0.9375まで(0.0625の15段階)

ディザリングモードを有効にすると、レジスタのコーディングが変更されます。

- 最下位4ビットは、強化された分解能の部分(端数部分)を符号化しています。

- 最上位ビットはビット19:4に左シフトされており、ベース値を 符号化しています。

左側の曲線は、PWM周波数に応じたPWM分解能を示しています。

与えられた分解能に対して、ディザリングが有効な場合の周波数は、ディザリングがない場合よりも大きくなります。

右のタイミング図は、ディザリングの原理を説明しています:選択されたデューティサイクルに応じて、連続する16のPWM期間にわたってタイマクロック期間を追加するかしないかで変化させます。

これにより、平均的なデューティサイクルまたはPWM周期を考慮して、分解能を16倍に向上させることができます。

### ディザリング・モード 16サイクル・ディザリング・パターン Counter period 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 • 322=16x20+2 CCR1 value • 326=16x20+6 CCR2 value Compare2 value 21 20 21 20 21 20 21 20 21 20 20 20 21 20 21 20 21 20 21 20 20 20 • 334=16x20+15 CCR3 value Compare3 value \( \begin{aligned} 21 \quad \be • 336=16x21 CCR4 value Compare4 value \( \lambda 21 \rangle 21 \ran 5

自動リロードとコンペア値のインクリメントは、特定のパターン に沿って広がっています。

このタイミング図では、カウンタの周期が固定されていると仮 定し、デューティサイクルのみが変化します。

パターンは、コンペア値と16の間の除算のアラームによって異なります。

最初のタイミング図では、CCR1でプログラムされたコンペア値は322に等しくなります。

322=20\*16+2.

つまり、322と26の間の除算の残りは2であり、16期間にわたる 2期間の間、コンペア値の最下位ビットがインクリメントされることを意味します。

ディザリングシーケンスは、インクリメントを可能な限り均等に 分散させ、全体のリップルを最小限に抑えるために行われます。

# カスケード・タイマ1/2

#### より高い柔軟性のためのスケーラブルな設計

- トリガ・コントローラは、マスタ/スレーブ 構成で複数のタイマをカスケードする機 能を提供

- スレーブ:トリガ・コントローラがTRGI上の入力を収集

- 外部トリガ・ピン(ETR)から

- ITRxの他のオンチップリソースから

- 通常、TRGOは他のタイマから出力

- マスタ:内部タイマ信号はTRGOに送信

- 接続は相互接続マトリックスで行われる

- 特定のタイマは、カスケード構成でスレーブ・モードとマスタ・モードで同時に動作することが可能

このスライドでは、タイマの同期機能を紹介します。

トリガコントローラは、マスタ/スレーブ構成で複数のタイマをカスケードすることができます。

タイマは、マスタタイマとして1つ以上のタイマを制御したり、スレーブとして他のタイマによって制御されたりすることができます。

クロックとトリガのコントローラは、タイマ間のリンクとして機能します。

マスタモードでは、タイマの外部、複数の内部制御信号、オンチップTRGOトリガ出力にリダイレクトすることができます。

スレーブモードでは、外部トリガピン(ETR)または他のTRGO出力に接続された11の内部トリガ入力(ITRO~ITR10)のうちの1つから来るTRGI(メイントリガ 入力)に複数の入力を収集します。

さらに、入力キャプチャ1と2ピンは、内部トリガ(通常はカウンタをリセットするため)として使用することもできます。

スレーブモードとマスタモードは独立してプログラムすることができます。 このようにして、特定のタイマは、出カトリガを提供しながら入カトリガを受け 入れ、カスケード構成でスレーブモードとマスタモードで同時に動作すること ができます。

マスタ同期とスレーブ同期は、タイマユニット内で独立してインスタンス化されます。

すべてのSTM32G4タイマの機能をまとめた、このプレゼンテーションの最後の表を参照してください。

#### 複数の信号をタイマ間で共有可能

- マスタモード:タイマは内部信号をTRGO出力に伝搬

- カウンタ・リセット、カウンタ・イネーブル、更新イベント、またはOC1コンペ アマッチ

- OC1~OC6で生成された波形のいずれか

- スレーブ・モード:タイマはTRGI入力で制御される

- トリガ・モード:カウンタスタートを制御

- リセット・モード:TRGIの立ち上がりエッジでカウンタが再初期化される

- リセット&トリガ・モードの組み合わせ(再トリガ可能なワンパルス・モード用)

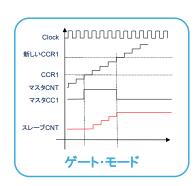

- ゲート・モード:カウンタの開始と停止の両方が制御される

- 複合ゲート+リセット・モード

- クロックに関連するその他のモード:

- 3つのエンコーダ・モード

- 外部クロック

れています。

このスライドは、各種動作モードとタイマ間でやり取りされる信号を一覧にしたものです。 マスタモードでは、TRGO出力に送信するトリガを選択するために16のオプションが与えら

出力は、カウンタリセット時に発行される単一の同期パルス、カウンタスタートに対応する カウンタイネーブル、更新イベント、またはコンペア1マッチイベントに対応するカウンタイ ネーブルとすることができます。

あるいは、TRGO出力は、PWM信号を含む6つの波形のうちの1つを他のタイマモジュール に送信することもできます(チャネル1~6で比較し、すべてのチャネルのパルスを比較しま す)。

スレーブモードでは、タイマの動作モードはTRGI入力で制御されます。

トリガモードでは、カウンタの起動を外部制御します。このモードは、複数のタイマを同時 に起動する場合に使用します。

リセットモードでは、カウンタはTRGI入力の立ち上がりエッジによってリセットされます。 リセットとトリガを含む複合モードを使用して、再トリガ可能なワンパルスモードを生成する ことができます。

タイミング図に示すゲートモードでは、入力信号のレベルがハイレベルの間のみカウンタ がアクティブになります。

リセットとゲートを含む複合モードを使用して、範囲外のPWM信号(デューティサイクルが 最大期待値を超える)を検出することができます。

外部クロックモード2は、他のスレーブモード(外部クロックモード1とエンコーダモードを除 く)に加えて使用することができます。

この場合、ETR信号を外部クロック入力として使用し、トリガ入力として別の入力を選択す ることができます。

最後に、スレーブモードの選択には、このプレゼンテーションで前述した直交エンコーダデ コードや外部クロックモードなどのクロック関連のモードが含まれます。

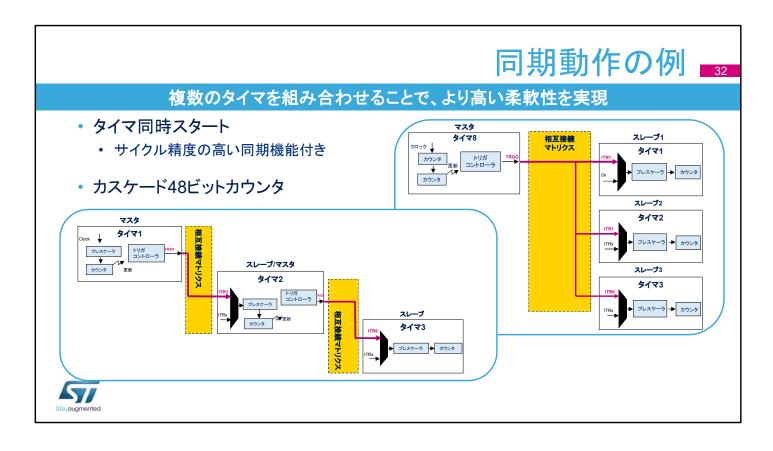

このスライドでは、同期動作の例を2つ示します。

最初の例は、4つのタイマを同時に開始する方法を示しています。

マスタ/スレーブリンクの遅延を補正するために、マスタタイマをわずかに遅れて開始させ、すべてのタイマをサイクル精度で同期させることができる機構です。

図のようにタイマ1、2、3、8のチャネルを組み合わせることで、 最大16個のPWMチャネルを同期させることが可能です。

2番目の例は、3つのタイマをカスケード接続して48ビットのタイマを作成する方法を示しています。

ここでは、カウンタのロールオーバー時に発生する更新イベントを後続のスレーブタイマの入力クロックとして使用し、タイマ1のカウンタは最下位の16ビット、タイマ2のカウンタは中位のビット(16~31)、タイマ3のカウンタは上位のビット(32~47)を保持するようにしています。

### モータ制御機能

#### STM32タイマはモータ・ドライブのあらゆる側面をカバー

- PWM生成

- センター・アラインメントおよび組合せ3相モード

- デッドタイム挿入

- 6ステップ・モード

- 保護機能 (デュアル・ブレーク緊急停止機構)

- スピード&ポジション・センシング

- エンコーダ、ホールセンサ、およびタコメータ・ジェネレータ用専用モード

- A/Dコンバータ・トリガ

このスライドでは、タイマを使ったの4つの電動モータ制御の特徴をまとめています。

- ▶タイマには、電源スイッチを制御するための特定のPWMモードが含まれています。以前に説明したセンターアラインドおよび複合3相PWMに加えて、相補的なPWM生成のためのデッドタイム挿入とブラシレスDCモータ駆動のための6ステップモードを特徴としています。

- ▶障害が発生した場合にハードウェアでPWM出力を無効化するための二重レベルの非常停止機構を備えたパワーステージ保護回路を搭載しています。

- ➤モータ制御システムで見られる最も一般的なセンサーを扱う ことができます。タコメータジェネレータはコスト効率の良い 速度フィードバックに使用され、クリアオンキャプチャモードを 必要とするだけです。

- ▶最後に、タイマには、電圧と電流の検出を適切に管理し、パワーステージのスイッチングノイズによる捕捉の問題を回避するために必要な、同期化されたA/Dコンバータトリガオプションが含まれています。

# デッドタイム挿入

#### タイマあたり最大3つのハーフブリッジ・コンバータを直接駆動

- ハードウェア・デッドタイム・ユニットは、非重複の相補的なPWM信号を生成

- ・ 機能安全のためのデッドタイムレジスタ(読み取り専用)のロック機能

- ハーフブリッジおよびフルブリッジ・コンバータのクロスコンダクションを防止

- DC/DCコンバータ、DCモータ、三相ブラシレス・モータ

フルブリッジDCモータ・ドライブ

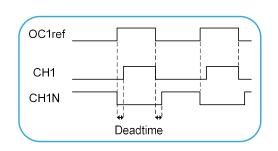

このスライドは、デッドタイム挿入機能を示しています。

ハードウェアデッドタイム・ジェネレータは、基準PWM信号から2つの重ならない相補的なPWMを提供します。

STM32タイマには、OC1、OC2、OC3、OC4チャネル用の最大4つのデッドタイムジェネレータが含まれています。デッドタイムの持続時間は8ビットの値でプログラムされています。

この値は、実行時にこの重要な値が破損するのを防ぐために、ユーザーがロックすることができます。

これは、次のMCUリセットまでデッドタイムレジスタを読取り専用モードに切り替えるライトワンスロックビットを設定することによって行われます。一対のトランジスタが2つのパワーレールの間に直列に接続されているハーフブリッジを駆動する場合には、デッドタイム挿入が必要です。この場合、物理的なスイッチング特性を考慮して、一方の側のスイッチオンの前に、他方の側のスイッチオフを許容するための時間を挿入する必要があります。

ハーフブリッジは通常、DCまたはステッピング・モータ駆動用のDC/DCコンバータでは、ここに示すフルブリッジ・トポロジーを使用するか、3相インバータでは3つのPWMペアを使用します。

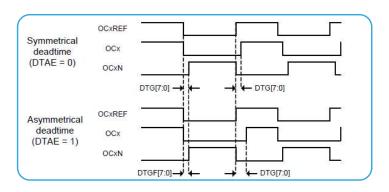

#### 非対称デッドタイム

- 非対称:レガシ・モード(対称)と新しいモードの両方をサポートするためのイネーブル ビットを備えた新しいレジスタ

- 非対称ゲートドライバ/オプトカプラの伝搬遅延を持つアプリケーション用

- オンザフライ・デッドタイム更新用シャドウ・レジスタ(適応型デッドタイム方式、デジタルSMPSまたは照明アプリケーション用)

対称モードでは、OCx出力の立ち上がりエッジと立ち上がりエッジの両方で、デッドタイムの期間は同じです。

非対称モードでは、立ち上がりエッジ参照のデッドタイムは DTG[7:0]ビットフィールドで定義され、立ち下がりエッジ参照の デッドタイムはDTGF[7:0]ビットフィールドで定義されます。 ゲートドライバやオプトカプラの伝搬遅延が非対称なアプリ ケーションに有効です。

プリロード機構を使用して、PWM動作中にデッドタイム値をオンザフライで更新することが可能です。

プリロード値は次の更新イベントでアクティブレジスタにロードされます。

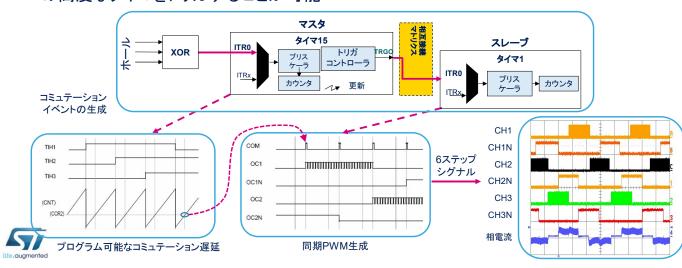

# 6ステップ/ブロック・コミュテーション

### ブラシレスDC(BLDC)モータ駆動向け、CPU負荷のオフロード

• 1つのタイマでホールセンサのフィードバックを処理し、同期したPWM生成のための高度なタイマをトリガすることが可能

このスライドは、STM32タイマを使用して6ステップドライブ(ブロックコミュテーションとも呼ばれます)を管理する方法を示しています。

これは、2つのタイマを連結して構成されており、1つは3つのホールセンサ信号を処理し、もう1つはロータの角度位置に同期したPWM生成を管理し、6つの連続したステップを生成します。

最初のタイマは、3つの入力によってトリガされるクリアオンキャプチャモードで動作します。

コンペアレジスタ(ここではコンペア2)は、生の角度位置とコミュテーション時間の間にプログラム可能な遅延を追加する役割を果たします。

キャプチャレジスタ1は、連続するホールセンサエッジ間のタイミング間隔を保持するものであり、速度規制ループに必要です。

コンペア2の一致イベントは、TRGO出力を介してスレーブタイマに伝搬されます。 これらのイベントは、PWM生成のコミュテーションイベントとして機能し、変更をトリガ

これらのイベンドは、PWM生成のコミュナーションイベンドとして機能し、変更をドリアします。

シーケンスの6つのステップのそれぞれについて、6つの出力の状態は、強制的にアクティブか非アクティブか、またはPWM信号を生成するように定義されています。

一方のステップから他方のステップへの移行は、ソフトウェアによって割込みルーチン内にプリロードされ、次の割込みが到着したときに出力動作モードを再プログラムするために、ハードウェアによって自動的に転送されます。

右図は、2つの連続した完全な6ステップシーケンスの6つのPWM信号と、モータ1つの相電流を示しています。

#### クラス最高の保護スキーム

- ブレークイベントはPWM出力を無効にする

- ハードウェア別(最小レイテンシ)

- 非同期(クロックレス動作、クロック関連の遅延なし)

- プログラム可能な安全状態(ハイ/ローまたはHi-Z)

- 相補的な出力を持つタイマで利用可能

- タイマ1、8、15、16、17、20

- タイマ1、8、20に2つのブレーク・チャネルが実装

- 二重レベルの保護スキームが可能

- すべての出力がOFF、または一部の出力が強制ON、一部の出力がOFF

- デッドタイムの挿入は、シュートスルーのリスクがないことを保証

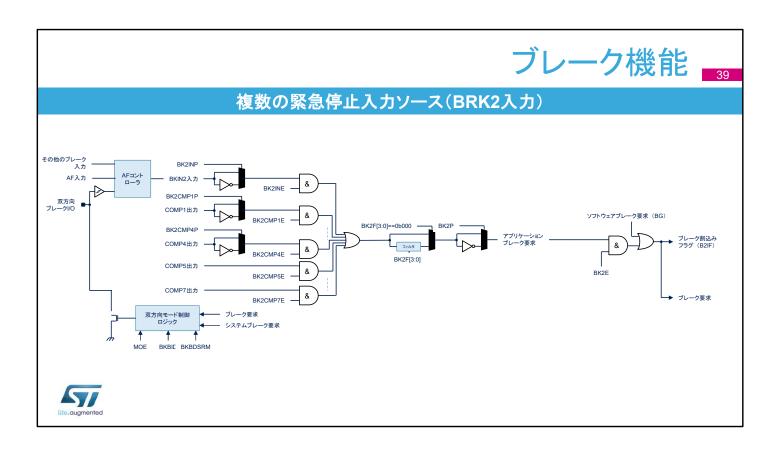

このスライドでは、ブレーク機能を紹介しています。

ブレークイベントは、PWM出力を自動的に無効化し、ユーザーが設定可能な状態(ハイレベルまたはローレベルの低インピーダンス、またはハイインピーダンス)に強制的にするハードウェア保護機構をトリガします。

論理回路は、クロックを使わずに非同期で動作します。

これにより、システムクロックが故障した場合でも機能が保証され、保護を遅らせがちなクロック関連の伝搬時間を回避することができます。

この機能は、電力変換タスクを実行することができる相補的なPWM出力を持つすべてのタイマで利用可能です。:タイマ1、8、15、16、17、20。

タイマ1、8、20は2つの分離したブレークチャネルを持ち、一方、タイマ15、16、17は独自のブレークチャネルをサポートしています。

2つのブレークチャネルをサポートすることで、デュアルレベルの保護スキームを提供し、例えば、すべてのスイッチがオフの状態で優先度の低い保護を、ローサイドのスイッチがアクティブな状態で優先度の高い保護によって上書きすることができます。

さらに、フォルトモードに入る直前にデッドタイムディレイを挿入して、安全にパワーステージを無効にすることができます。

これにより、潜在的なシュートスルー状態を防ぐことができます。

例えば、安全状態がハイサイドOFF、ローサイドONにプログラムされている状態で、ハイサイドPWMがONの時に障害が発生した場合、

システムは最初にハイサイドPWMを無効にし、ローサイドをONにする前に デッドタイムを挿入します。

#### ブレーク機能 複数の緊急停止入力ソース(BRK入力) & ロックアップロック PVD & PVDロック RAMパリティエラー & パリティLOCK & ECCロック クロックセキュリティシステム(クロックの損失) その他ブレーク 入力 ソフトウェアブレーク要求 (BG) AF入力 & → ブレーク割込み フラグ (BIF) BKCMP1P 双方向ブ レークI/O COMP1出力 & BKE BKCMP1F -BKF[3:0]==0b000 BKCMP4 ブレーク要求 & BKCMP4F BKF[3:0] & BKCMP5E COMP7出力 & システムブレーク要求

このスライドでは、BRK入力に関連するブレーク機能について説明します。 複数のブレークソースを組み合わせてブレークイベントをトリガすることが できます。

システムブレーク要求は、CPUロックアップ、電源電圧低下、RAMパリティエラー、フラッシュECCエラー、クロックの損失などの重大なエラーがMCUで検出された場合に発生します。

ロック信号は、SYSCFGペリフェラルにある書き込み可能なビットです。 デフォルトでリセットされます(フォルトエラーはマスクされます)。

一度設定(故障検出が有効)されると、機能安全のためにMCU全体がリセットされない限り、それらはリセットできません。

アプリケーションのブレーク要求は、ボードの故障に起因します。

ブレーク入力は、マイクロコントローラのピンアウトにあるオルタネート機能コントローラで選択することもできます。

適切な極性を選択し、デジタルフィルタを使用してスプリアスなグリッチを除去するために、ブレーク検出ユニットに入る前に外部ソースの調整をすることができます。

ソフトウェアは、通常、回復不可能なエラー状態を診断する際に、ブレークを要求することも可能です。

これらのブレーク要求のいずれかが発生すると、PWM出力を安全な状態に設定するだけでなく、割込みまたはDMA要求がアサートされます。

BRK2入力に関連するブレーク機能について説明します。 BRK入力とは異なり、BRK2イベントはシステムブレーク要求で もソフトウェアブレーク要求でも発生しません。

### ブレーク機能 40

- ブレーク入力は、外部の故障イベントを受け入れるための双方向性であり、MCUの外部で内部故障イベントを信号化する

- この機能を使用すると、次の機能が可能になる

- 外部MCUまたはゲート・ドライバが入力をシャットダウンするために利用可能なグローバル・ブレーク情報を1ピンで提供

- 内部コンパレータと複数の外部オープンドレイン・コンパレータの出力が一緒にORされ、複数の内部および外部ブレーク入力がマージされなければならない場合にブレーク・イベントをトリガ

- すべての内部フォルト・ソース(システム、コンパレータ)は、単一の信号にマージ

STM32G4は双方向ブレークを実装します。

ブレークIOパッドはボードレベルの故障を報告するために使用されますが、マイクロコントローラ内部の故障を知らせるための出力としても使用できます。

双方向モードは、ブレークおよびブレーク2入力の両方で使用可能で、アクティブなロー極性のオープンドレインモードでI/Oを構成する必要があります。

したがって、STM32G4内で検出されたグローバルブレーク情報は、他のCPUまたはゲートドライバに出力できます。

内部ブレークソースと複数の外部オープンドレインコンパレータ 出力は、複数の内部および外部ブレークソースをマージする必要がある場合に、独自のブレークイベントをトリガするために一緒にORされます。

#### ブレーク機能解除のメカニズム

- ブレーク入力は、ビットBKxBIDが1に設定されている場合、双方向モードで構成される

- 安全なブレーク機能の解除機構により、システムが確実にロックアップされることを防ぐ

ブレーク入力のローレベルは、同じ入力のローレベルを強制するブレークをトリガ

- ・ビットBKxDSRMが1に設定されると、ブレーク出力が解除されフォルト信号がクリアされて、 システムの再起動が可能になる

| MOE | BKxDIR | BKxDSRM<br>(DiSaRMed) | 状態             |  |  |  |  |  |  |

|-----|--------|-----------------------|----------------|--|--|--|--|--|--|

| 0   | 0      | X                     | セット(BKINは入力信号) |  |  |  |  |  |  |

| 0   | 1      | 0                     | セット(BKINは双方向)  |  |  |  |  |  |  |

| 0   | 1      | 1                     | 解除             |  |  |  |  |  |  |

| 1   | Х      | Х                     | セット            |  |  |  |  |  |  |

このスライドでは、ブレーク回路の解除方法を説明します。

BKxBIDビットがセットされているときは双方向モードになります。

ブレークIOパッドは双方向性なので、ブレーク入力のローレベルは、同じパッドのローレベルを強制するブレークをトリガします。

そのため、ブレーク状態を解除するためには、解除機構が必要です。

メイン出力イネーブル(MOE)ビットは、チャネルが出力として構成されている場合に関連します。

ブレーク入力の1つがアクティブになるとすぐにハードウェアによって非同期的にクリアされ、OCおよびOCN出力をディセーブルにします。

以下のシーケンスを使用して、ブレークイベントの後にプロテクションを再設 定する必要があります。

- BKDSRM(BK2DSRM)ビットを設定して出力制御を解除する必要があります。

- ソフトウェアは、システムブレーク状態がなくなるまで待ち(もしあれば)、 SBIFステータスフラグをクリアしなければなりません(または、再セットする前にシステムにクリアしなければなりません)。

- ソフトウェアは、ハードウェアによってクリアされるまで(アプリケーションブレーク条件が消滅したとき)、BKDSRM(BK2DSRM)ビットをポーリングする必要があります。

この時点からブレーク回路はセットしてアクティブになり、MOEビットを設定してPWM出力を再有効にすることができます。

#### A/Dコンバータ・トリガの複数のオプション

- A/Dコンバータ・トリガの発生は、タイマ・イベントによって発生可能

- タイマ出力はA/Dコンバータ1~5レギュラおよびインジェクト・チャネルをトリガするために使用可能

- 次のタイマ出力が使用される

- コンペア出力CC1、CC2、CC3、CC4

- トリガ出力TRGOとTRGO2

- TRGO2出力はA/Dコンバータ専用

- 16の使用可能なトリガソース

- PWM周期ごとにデュアルA/Dコンバータ・トリガを許可

- TRGOは、同期の目的でフリー

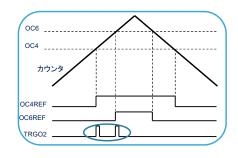

このスライドでは、タイマに関連したA/Dコンバータのトリガオプションを紹介します。

A/Dコンバータは、ほとんどのSTM32タイマでトリガすることができます。

これはコンペアイベントを使用して行うことができます: A/Dコンバータは指定されたコンペアマッチで開始されます。これはタイマ・チャネル1から4に適用されます。

TRGOイベントは、特定のタイマでも使用できます。TRGOは、レジスタ更新、カウンタリセット、トリガ入力などの比較イベントまたはタイマ内部制御信号のいずれかになる可能性があるため、柔軟性が高くなります。

一方で、これはTRGOが同期目的で使用されることを防ぎます。 この理由から、タイマは追加のTRGO2出力も持っており、完全に A/Dコンバータのトリガに専念しています。

TRGO2は、6つのコンペアイベントを含む16の可能性を提供し、図のようにコンペア4と6のイベントを組み合わせることでPWM期間ごとにデュアルトリガを持つ可能性、またはコンペア5と6のイベントを持つことができます。

これにより、TRGOは複数のタイマ同期方式にも対応できます。

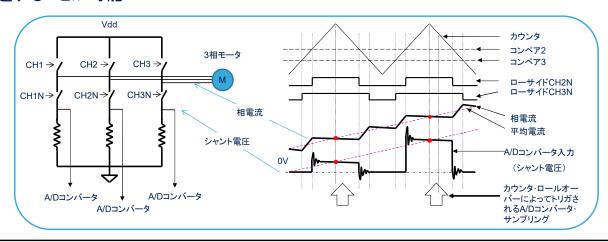

#### A/Dコンバータ読取り時にPWM関連のノイズを回避

• 三相モータ制御アプリケーションでは、カウンタ・オーバーフローでのA/Dコンバータ・トリガにより、平均電流値を得ることができ、ノイズの多いA/Dコンバータでの変換を回避することが可能

life, augmented

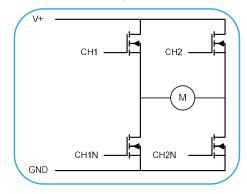

このスライドでは、PWMに同期したA/Dコンバータのトリガ例を示しています。 3相モータ制御の場合は、A/Dコンバータの読みが電源段を制御するために生成されたPWMと同期していることが必要です。

これにより、電流波形のリップルから平均値を抽出することができ、電源スイッチによるリンギングから適切な距離でA/Dコンバータの読出しを行うことができます。

左に示されているのが3相モータインバータです。

6つのスイッチは、デッドタイムが挿入された3つの相補的なPWMペアで制御され、モータ巻線の電流は、3つのハーフブリッジの下側に配置されたシャント抵抗を使用して測定されます。

右側には、CH1N、CH2Nで制御されるローサイドスイッチのタイマカウンタ、コンペア1、コンペア2の値と対応するPWM出力が表示されています。

下の2つの波形は、モータ相の電流と、この電流をシャント抵抗上で得た画像を表しています。

この低コストのトポロジーでは、電圧はローサイド・スイッチがONの時にしか測定できないので、A/Dの入力で得られる方形波状の信号を説明することができます。

この場合、カウンタのロールオーバーでA/Dコンバータトリガが生成されます。 これにより、期間の途中で正確に読み取ることができ、大きなリップルを持つ信 号の平均値を得ることができます。

さらに、PWM同期A/Dコンバータトリガを使用することで、A/Dコンバータの変換がシャント電圧に存在するリンギング・ノイズから解放されます。

#### 割込みとDMA 🛂

| イベント                                                                                   | 割込み                                              | DMA | 説明                                                                                                           |  |  |  |  |  |

|----------------------------------------------------------------------------------------|--------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 更新                                                                                     | はい                                               | はい  | カウンタがオーバーフローまたはアンダーフローした場合、または<br>強制的にソフトウェアの更新要求があった場合に発行                                                   |  |  |  |  |  |

| キャプチャ/コンペア1<br>キャプチャ/コンペア2<br>キャプチャ/コンペア3<br>キャプチャ/コンペア4<br>キャプチャ/コンペア5<br>キャプチャ/コンペア6 | プチャ/コンペア2<br>プチャ/コンペア3<br>プチャ/コンペア4<br>プチャ/コンペア5 |     | コンペアー致時、またはキャプチャがトリガされた時に発行 ・ キャプチャ/コンペアチャネルにはそれぞれ独自の割込みイネーブル・ビットとフラグがある ・ キャプチャ/コンペア5および6イベントはDMA転送をトリガできない |  |  |  |  |  |

| トリガ                                                                                    | はい                                               | はい  | トリガ・イベント時に発行(内部トリガ入カITRx、TI1エッジ検出器、フィルタリングされたTI1/TI2または外部トリガ入カピンから)                                          |  |  |  |  |  |

| Com                                                                                    | はい                                               | はい  | <i>5.7</i> 71                                                                                                |  |  |  |  |  |

| ブレーク                                                                                   |                                                  |     | - タイマ1とタイマ15-16-17のみ                                                                                         |  |  |  |  |  |

| インデックス                                                                                 | はい                                               | いいえ | インデック・イベントが検出された場合にセット                                                                                       |  |  |  |  |  |

| トランジション・エラー                                                                            | はい                                               | いいえ | エンコーダ切り替えエラーが発生した場合にセット                                                                                      |  |  |  |  |  |

| インデックス・エラー                                                                             | はい                                               | いいえ | インデックス・エラーが検出された場合にセット                                                                                       |  |  |  |  |  |

| 方向転換                                                                                   | はい                                               | いいえ | エンコーダ・モードで方向が変わる時にセット                                                                                        |  |  |  |  |  |

このスライドでは、割込みとDMAリクエストのソースを一覧にしています。 ほとんどのイベントは、割込みかDMAリクエストのどちらかを生成すること ができ、さらには2つのイベントを同時に生成することができます。

更新は、カウンタがオーバーフローまたはアンダーフローしたときに発行さ れます。主にPWM期間の開始時にタイマのランタイム設定を更新し、次のレ ジスタ更新までの間隔を最大にするために使用されます。

繰り返しカウンタを使用すると、いくつかのPWM周期をスキップして、高い PWM周波数での割込みやDMA要求の数を減らすことができます。

6つのキャプチャ/コンペアイベントにはそれぞれ独自の割込みがあります。 DMA転送をトリガすることができるのは、チャネル1~4のみです。

TRGI入力のトリガ・イベント(トリガ・ソースに関係なく)は、割込みまたは DMA要求をトリガできます。

エンコーダモードでは、エンコーダからの絶対基準位置を示すインデックス 信号により、カウンタをリセットすることができます。

このインデックスイベントは割込みの要因にもなります。

さらに、エンコーダモードでは、割込みの原因となる遷移エラーとインデック スエラーの2つのエラーを検出することができます。

割込みは、エンコーダモードでの方向変更の検出によって発生が可能です。 最後に、割込みとDMA要求の追加のソースは、コミュテーションイベントとブ レークイベントです。

### DMAバースト・モード

45

#### タイマの再設定をオンザフライで行える

- 1つのDMAイベントで複数のレジスタの更新を可能にする

- DMAの効率的な利用(シングルバーストが必要)

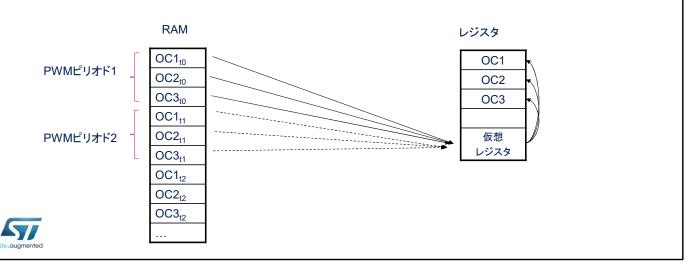

タイマには、1つのDMAストリームで複数のレジスタを再プログラムする ためのDMAバーストモードが含まれています。

これにより、複数のランタイムパラメータを同時に変更したり(例えば、複数のチャネルのデューティサイクルや周波数など)、コンフィグレーションレジスタを書き込むことでタイマのコンフィグレーションを動的に変更することができます。

この例では、新しいPWM周期の開始時に、3つのコンペア値を含むテーブルを1つのDMAバーストでコンペアレジスタに転送する方法を示しています。

DMAは、タイマ内の一意の位置(仮想レジスタTIMx\_DMAR)を指して、メモリ内でペリフェラルモードにプログラムされている必要があります。

更新イベントが発生すると、タイマはプログラムされたバースト長に対応 する数のDMAリクエストを送信します。

その後、各値は仮想レジスタから対象のアクティブレジスタに自動的にリダイレクトされます。

次の更新イベントでは、3つの新しいピリオド値が再び転送されます。 この例では、このメカニズムは、通常はこのような更新スキームに必要 な2つのDMAストリームを保存します。

| モード      | 説明                                            |

|----------|-----------------------------------------------|

| RUN      | 有効                                            |

| SLEEP    | 有効 ・ ペリフェラル割込みにより、デバイスはSLEEPモードを終了            |

| 低電力RUN   | 有効                                            |

| 低電力SLEEP | 有効 ・ ペリフェラル割込みにより、デバイスは低電力SLEEPモードを終了         |

| STOP0/1  | 停止 ・ ペリフェラル・レジスタの内容を保持                        |

| STANDBY  | パワーダウン ・ STANDBYモードを終了した後、ペリフェラルを再初期化する必要がある  |

| SHUTDOWN | パワーダウン ・ SHUTDOWNモードを終了した後、ペリフェラルを再初期化する必要がある |

この表は、現在のMCUの電源モードに応じた汎用タイマ(GPT) の状態を示しています。

RUN、低電力RUN、SLEEP、低電力SLEEPモードでは、汎用タ イマが作動します。

SLEEPモードと低電力SLEEPモードでは、GPT割込みによりデ バイスはそれぞれSLEEPモードと低電力SLEEPモードを終了し ます。

STOP0、1モードでは、汎用タイマは停止します。ペリフェラルレ ジスタの内容は保持されます。これらのモードを終了する際に は、GPTの再構成は必要ありません。

STANDBYモードとSHUTDOWNモードでは、汎用タイマはパ ワーダウンしているため、これらのモードを終了する際に再初 期化する必要があります。

低電力の場合には、LPTIMERは、STOPOおよび1モードでの完 全動作やウェイクアップ機能などの拡張機能を提供しています。

### デバッグ 47

#### 電力変換アプリケーションの安全なデバッグが可能

- 各タイマについて、DBGMCUモジュールのDBG\_TIMx\_STOPコンフィグレーション・ ビットを使用することで、マイコンがデバッグ・モード(Cortex®-M4コアが停止)に入ったときのタイマの動作を設定することが可能

- DBG TIMx STOP=0

- TIMxカウンタ操作が維持される

- DBG\_TIMx\_STOP=1

- ・ コアの停止時にカウンタのクロックを停止

- 相補的な出力を持つタイマの場合、出力は無効になる

デバッグモード時のタイマの状態は、1つのタイマにつき1つの コンフィグレーションビットで設定することができます。

- デバッグビットがリセットされると、ブレークポイント中はタイマクロックが維持されます。

- ▶デバッグビットがセットされている場合、コアが停止すると同時にタイマのカウンタが停止します。さらに、相補的な出力を持つタイマの出力は無効化され、強制的に非アクティブ状態になります。この機能は、タイマがパワースイッチや電動モータを制御するアプリケーションに非常に便利です。過大な電流によるパワーステージの損傷や、ブレークポイントに到達した際のモータの制御不能状態を防ぐことができます。

## いくつかの有用な数式1/2 48

- PWM周波数セットアップ

- 自動リロード(ARR、TIMx\_ARR)とクロック・プリスケーラ(PSC、TIMx\_PSC)で定義

- 実質的には、PSC=0(プリスケーラなし)から始めなければいけない

- それが16ビット(または32ビット)の範囲以上の値を生成する場合は、ARRが適合するまで PSCを増加させる必要がある

このスライドでは、タイマのPWM周波数を設定する方法について説明します。

このパラメータは、TIMx\_ARRレジスタにプログラムされたオートリロード値(ARR)とTIMx\_PSCレジスタにプログラムされたクロック・プリスケーラを使用して定義されます。

PWM周波数は、タイマ動作周波数(fTIM)をARR+1で割った値にクロックプリスケーラ+1を乗じた値で与えられます。

実質的には、両方のレジスタ値を見つけることは反復処理であり、 PSC=0から開始しなければなりません。これにより、PWMは可能な限り 最高の分解能を持つことが保証されています。

この場合のARR値は、単純にタイマクロック周波数とPWM周波数の比であり、全体から1を引いた値となります。

この式でタイマのARR範囲を超えるARR値(選択されたタイマに応じて16ビットまたは32ビットの値)が得られた場合、以下のシーケンスで、より高いプリスケーラ値で計算をやり直さなければなりません。

タイマクロック周波数をPWM周波数で2で割った値をマイナス1とし、タイマクロック周波数をPWM周波数で3で割った値をマイナス1とし、ARR値がプログラム可能な範囲内に収まるようにしたものです。

## いくつかの有用な数式2/2 49

- デューティサイクル設定

- 自動リロード(ARR、TIMx\_ARR) とコンペア値 (PSC、TIMx\_CCRx) で定義されている デューティサイクル =  $\frac{CCRx+1}{ARR+1}$   $\Rightarrow$  CCRx =  $\left($ デューティサイクル  $\times$  (ARR+1) $\right)-1$

- PWM分解能

- この分解能は、可能なデューティサイクル値の数を与え、PWM信号の制御をどの程度細かくするかを 示す

$$Res_{(ステップ)} = \frac{f_{TIM}}{f_{PWM}}$$

• 別の表現方法としては、D/Aコンバータの出力分解能を与えるためのように、ビット単位で表現出来る

$$Res_{(\stackrel{\leftarrow}{\text{Lin}})} = log_2(\frac{f_{TIM}}{f_{PWM}})$$

このスライドでは、与えられたPWM周波数のデューティサイクルをプログラムする方法を説明します。

このパラメータは、TIMx\_ARRレジスタにプログラムされたオート リロード値(ARR)とTIMx\_CCRxレジスタにプログラムされたコン ペア値を使用して定義されます。

デューティサイクルはPWM周波数に依存せず、オートリロード値+1に対する比較値+1で与えられます。

もう一つの有用な指標は、PWM分解能です。

これは可能なデューティサイクル値の数を示し、PWM信号の制御がどの程度細かくなるかを示します。デューティサイクルのステップ数で表される分解能は、タイマクロック周波数とPWM周波数の比、つまり全体からマイナス1を引いた値に単純に等しくなります。

それを表現する別の方法は、D/Aコンバータの出力分解能を与えるような、ビットでの表現です。この場合、分解能は、タイマクロック周波数とPWM周波数の間の比率の基本2対数、全体のマイナス1です。

# アプリケーションの例:LEDの調光

TIM1 CH1

STM32

- PWM周波数:1kHz

- 周波数:  $ARR = \frac{f_{TIM}}{f_{PWM}} 1 = \frac{128MHz}{1kHz} 1 = 127999$

- ARRが最大16ビット値を超えた

- ・ プリスケーラは1に設定する必要がある

- $ARR = \frac{f_{TIM}/2}{f_{PWM}} 1 \Rightarrow ARR = \frac{128MHz/2}{1kHz} 1 = 63999$

・ デューティサイクル =

$$\frac{CCRx+1}{ARR}$$

$\Rightarrow$   $CCRx$  =  $\Big((ARR+1) \times$ デューティサイクル $\Big)-1$  =  $\Big((64000) \times 0.2\Big)-1=12799$

- 調光分解能

- 64000ステップもしくはlog<sub>2</sub>(64000)=15.9ビット

このスライドでは、低消費電力LEDの調光にPWMを使用した簡単な実用例を示しています。

これは、電流が定格出力電流を超えない限り、PWM出力を直接使用して行うことができます。

最初のステップでは、周波数を1kHzに設定するようにプログラムします。プリスケーラなし、タイマ動作周波数128MHzでARR値の計算を行うと、結果は127999となり、タイマ1で使用できる16ビットの範囲を超えています。

タイマを64MHzで動作させるためには、タイマ・プリスケーラを1に設定する必要があり、これによりARRレジスタの有効な値は63999になります。

2番目のステップでは、20%のデューティサイクルを持つようにコンペアレジスタの値を計算します。これにより、12799の値が得られます。最後に、調光分解能は前のスライドで紹介した計算式から計算できます。タイマを64MHzで動作させると、1kHzのPWMで640000回の調光ステップが得られ、これは15.9ビットの分解能に相当します。

- タイマ全体が設定され、カウンタが起動し、PWMモードが有効になり、対応する出力 も有効になっていますが、ピンにはまだ何も動作していない場合

- →MOEビットとCCxEビットの設定は検討しましたか?

- デッドタイム・ジェネレータを搭載したタイマの場合、TIMx BDTRレジスタのメイン出 カイネーブル(MOE)ビットはすべての出力を制御し、ブレーク入力で障害が検出さ れた場合にはサーキット・ブレーカとして機能 (すべてのPWM出力をグローバルにディセーブルにする)

- →出力を有効にするには、MOEビットを設定(セット)する必要がある

- →デッドタイムを挿入せずにタイマを使用している場合でも有効

このスライドでは、タイマ全体を設定し、カウンタを起動し、PWM モードを有効にし、対応する出力も有効にしているが、ピンには何 も動作していないというよくあるサポートケースを説明しています。 通常、これはMOEビットまたはCCxEビットが設定されていないため です。

TIMxCCERレジスタのCCxEビットは、CCxチャネルの入力または出 力としての構成を定義します。CC1Eビットは、CH1チャネルでPWM 信号を得るために設定する必要があります。

デッドタイム・ジェネレータを搭載したタイマの場合、TIMx BDTRレ ジスタのメイン出力イネーブル(MOE)ビットはすべての出力を制御 し、ブレーク入力で障害が検出された場合にはサーキットブレーカ として機能します(すべてのPWM出力をグローバルにディセーブル にする)。

出力を有効にするには、MOEビットを設定(セット)する必要があり ます。

これは、タイマがデッドタイム挿入なしで使用され、タイマが汎用ア プリケーションに使用される場合でも有効です。

|          |      |                                                                                              |      | 5 I IVI | 320                                       | <del>5</del> 45         | イマ   | <u> </u> | ン     | <u>人"</u>                   | シンス        | 幾能■         |  |

|----------|------|----------------------------------------------------------------------------------------------|------|---------|-------------------------------------------|-------------------------|------|----------|-------|-----------------------------|------------|-------------|--|

| 機能       |      | TIM1                                                                                         | TIM8 | TIM20   | TIM2                                      | TIM3                    | TIM4 | TIM5     | TIM6  | TIM7                        | TIM15      | TIM16 TIM17 |  |

|          |      | (高機能)                                                                                        |      |         | (汎用)                                      |                         |      |          | (基本)  |                             | (汎用)       |             |  |

| クロック・ソース |      | CK_INT<br>外部入カピン<br>外部トリガ入カETR                                                               |      |         | CK_INT<br>外部入力ピン<br>外部トリガ入力ETR<br>内部トリガ入力 |                         |      | CK_INT   |       | CK_INT<br>外部入カピン<br>内部トリガ入カ |            |             |  |

| 分解能      |      | 16ビット                                                                                        |      |         | 32ビット                                     | 32ビット 16ビット 16ビット 32ビット |      |          | 16ビット |                             | 16ビット      |             |  |

| プリスケーラ   |      | 16ビット                                                                                        |      |         |                                           |                         |      |          |       |                             |            |             |  |

| カウンタブ    | 前    | アップ、ダウン、アップ&ダウン                                                                              |      |         | アップ、ダウン、アップ&ダウン                           |                         |      |          | アップ   |                             | アップ        |             |  |

| 繰り返した    | コウンタ | ✓                                                                                            |      |         | -                                         |                         |      |          | -     |                             | ✓          |             |  |

| 同期       | マスタ  |                                                                                              | ✓    |         | ✓                                         |                         |      |          | ✓     |                             | ✓          |             |  |

|          | スレーブ |                                                                                              | ✓    |         | ✓                                         |                         |      |          | -     |                             | <b>√</b> - |             |  |

| チャネル数    |      | 6:<br>> CH1/CH1N<br>> CH2/CH2N<br>> CH3/CH3N<br>> CH4/CH4N<br>> CH5およびCH6出力のみ、<br>外部では使用できない |      |         | 4:<br>> CH1<br>> CH2<br>> CH3<br>> CH4    |                         |      | 0        |       | 2: 1: > CH1/CH1N > CH2      |            |             |  |

| トリガ入力    |      | ✓                                                                                            |      |         | ✓                                         |                         |      |          | _     |                             | ✓          | ✓           |  |

このスライドでは、STM32G4マイコンに搭載されているタイマインスタンスの一覧を示しています。

タイマ1、8および20は、すべてのPWMオプションと同時に3相 PWM信号を生成し、2つの独立したA/Dコンバータトリガを持つことができる6つのコンペアチャネルを含む、フル機能を備えたタイマ、モータ制御が可能です。

タイマ15、16、17は汎用タイマになります。

タイマ15だけが、補完的なチャネルと高度なPWMモードをサポートします。

タイマ2、3、4、5は、高度なPWMモード、アップダウンカウント機能、4チャネルを備えた汎用タイマです。タイマ2と5は、さらに32ビットのカウント範囲を提供します。

最後に、タイマ6と7は出力のない純粋なタイムベースで、主に D/Aコンバータをトリガしたり、ソフトウェアのタイムベースを提 供するために使用されます。

#### STM32G4タイマ・インスタンス機能 ■53

| 機能             | TIM1 TIM8 TIM20                            | TIM2 TIM3 TIM4 TIM5 | TIM6 TIM7 | TIM15 TIM          | /116 TIM1 |  |

|----------------|--------------------------------------------|---------------------|-----------|--------------------|-----------|--|

|                | (高機能)                                      | (汎用)                | (基本)      | (汎用)               |           |  |

| 入力キャプチャモード     | ✓                                          | ✓                   | -         | ✓                  |           |  |

| PWM入力モード       | ✓                                          | ✓                   | -         | ✓                  | -         |  |

| 強制出力モード        | ✓                                          | ✓                   | -         | ✓                  |           |  |

| 出力コンペアモード      | ✓                                          | ✓                   | -         | ✓                  |           |  |

| PWM            | 標準<br>非対称<br>組み合わせ<br>3相の組み合わせ<br>6ステップPWM | 標準<br>非対称<br>組み合わせ  | -         | 標準<br>非対称<br>組み合わせ | 標準        |  |

| PWMディザリングモード   | ✓                                          | ✓                   |           | ✓                  | ✓         |  |

| プログラム可能なデッドタイム | ✓ (CH1-4)                                  | -                   | -         | ✓ (CH1) -          |           |  |

| ブレーク入力         | 2双方向                                       | 0                   | 0         | 1双方向               |           |  |

| ワンパルスモード       | ✓                                          | ✓                   | -         | ✓                  |           |  |

|                | ✓                                          | <b>√</b>            | _         | <b>√</b> -         |           |  |

入力キャプチャと出力コンペアは、タイマ6と7ではサポートされていません。

PWMが可能なタイマであれば、ディザリングモードをサポートしています。

タイマに補完出力がある場合、プログラマブルデッドタイムは、 タイマ1、8、20(チャネル1~4)およびタイマ15(チャネル1)の場 合に適しています。

タイマ1、8、20、15、16、17はブレーク入力をサポートしています。

再トリガ可能なワンパルスモードは、タイマ16、17ではサポート されていません。

### STM32G4タイマ・インスタンス機能 54

| 機能                    | TIM1                           | TIM8 | TIM20                          | TIM2 | TIM3 | TIM4 | TIM5 | TIM6 | TIM7 | TIM15 | TIM16 | TIM17 |

|-----------------------|--------------------------------|------|--------------------------------|------|------|------|------|------|------|-------|-------|-------|

|                       | (高機能I)                         |      | (汎用)                           |      |      |      | (基   | 本)   | (汎用) |       |       |       |

| エンコーダ・インタフェース・モード     | 直交エンコーダ<br>クロックプラス方向<br>方向クロック |      | 直交エンコーダ<br>クロックプラス方向<br>方向クロック |      |      |      |      | -    | -    |       |       |       |

| インデックス入力              | ✓                              |      |                                | ✓    |      |      |      |      | -    | -     |       |       |

| エンコーダ·エラー·マネージメ<br>ント |                                | ✓    |                                |      | ✓    |      |      |      | -    | -     |       |       |

| タイマ入力XOR機能            |                                | ✓    |                                |      | -    |      | -    |      | -    | ✓     |       | -     |

| DMA                   |                                | ✓    |                                |      | ✓    |      |      | ,    | /    | ✓     |       |       |

タイマ1、8、20、2、3、4、5だけが3モードのエンコーダインタフェースを備えています:直交エンコーダ、クロックプラス方向と方向クロック。

このエンコーダインタフェースを持つタイマは、インデックスパルスをサポートし、エンコーダエラーを検出します。

チャネルを結合するXOR機能は、タイマ1、8、20、15でのみ使用可能です。

基本タイマを含め、すべてのタイマはDMAMUXユニットを介してDMA転送を要求することができます。

#### 関連ペリフェラル 🛂

- タイマと連動する以下のペリフェラルについては、トレーニング資料を参照してください。

- A/Dコンバータ

- タイマはインジェクトとレギュラ変換をトリガする

- PWMはアナログ・ウォッチドッグによって止めることが可能

- D/Aコンバータ

- タイマが変換開始をトリガ

- 相互接続マトリクス

- ペリフェラル間の直接接続を制御

- RCC

- RCCはタイマ内部クロック・リファレンスを提供

- COMP

- ・ コンパレータ出力はブレーク・イベントをトリガ可能

タイマは複数のオンチップペリフェラルと連動しています。 A/DコンバータとD/Aコンバータのトリガ・ソースとして機能します。

相互接続マトリックスは、マスタとスレーブのインタフェースを使用して、タイマとタイマの直接接続を可能にし、また、タイマと他のペリフェラル間の直接接続を可能にします。

RCCと呼ばれるリセット・クロック・コントロール・ユニットは、すべてのタイマの内部クロックリファレンスを提供します。

最後に、コンパレータユニットは、異常な温度または電圧状態 を検出し、タイマブレークイベントを発生させることができます。

- 詳細は、以下の資料をご参照ください。

- AN2592

- STM32F10xおよびSTM32L15xマイクロコントローラでリンクシステムを使用して32ビットタイマ分解能を 実現する方法 (含まれているソフトウェア:STSW-STM32009)

- AN4013

- STM32クロスシリーズタイマの概要

- AN4507

- STM32アドバンスド・コンフィグレーション、汎用およびライトタイマのためのディザリング技術によるPWM 分解能の向上(含まれているソフトウェア:STSW-STM32151)

- AN4776

- 汎用タイマクックブック

- AN4507

- ディザリング技術によるPWM分解能の向上

3つのアプリケーションノートは、リファレンスマニュアルのタイマセクションを補完します。

AN2592は、2つの16ビットタイマを同期させた32ビットタイマの実用的な実装方法を示しており、タイマ同期機構全体の理解を深めるのに役立ちます。ソフトウェア例が付属しています。AN4013では、すべてのタイマ機能と利用可能なファームウェアの例について、より詳細な概要を説明しています。

AN4507では、ディザリング技術を用いたPWM分解能向上の実装を紹介しています。ソフトウェアの例が付属しています。

AN4776は、タイマの動作原理についてのいくつかの注意事項から始まり、標準的なタイマの使用例を集めています。ソフトウェアの例が付属しています。

AN4507ではPWMの分解能を向上させるディザリング技術を紹介しています。ソフトウェア例が付属しています。