こんにちは。STM32 I<sup>2</sup>Cインタフェース(SAI)のプレゼンテーションへようこそ。このプレゼンテーションでは、マイコン、センサ、シリアルインタフェースメモリなどのデバイスを接続するために広く使用されている、この通信インタフェースの主な機能について説明します。

## 概要:

- I<sup>2</sup>C通信インタフェースを提供

- I<sup>2</sup>Cバス仕様およびユーザマニュアル、リビジョン3

- 標準、高速、および高速モードプラス(1MHz)

- SMBus2.0ハードウェアサポート

- PMBus1.1互換性

### アプリケーション側の利点

- 使いやすいイベント管理

- 完全にプログラム可能なタイミング値

- 低電力STOPモードで動作可能

I<sup>2</sup>Cインタフェースは、NXP I<sup>2</sup>Cバス仕様およびユーザマニュアル(リビジョン3)、SMBusシステム管理バス仕様(リビジョン2)、PMBus電カシステム管理プロトコル仕様(リビジョン1.1)に準拠しています。

このペリフェラルは、使いやすいインタフェース、非常にシンプルなソフトウェアプログラム、および完全なタイミングの柔軟性を備えています。また、I<sup>2</sup>C ペリフェラルは、低消費電力のSTOPモードで動作可能です。

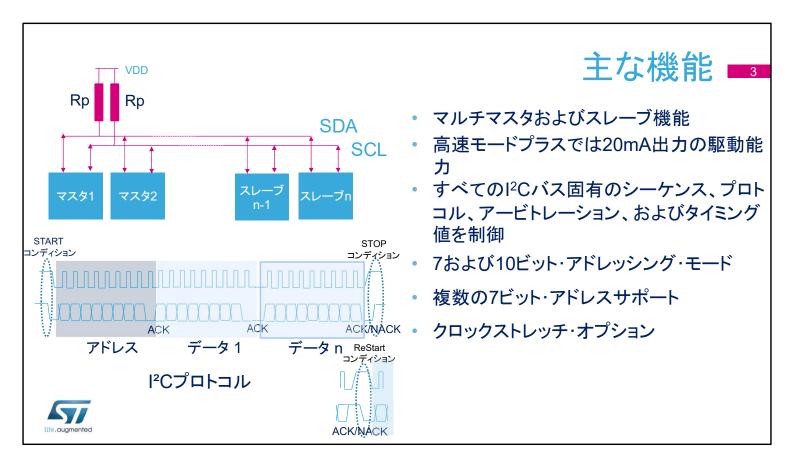

I<sup>2</sup>Cペリフェラルはマルチマスタおよびスレーブモードをサポートします。

I<sup>2</sup>C IOピンは、オープンドレインモードで設定される必要があります。論理ハイレベルは外部プルアップによって駆動されます。IOピンは高速モードプラスに必要な20mA出力駆動をサポートします。

ペリフェラルは、すべてのI<sup>2</sup>Cバス固有のシーケンス、プロトコル、アービトレーション、およびタイミング値を制御します。 7および10-ビットアドレッシングモードがサポートされ、同じアプリケーションで複数の7ビットアドレスをサポートできます。マスタモードのペリフェラルは、スレーブクロックストレッチとスレーブ側からのクロックストレッチをサポートします。ペリフェラルのスレーブモード構成では、クロックストレッチをソフトウェアによって無効にできます。

## 主な機能

- プログラム可能なセットアップおよびホールド時間

- SCLおよびSDAラインでのプログラム可能なアナログおよびデジタルノイズ·フィルタ

- アドレス一致時にSTOPモードからウェイクアップ

- 独立クロックにより、システムクロックから独立した通信ボーレートが可能

- I2C4は、D3ドメインの自律モードに対応

セットアップおよびホールド時間は、ソフトウェアによるプログラムが可能です。

データおよびクロックラインのアナログおよびデジタルグリッチフィルタをソフトウェアによって設定できます。

ペリフェラルは、アドレス一致が検出されたとき、MCUをSTOPモードからウェイクアップできます。

ペリフェラルは独立したクロックドメインを持つため、システム クロックから独立した通信ボーレートが可能です。

I2C4は、低消費電力のD3ドメインに配置されており、低消費電力のアプリケーションでは自律モードで使用することができます。

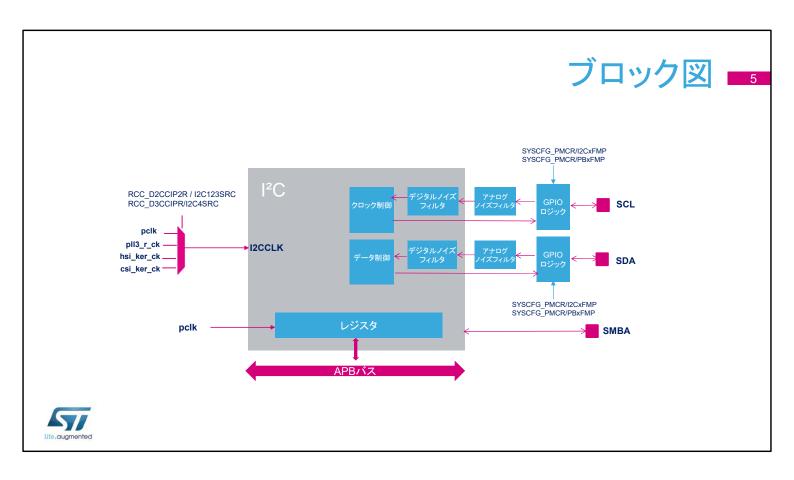

これは、I<sup>2</sup>Cブロック図です。レジスタはAPBバスを介してアクセスされ、ペリフェラルはAPBクロックから独立したI<sup>2</sup>Cクロックからクロック供給されます。I<sup>2</sup>Cクロックは、PLL、APBクロック、8~64MHzの高速内蔵RCオシレータ、および低消費電力の4MHz内蔵RCオシレータから選択できます。 SCLおよびSDAラインには、アナログおよびデジタルノイズフィルタがあります。20mAの駆動能力は、システム設定レジスタの制御ビットを使用して有効にできます。さらに、SMBusモードではSMBusアラートピンが使用可能です。

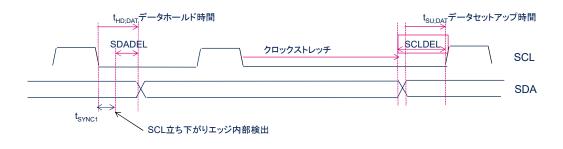

## I<sup>2</sup>Cプログラム可能タイミング

#### タイミング生成における完全な柔軟性

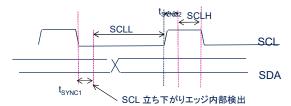

- 送信時のSDAおよびSCLライン間のセットアップおよびホールド時間は、I<sup>2</sup>Cタイミング・レジスタ(I2C\_TIMINGR)のPRESC、SDADEL、およびSCLDELフィールドでプログラム可能

- SDADELはデータホールド時間の生成に使用。t<sub>SDADEL</sub> = [SDADEL \* (PRESC+1) + 1] \* t<sub>l2CCLK</sub>

- SCLDEL はデータセットアップ時間の生成に使用。t<sub>SCLDEL</sub> = (SCLDEL+1) \* (PRESC+1) \* t<sub>I2CCLK</sub>

I<sup>2</sup>Cのセットアップおよびホールド時間は、I<sup>2</sup>Cタイミングレジスタを介してソフトウェアによって設定できます。

SDADELおよびSCLDELカウンタは、最小のデータホールド時間とデータセットアップ時間を保証するために、送信時に使用されます。

I<sup>2</sup>Cペリフェラルは、クロックラインの立ち下がりエッジを検出した後、プログラムされたデータホールド時間だけ待ってからデータを送信します。データの送信後、プログラムされたデータセットアップ時間の間、クロックラインはローにストレッチされます。

合計のデータホールド時間は、プログラムされたSDADELカウンタより大きくなります。これは、SCL立ち下がりエッジが内部で検出されて初めて、SDADEL遅延が追加されるためです。この内部検出に必要な時間(t<sub>SYNC1</sub>)は、SCL立ち下がりエッジ、フィルタによる入力遅延、および内部SCLとl<sup>2</sup>Cクロックとの同期による遅延に依存します。ただし、セットアップ時間は、これらの内部遅延の影響を受けません。

# I<sup>2</sup>Cマスタ·クロック生成 I

#### マスタクロック生成における完全な柔軟性

- I2C TIMINGRによりSCLローおよびハイ時間をプログラム可能

- SCLローカウンタ: (SCLL+1) \* (PRESC+1) \* t<sub>I2CCLK</sub>

- SCLの立ち下がりエッジの内部検出後にカウントを開始

- カウント後、SCLはリリース

- SCLハイカウンタ: (SCLH+1)\*(PRESC+1)\*t<sub>I2CCLK</sub>

- SCLの立ち上がりエッジの内部検出後にカウントを開始

- カウント後、SCLはローに駆動

- SCL period = t<sub>SYNC1</sub> + t<sub>SYNC2</sub> + [(SCLL+1) + (SCLH+1)] \* (PRESC+1) \* t<sub>I2CCLK</sub>

I<sup>2</sup>C マスタクロックのローおよびハイレベル時間は、I<sup>2</sup>Cタイミングレジスタでソフトウェアによって設定されます。 SCLローおよびハイレベルカウンタは、SCLラインのエッジの検出後に開始します。この実装により、ペリフェラルはマルチマスタ環境でマスタクロック同期メカニズムをサポートでき、スレーブクロックストレッチ機能もサポートできます。したがって、合計のSCL周期はカウンタの合計より大きくなります。これは、SCLラインのエッジの内部検出による遅延の追加に関係しています。これらの遅延、つまり、t<sub>SYNC1</sub>とt<sub>SYNC2</sub>は、SCLの立ち下がりまたは立ち上がりエッジ、フィルタによる入力遅延、および内部SCLとI<sup>2</sup>Cクロックとの同期による遅延に依存します。

立ち上がりエッジは、プルアップレジスタとSCLラインのキャパシタンスに依存します。立ち下がりエッジは、データシートで定義されたI/Oポートのパラメータに依存します。クロック速度を適切に設定するために、これらのエッジを測定または計算できます。STM32CubeMXツールでI<sup>2</sup>Cペリフェラルを適切に設定するために必要であり、その後、タイミングレジスタの設定は、このツールによって自動的に計算できます。

# スレーブ・アドレッシング・モード ---

#### 多数のスレーブ・アドレス

- I<sup>2</sup>Cは複数のスレーブ・アドレスを認識可能。2つのアドレス・レジスタ:

- I2C\_OAR1:7または10ビット・モード

- I2C OAR2:7ビット・モードのみ。OA2MSK[2:0]によりOAR2の0~7LSBをマスク可能

| OA2MSK [2:0] | アドレス一致条件                                    |  |  |

|--------------|---------------------------------------------|--|--|

| 000          | アドレス [7:1] = OA[7:1]                        |  |  |

| 001          | アドレス [7:2] = OA[7:2](ビット 1 は無視)             |  |  |

| 010          | アドレス [7:3] = OA[7:3](ビット 2:1 は無視)           |  |  |

|              |                                             |  |  |

| 111          | I <sup>2</sup> C 予約済みアドレスを除き、すべてのアドレスが認識される |  |  |

I<sup>2</sup>Cスレーブは複数のスレーブアドレスを認識できます。スレーブアドレスは2つのレジスタにプログラムされます。自己アドレスレジスタ1は、7または10ビットアドレスでプログラムできます。自己アドレスレジスタ2は、7ビットアドレスでプログラムできますが、このアドレスの最下位ビットをOA2MSKレジスタを介してマスクし、複数のスレーブアドレスを認識させることができます。2つの自己アドレスレジスタを同時に有効化できます。

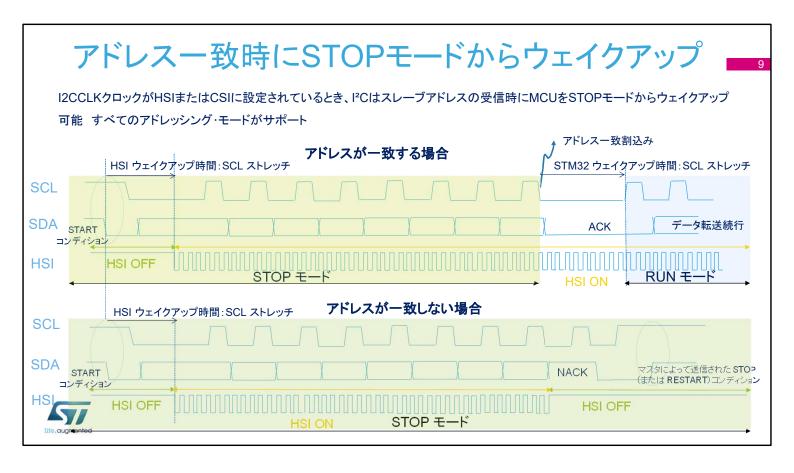

I<sup>2</sup>Cペリフェラルは、アドレス一致時のSTOPモードからのウェイクアップをサポートします。このためには、I<sup>2</sup>CペリフェラルクロックをHSIもしくはCSIオシレータに設定する必要があります。STOPからのウェイクアップ機能が有効な時には、アナログノイズフィルタのみがサポートされます。すべてのアドレッシングモードがサポートされます。

デバイスがSTOPモードのとき、高速内部オシレータはオフになります。STARTコンディションが検出されると、I<sup>2</sup>Cペリフェラルは高速内部オシレータを有効にし、それを使用してバス上のアドレスを受信します。

STOPモードでアドレスが受信された後、アドレスがプログラムされた スレーブアドレスに一致した場合、ウェイクアップ割込みが生成されま す。

アドレスが一致しなかった場合、高速内部オシレータはオフになり、 割込みは生成されず、デバイスはSTOPモードのままです。

I<sup>2</sup>CペリフェラルはSTARTコンディション後、高速内部オシレータが開始するまでクロックラインをローにストレッチするので、クロックストレッチを有効にする必要があります。プログラムされたスレーブアドレスに一致するアドレスを受信した後、I<sup>2</sup>CペリフェラルはSTM32H7デバイスがウェイクするまで、クロックラインをローにストレッチします。

# シンプルなマスタモード管理

#### ペイロードが255バイト以下の場合、必要な書込み回数は1回のみ

- START = 1

- SADD: スレーブアドレス

- RD WRN: 転送方向

- NBYTES = N: 転送されるバイト数

- AUTOEND = 1:N データ後、STOPを自動送信

| AUTOEND       | 説明                                                                                                                |

|---------------|-------------------------------------------------------------------------------------------------------------------|

| 0:ソフトウェア終了モード | NBYTESバイトのデータが転送された後、転送終了をソフトウェアで制御:<br>転送完了(TC)フラグがセットされ、有効な場合は割込みが生成される<br>RESTARTまたはSTOPコンディションをソフトウェアによって要求可能 |

| 1:自動終了モード     | NBBYTESバイトのデータが転送された後、STOPコンディションが自動送信される                                                                         |

マスタモードでのソフトウェア管理は非常にシンプルです。1回の書込みアクションだけで、255バイト以下のペイロードのマスタ転送を処理できます。完全なプロトコルはハードウェアによって管理されます。

マスタモードで転送を開始するには、I2C制御レジスタ2に STARTコンディション要求、スレーブアドレス、転送方向、転送されるバイト数、および転送終了モードを書き込む必要があります。転送終了モードは、AUTOENDビットによって設定されます。このビットがセットされた場合、プログラムされたバイト数が転送された後、STOPコンディションが自動的に送信されます。

AUTOENDビットがセットされていない場合、転送終了はソフトウェアによって管理されます。プログラムされたバイト数が転送された後、転送完了(TC)フラグがセットされ、有効な場合、割込みが生成されます。その後、RESTARTまたはSTOPコンディションをソフトウェアによって要求できます。データ転送は、割込みまたはDMAによって管理できます。

# 使いやすいイベント管理

- ペイロードが255バイトを超える場合:I2C\_CR2のRELOADビットをセットする必要あり

- AUTOEND=0は、RELOADビットがセットされているときには効果無し

| RELOAD    | 説明                                                                                           |

|-----------|----------------------------------------------------------------------------------------------|

| 0:リロードなし  | NBYTESバイトのデータが転送された後、STOPまたはRESTARTが続く                                                       |

| 1:リロードモード | NBYTESバイトのデータが転送された後、NBYTESがリロードされ、データ転送が<br>再開される<br>転送完了リロード(TCR)フラグがセットされ、有効な場合は割込みが生成される |

ペイロードが255バイトより大きいときには、I<sup>2</sup>C制御レジスタ2のRELOADビットをセットする必要があります。この場合、プログラムされたバイト数が転送された後、転送完了リロード(TCR)フラグがセットされます。TCRビットがセットされていると、転送される追加のバイト数がプログラムされ、データ転送が再開されます。TCRビットがセットされている限り、I<sup>2</sup>Cクロックはローにストレッチされます。RELOADビットは、マスタモードではペイロードが255バイトより大きいときに使用され、スレーブモードでは、スレーブバイト制御が有効なときに使用されます。

RELOADビットがセットされているとき、AUTOENDビットは 効果がありません。

## スレーブモード

- デフォルト: I<sup>2</sup>Cスレーブはクロックストレッチを使用します。クロックストレッチはソフトウェアで無効可能

- 受信:認識制御は、RELOAD=1のとき、スレーブバイト制御(SBC)モードで選択されたバイトで実行可能

- SBC=1のとき、スレーブモード(TxおよびRxモード)のNBYTESカウンタが有効

- SBC=1は、NOSTRETCH=0のときのみ設定可能

| SBC       | 説明                                                                                       |

|-----------|------------------------------------------------------------------------------------------|

| 0:リロードなし  | NBYTESバイトのデータが転送された後、STOPまたはRESTARTが続く                                                   |

| 1:リロードモード | NBYTESバイトのデータが転送された後、NBYTESがリロードされ、データ転送が再開される<br>転送完了リロード(TCR)フラグがセットされ、有効な場合は割込みが生成される |

デフォルトでは、I<sup>2</sup>Cスレーブはクロックストレッチを使用します。クロックストレッチ機能はソフトウェアで無効にできます。

受信モードでは、スレーブによる受信バイト認識動作は、スレーブバイト制御モードが選択されていて、RELOADビットがセットされているときに設定できます。SBCビットがセットされているとき、スレーブモードでバイト数カウンタが有効になります。クロックストレッチは、スレーブバイト制御が有効なときに有効でなければなりません。受信モードでは、スレーブバイト制御が有効であり、RELOADビットがセットされていて、転送されるバイト数が1のとき、1バイト受信ごとに転送完了リロードフラグがセットされ、SCLラインがストレッチされます。これは、データ受信後、認識パルス前に行われます。受信バッファノットエンプティフラグもセットされ、データの読出しが可能になります。TCRサブルーチンでは、ACK(認識)またはNACK(非認識)がバイト受信後に送信されるようにプログラムできます。

|2Cスレーブトランスミッタモードではバイトカウンタを使用しないため、送信時はSBCビットをクリアすることを推奨します。

SMBusモードでは、スレーブバイト制御モードは、送信時、PEC (パッケージエラーコード)バイトの送信に使用されます。

#### シームレスなSMBus2.0サポート

- ARP(アドレス解決プロトコル):スレーブモードでは、デバイスのデフォルトアドレス、 アービトレーション

- ホスト通知プロトコルのサポート: ホストアドレス

- アラートのサポート: アラートピンとアラート応答のサポート

- タイムアウトとバスアイドルの検出

- SBCモードでのコマンドおよびデータ認識制御

- パケット・エラー・チェック(PEC)のハードウェア計算

I<sup>2</sup>Cペリフェラルは、SMBusのハードウェアサポートを提供します。SMBusアドレス解決プロトコルは、スレーブモードでは、デバイスのデフォルトアドレスとアービトレーションを通じてサポートされます。

ホスト通知プロトコルは、ホストアドレスサポートによってサポートされます。

アラートプロトコルは、SMBusアラートピンとアラート応答アドレスを通じてサポートされます。

SMBusクロックロータイムアウトと累積クロックロー延長時間を、プログラム可能な時間で検出できます。バスアイドル条件は、プログラム可能な時間で検出できます。

コマンドおよびデータ認識制御は、スレーブバイト制御モード を通じてサポートされます。

パケットエラーコード(PEC)バイトは、ハードウェアによって計算されます。

#### 14

# SMBus: PEC(パケット・エラー・チェック)

- PECの自動送信/チェック

- NBYTES(データ転送カウンタ)は以下のために使用

- 受信時、NBYTES-1バイトの受信後に、パケットエラーコード(PEC)バイトを自動的にチェック

- 障害時に、NACKを自動送信

- 送信時、NBYTES-1バイトの送信後に、パケットエラーコード(PEC)バイトを自動的に送信

- スレーブバイト制御モード(SBCビット)をスレーブモードにセットして、NBYTESカウンタを有効に する必要あり

パケットエラーコード(PEC)バイトは、送信時に自動送信され、 受信時に自動的にチェックされます。

データ転送カウンタは、NBYTES値で初期化され、受信時に NBYTES-1バイトを受信した後、PECバイトを自動的にチェックするために使用されます。受信したPECバイトが計算に一致しなかった場合、PECバイト後にNot Acknowledge (NACK)が自動的に送信されます。送信時は、NBYTES-1バイト後に、内部で計算されたPECバイトが自動的に送信されます。NBYTESカウンタを有効にして、PECの自動送受信を可能にするには、スレーブバイト制御モードをスレーブモードで有効にする必要があります。

## 割込みとDMA ■15

| 割込みイベント        | 説明                                              |  |  |  |

|----------------|-------------------------------------------------|--|--|--|

| 受信バッファノットエンプティ | 受信バッファに受信データがあり、読出し準備ができているときにセット               |  |  |  |

| 送信バッファ割込みステータス | 送信バッファが空であり、書込み準備ができているときにセット                   |  |  |  |

| ストップ検出         | バス上でSTOPコンディションが検出されたときにセット                     |  |  |  |

| 転送完了リロード       | RELOAD=1であり、NBYTESバイトのデータが転送されたときにセット           |  |  |  |

| 転送完了           | RELOAD=0、AUTOEND=0であり、NBYTESバイトのデータが転送されたときにセット |  |  |  |

| アドレス一致         | 受信したスレーブアドレスが有効なスレーブアドレスの1つと一致したときにセット          |  |  |  |

| NACK受信         | 1バイト送信後にNACKを受信したときに、ハードウェアによってセット              |  |  |  |

受信バッファがノットエンプティのとき、または送信バッファがエンプティのとき、DMAリクエストを 生成可能

いくつかのイベントが割込みをトリガします。

受信バッファノットエンプティフラグは、受信バッファに受信デー タがあり、読出し準備ができているときにセットされます。送信 バッファ割込みステータスは、送信バッファが空であり、書込み 準備ができているときにセットされます。STOP検出フラグは、 バス上でSTOPコンディションが検出されたときにセットされま す。

転送完了リロードフラグは、RELOARD ビットがセットされてい て、NBYTESバイトのデータが転送されたときにセットされます。 転送完了フラグは、RELOADおよびAUTOENDビットがクリア され、NBYTESバイトのデータが転送されたときにセットされま す。

アドレス一致フラグは、受信したスレーブアドレスが有効なス レーブアドレスの1つと一致したときにセットされます。

NACK受信フラグは、1バイト送信後にNot Acknowledge (NACK)が受信されたときにセットされます。

受信バッファノットエンプティまたは送信バッファエンプティフラ グがセットされたとき、DMAリクエストを生成できます。

| 割込みイベント           | 説明                                                                                                      |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| バスエラー検出           | STARTまたはSTOPコンディションの誤配置が検出されたときにセット                                                                     |  |  |  |

| アービトレーション喪失       | アービトレーション喪失のイベントでセット                                                                                    |  |  |  |

| オーバーラン/アンダーラン・エラー | スレーブモードでNOSTRETCH = 1の場合、前のバイトがまだ読み出されていない間に新しいデータを受信したとき、または新しいデータがまだ書き込まれていない間に新しいデータを送信する必要があるときにセット |  |  |  |

| SMBus:PECエラー      | 受信したPECがPECレジスタの内容に一致しないときにセット                                                                          |  |  |  |

| SMBus:タイムアウト・エラー  | タイムアウトまたは拡張クロックタイムアウトが発生したときにセット                                                                        |  |  |  |

| SMBus:アラートピン検出    | SMBHEN=1(SMBusホスト設定)、ALERTEN=1であり、<br>SMBAピンでSMBALERTイベント(立ち下がりエッジ)が検出されたときにセット                         |  |  |  |

いくつかのエラーフラグが生成されます。

バスエラー検出フラグは、STARTまたはSTOPコンディション の誤配置が検出されたときにセットされます。アービトレー ション喪失フラグは、アービトレーション喪失時にセットされま す。オーバーランまたはアンダーランエラーフラグは、スレー ブモードでクロックストレッチが無効な場合、オーバーランま たはアンダーランエラーが検出されたときにセットされます。 SMBusモードでは、PECエラーフラグは、受信したPECが計 算されたPECレジスタの内容に一致しないときにセットされま す。タイムアウトエラーフラグは、タイムアウトまたは延長ク ロックタイムアウトが検出されたときにセットされます。アラー トピン検出フラグは、SMBusホスト設定で、アラートが有効で あり、SMBAピンで立ち下がりエッジが検出されたときにセッ トされます。

# 低電力モード 17

| モード     | ·····································                   |

|---------|---------------------------------------------------------|

| RUN     | アクティブ                                                   |

| SLEEP   | アクティブ<br>ペリフェラル割込みによって、デバイスはSLEEPモードを終了                 |

| STOP    | I <sup>2</sup> Cレジスタの内容は保持                              |

| STANDBY | パワーダウン状態。STANBYまたはSHUTDOWNモード終了後にペリフェラルを再初<br>期化する必要がある |

I<sup>2</sup>Cペリフェラルは、RUNモードとSLEEPモードでアクティブになります。STOPモードでは、ペリフェラルのクロックはオフになり、レジスタの内容は保持されます。STANDBYモードでは、ペリフェラルはパワーダウンし、スタンバイモードを終了した後に再初期化する必要があります。

# デバッグ情報 📲

• DBG\_I2Cx\_STOP:コア停止時、I2Cx SMBUS タイムアウト・カウンタは停止

各I<sup>2</sup>Cペリフェラルについて、MCUデバッグコンポーネントで1 ビットをデバッグ目的に使用でき、これを使用して、コアが停 止したときにSMBUSタイムアウトカウンタを停止することがで きます。

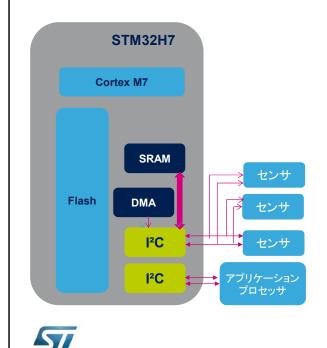

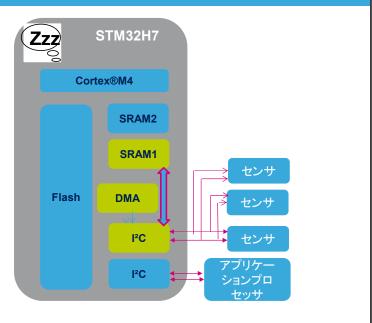

# アプリケーション例 19

#### センサハブ

- SLEEPモードのI<sup>2</sup>Cマスタがセンサと 通信

- I<sup>2</sup>Cスレーブはアプリケーション プロセッサと通信

これは、いくつかのI<sup>2</sup>Cペリフェラルを必要とするセンサハブア プリケーションの例です。

1つ以上のI<sup>2</sup>Cマスタが外部のセンサとのインタフェースに使用されます。I<sup>2</sup>Cスレーブはアプリケーションプロセッサと通信するために使用されます。

# STM32H7インスタンス機能 型

| I <sup>2</sup> Cfeatures             | I2C1 | I2C2 | I2C3 | I2C4 |

|--------------------------------------|------|------|------|------|

| 7-ビットアドレスモード                         | Х    | Х    | Х    | Х    |

| 10-ビットアドレスモード                        | Х    | X    | X    | X    |

| 標準モード(最大100kビット/秒)                   | Х    | X    | X    | X    |

| 高速モード(最大400kビット/秒)                   | X    | X    | X    | X    |

| 20mA出力駆動I/O搭載高速モードプラス<br>(最大1Mビット/秒) | Х    | X    | Х    | Х    |

| 独立クロック                               | Х    | X    | X    | X    |

| アドレス一致時にSTOPからウェイクアップ                | Х    | X    | Х    | X    |

| D3ドメインの自律モード                         |      |      |      | X    |

| SMBus                                | X    | X    | X    | X    |

X:サポート

STM32H7マイクロコントローラは4つのI<sup>2</sup>Cペリフェラルを内蔵しています。

## 関連ペリフェラル 型

- 詳細については、このペリフェラルにリンクしている以下のトレーニングを 参照ください

- システム設定コントローラ(SYSCFG)

- リセットおよびクロックコントローラ(RCC)

- 電源コントローラ(PWR)

- 割込み(NVICおよびEXTI)

- ダイレクト・メモリ・アクセス (DMA) コントローラ

- ベーシック・ダイレクト・メモリ・アクセス・コントローラ(BDMA)

- 低消費電力D3ドメイン(PWR)

このペリフェラルに関する詳細については、以下のトレーニングも参照してください。

- システム設定コントローラ

- リセットおよびクロックコントローラ

- ・ 電源コントローラ

- 割込みコントローラ

- 低消費電力D3ドメイン

- ダイレクトメモリアクセスコントローラ

- 詳細については、以下のWebページを参照してください。

- www.nxp.com:

- UM10204 I2C-bus specification and user manual

- www.sbs-forum.org

- System Management Bus (SMBus) Specification

- http://www.powersig.org/

- PMBusTM Power System Management Protocol Specification

詳細については、NXP Webサイトから、I<sup>2</sup>Cバス仕様およびユーザマニュアルを参照してください。 SMBus仕様については、Smart Battery System implementers forumを参照してください。 PMBus電カシステム管理プロトコル仕様については、Power Management Bus implementers forumを参照してください。