# STM32H7 - LTDC

LCD-TFTディスプレイ・コントローラ

1.0版

こんにちは、STM32 LCD TFTディスプレイコントローラのプレゼンテーションへようこそ。このプレゼンテーションでは、TFTディスプレイとのインターフェースに使用するLTDCコントローラのすべての機能について説明します。

- LCD TFTディスプレイ・コントローラ

- 柔軟に設定可能

- 標準パラレルRGBインターフェース

### アプリケーション側の利点

- 柔軟性のあるプログラム可能なディスプレイ・パラメータ

- 統合されたピクセル・フォーマット・コンバータとブレンダ

- オンチップ・メモリまたは外部メモリをフレームバッファとして使用可能

LCD-TFTは、液晶ディスプレイ-薄膜トランジスタ(Liquid Crystal Display-Thin Film Transistor)の略です。コントローラは柔軟に設定可能であり、標準のパラレルRGBインターフェースと接続します。

LCD TFTディスプレイコントローラの利点には、柔軟性の高いプログラム可能なディスプレイパラメータ、統合ピクセル・フォーマットコンバータ、ブレンダなどがあります。

LCD TFTディスプレイコントローラ(LTDC)のフレームバッファは、パネルの解像度に応じて、オンチップメモリまたは外部メモリに配置できます。

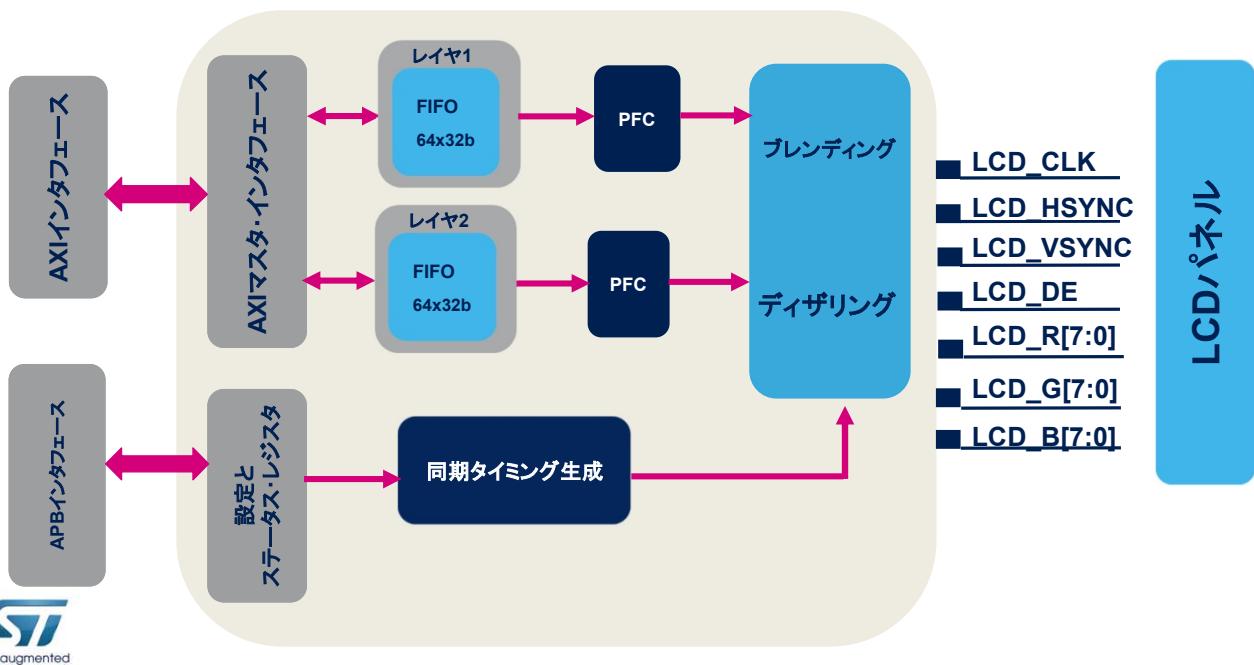

- 24ビットRGBパラレル・ピクセル出力

- ピクセルあたり8ビット(RGB888)

- 任意のシステム・メモリへの16ダブルワードのバーストアクセスが可能なAXIマスタインターフェース

- レイヤごとの専用64ダブルワードFIFO

- プログラム可能なタイミングと極性により、さまざまなディスプレイ・パネルと接続が可能

- タイミング: HSYNC幅、VSYNC幅、VBP、HBP、VFP、HFP

- 極性: HSYNC、VSYN、非データイネーブル、ピクセルクロック

- TFTのみサポート(STNは対象外)

LCD-TFTディスプレイコントローラは、24ビットパラレルデジタルRGB(赤、緑、青)インターフェースを提供し、水平および垂直同期用の追加信号も備えています。

LTDCはAXIバスマトリックスのマスタであり、内部Flash、SRAM1、SRAM2などの内部メモリ、またはFMC/QUADSPIインターフェースを経由して外部メモリにアクセスできます。

また、レイヤごとに専用の64ダブルワードFIFOも備えています。プログラム可能なタイミングと極性パラメータをサポートし、さまざまなディスプレイパネルと相互接続を行います。

# 柔軟性の高いLTDCパラメータ

4

## さまざまなディスプレイパネルに適合

- プログラム可能なウィンドウ位置とサイズ

- プログラム可能なバックグラウンド・カラー

- ボトムレイヤとのブレンドに使用される、LCDコントローラレジスタ(LTDC\_BCCR)にプログラミングされた24ビットのRGB値

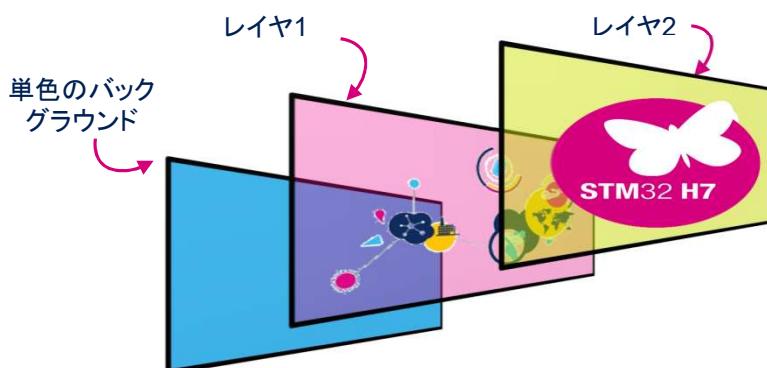

- 2レイヤ・ブレンディングによるマルチレイヤ・サポート

- カラー・チャネルごとに2ビットのディザリング(RGBでは2、2、2)

- 新しいプログラム値は、実行時または垂直ブランкиング中にすぐにロード可能

LTDCは、さまざまなディスプレイパネルをサポートできる柔軟でプログラム可能なパラメータを提供します。

- プログラム可能なディスプレイサイズ。例えば: QVGA、WQVGA、VGA

- プログラム可能なバックグラウンドカラー

- ボトムレイヤとのブレンドに使用される、LCDコントローラレジスタ(LTDC\_BCCR)にプログラミングされた24ビットのRGB値

- 2レイヤブレンディングによるマルチレイヤサポート

- カラー・チャネルごとに2ビットのディザリング(RGBでは2、2、2)

疑似乱数ディザリングを使用して各ピクセルカラーチャネル(R、G、またはB)値に小さな乱数値(閾値)を加えて18ビットディスプレイで24ビットデータを表示するため、場合により最上位ビットが切り上げられます。

- 新しいプログラム値は、実行時または垂直ブランкиング中にすぐにロードできます。

# LCD-TFTのブロック図

5

これは、LCD TFTコントローラのブロック図です。

# LTDCクロック・ドメイン

6

- 3つのクロック・ドメイン:

- AXIクロック・ドメイン(ACLK)

- メモリからレイヤFIFOとフレームバッファにデータを転送

- APBクロックドメイン(PCLK)

- グローバル設定および割込みレジスタにアクセス

- ピクセルクロックドメイン(LCD\_CLK)

- LCD-TFTインターフェース信号、ピクセルデータ、およびレイヤ設定を生成

- LCD\_CLK出力は、パネルの要件に従って設定する必要がある

LTDCには3つのクロックドメインがあります:

-メモリからレイヤFIFOおよびフレームバッファにデータを転送するAXIクロックドメイン(ACLK)

-グローバル設定および割込みレジスタにアクセスするためのAPBクロックドメイン(PCLK)

-LCD-TFTインターフェース信号、ピクセルデータ、およびレイヤ設定を生成するピクセルクロックドメイン(LCD\_CLK)

LCD\_CLK出力は、パネル要件に従って設定する必要があります。

# プログラム可能なLTDCのタイミング

7

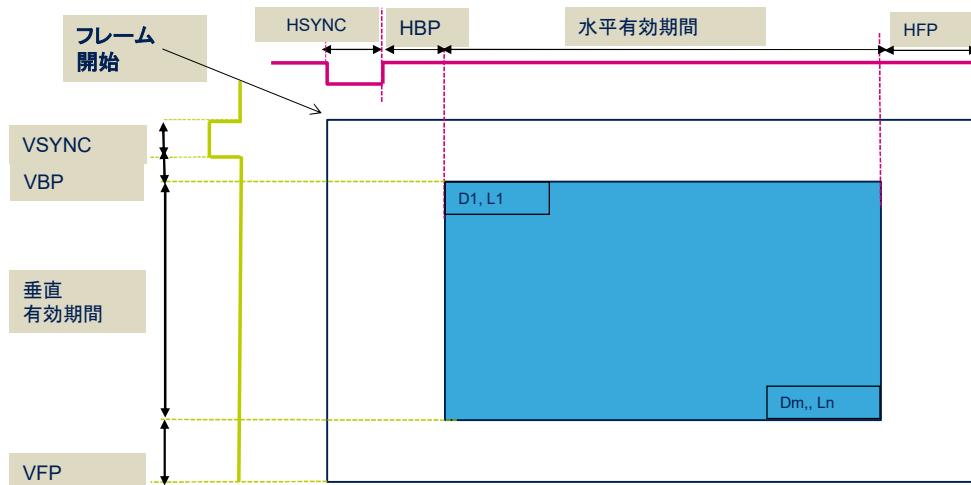

VBP: Vertical back porch (垂直バックポーチ)

VFP: Vertical front porch (垂直フロントポーチ)

HBP: Horizontal back porch (水平バックポーチ)

HFP: Horizontal front porch (水平フロントポーチ)

HSYNC: Horizontal synchronization (水平同期)

VSYNC: Vertical synchronization (垂直同期)

これらのタイミングは、ディスプレイのデータシートに基づく

例：

| Parameters                 | Symbols | Condition | Min. | Typ. | Max. | Units  |

|----------------------------|---------|-----------|------|------|------|--------|

| Horizontal Synchronization | HSync   |           | 2    | 10   | 16   | DOTCLK |

| Horizontal Back Porch      | HBP     |           | 2    | 20   | 24   | DOTCLK |

| Horizontal Address         | HAddr   |           | -    | 240  | -    | DOTCLK |

| Horizontal Front Porch     | HFP     |           | 2    | 10   | 16   | DOTCLK |

| Vertical Synchronization   | VSync   |           | 1    | 2    | 4    | Line   |

| Vertical Back Porch        | VBP     |           | 1    | 2    | -    | Line   |

| Vertical Address           | VAddr   |           | -    | 320  | -    | Line   |

| Vertical Front Porch       | VFP     |           | 3    | 4    | -    | Line   |

TFTパネルと相互接続するため、すべてのタイミングはLTDCコントローラによりプログラムできます。TFTパネルのデータシートに基づくこれらのタイミングは次の通りです：

VBP: Vertical Back porch (垂直 バックポーチ)

VFP: Vertical Front porch (垂直 フロントポーチ)

HBP: Horizontal Back porch (水平 バックポーチ)

HFP: Horizontal Front porch (水平 フロントポーチ)

HSYNC: Horizontal synchronization (水平同期)

VSYNC: Vertical synchronization (垂直同期)

## 柔軟性のあるI/O設定

| LCD-TFT信号  | 説明         |

|------------|------------|

| LCD_CLK    | ピクセルクロック出力 |

| LCD_HSYNC  | 水平同期       |

| LCD_VSYNC  | 垂直同期       |

| LCD_DE     | 非データイネーブル  |

| LCD_R[7:0] | 8ビットの赤のデータ |

| LCD_G[7:0] | 8ビットの緑のデータ |

| LCD_B[7:0] | 8ビットの青のデータ |

LTDC出力信号がこの表にまとめられています。

LTDCのピンは、ユーザアプリケーションで設定する必要があります。使用されていないピンは、他の目的に使用できます。

# ピクセルデータマッピングとカラー・フォーマット

9

## 8つのプログラム可能な入力カラー・フォーマット

|          | 31:24               | 23:16               | 15:8                | 7:0             |           |         |         |         |         |         |

|----------|---------------------|---------------------|---------------------|-----------------|-----------|---------|---------|---------|---------|---------|

| ARBG8888 | Ax[7:0]             | Rx[7:0]             | Gx[7:0]             | Bx[7:0]         |           |         |         |         |         |         |

| RGB888   | Bx+1[7:0]           | Rx[7:0]             | Gx[7:0]             | Bx[7:0]         |           |         |         |         |         |         |

| RGB565   | Rx+1[4:0]           | Gx+1[5:3]           | Gx+1[2:0]           | Bx+1[4:0]       | Rx[4:0]   | Gx[5:3] | Gx[2:0] | Bn[4:0] |         |         |

| ARGB1555 | Ax+1[0]             | Rx+1[4:0]           | Gx+1[4:3]           | Gx+1[2:0]       | Bx+1[4:0] | Ax[0]   | Rx[4:0] | Gx[4:3] | Gx[2:0] | Bx[4:0] |

| ARGB4444 | Ax+1[3:0]           | Rx+1[3:0]           | Gx+1[3:0]           | Bx+1[3:0]       | Ax[3:0]   | Rx[3:0] | Gx[3:0] | Bx[3:0] |         |         |

| L8       | Lx+3[7:0]           | Lx+2[7:0]           | Lx+1[7:0]           | Lx[7:0]         |           |         |         |         |         |         |

| AL88     | Ax+1[7:0]           | Lx+1[7:0]           | Ax[7:0]             | Lx[7:0]         |           |         |         |         |         |         |

| AL44     | Ax+3[3:0] Lx+3[3:0] | Ax+2[3:0] Lx+2[3:0] | Ax+1[3:0] Lx+1[3:0] | Ax[3:0] Lx[3:0] |           |         |         |         |         |         |

レイヤのフレームバッファ内に保存されるデータには、プログラム可能なピクセル・フォーマットが使用されます。

この表は、ピクセルデータマッピングと選択した入力カラー・フォーマットを示しています。

LTDCは、レイヤごとに最大8つのプログラム可能な入力カラー・フォーマットで設定できます。

ダイレクトカラー

ARGB8888

RGB888

RGB565

ARGB1555

ARGB4444

インダイレクトカラー

L8(8ビット輝度またはCLUT)

AL44(4ビットアルファ+4ビット輝度)

AL88(8ビットアルファ 8ビット輝度)

# ピクセル・フォーマット変換 (PFC:Pixel Format Conversion)

10

## ピクセル・フォーマット変換

### RGB565入力ピクセル・フォーマット

ビット位置

### ARGB8888内部ピクセル・フォーマット

ビット位置

ビットマップのカラー・フォーマットを別のフォーマットに変換する場合、この操作はピクセル・フォーマット変換(PFC:Pixel Format Conversion)と呼ばれます。

フレームバッファから読み取ったピクセルデータは、次のように内部ARGB8888フォーマットに変換されます。幅が8ビット未満のコンポーネントは、ビットレプリケーションによって8ビットまで拡張されます。上位8ビットが選択されます。

ダイレクトカラーからインダイレクトカラーまたはインダイレクトカラーからダイレクトカラーに変換するのは簡単ですが、ダイレクトカラーをインダイレクトカラー・フォーマットに変換する際、非常に複雑な操作であるカラールックアップテーブル(CLUT)の再生成が伴います。

# CLUT-カラー・パレット

11

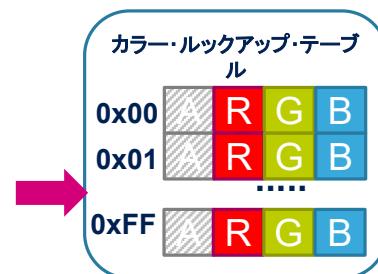

## レイヤあたり最大256エントリのカラー・ルックアップ・テーブル(CLUT)

- フレームバッファには、各ピクセルのインデックス値が含まれる

- CLUTには、R、G、Bの値をプリロードしておく必要がある

- L8およびAL88入力ピクセル・フォーマットの場合、CLUTは256色でプリロード

- AL44入力ピクセル・フォーマットの場合、CLUTには16色をプリロード

各色のアドレスは、4ビットLチャネルを次のように8ビットに複製することによって埋める必要がある

- L0(インデックスカラー0)、アドレス0x00

- L1、アドレス0x11

- L2、アドレス0x22

- ....

- L1、アドレス0xFF

ピクセルあたり

8ビット

L8、AL44、A8

インデックス

インダイレクト

コーディング

カラールックアップテーブルは、入力ピクセル・フォーマットがL8、AL44、およびAL88のインデックスカラーにのみ使用します。

レイヤごとに最大256のエントリをサポートします。

フレームバッファには、各ピクセルのインデックス値が含まれています。

CLUTの各ピクセル(インデックスカラー)には元のR、G、B値を置き換えるR、G、B値を読み込む必要があります。各色(RGB値)には、それ自体のアドレスがあり、CLUT内の位置を表します。

# レイヤのプログラム可能なパラメータ

12

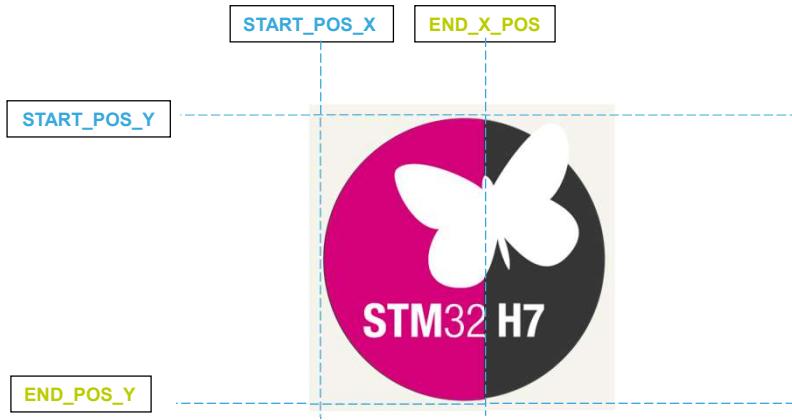

## 柔軟性のあるウィンドウ位置とサイズの設定

すべてのレイヤは配置とサイズを変更できます。

プログラム可能なレイヤの位置とサイズは、ラインの最初と最後の可視ピクセルと

ウィンドウの最初と最後の可視ラインを定義します。画像フレームの全体を表示、または

その一部だけの表示もできます。

## レイヤのプログラム可能なパラメータ

13

### カラーフレームバッファの設定

- フレームバッファ・サイズ、ライン長、およびライン数パラメータを正しく設定する必要がある

- レイヤが必要とするバイトより少ないバイトが設定されている場合、FIFOアンダーランエラーがセットされる

- レイヤが必要とするバイトより多くバイトが設定されている場合、不要な読み取りデータは破棄

不要なデータは表示されない

すべてのレイヤは、カラーフレームバッファとピッチ用の設定可能な

ライン数とライン長を持っています。

ピッチとは、1本のラインの始まりと次のラインの始まりの間の距離

(バイト単位)です。

これらのパラメータはバイトで表されます—ピクセルではありません!つまり、距離の値はピクセルあたりのビット数で決まります。

ライン長とライン数のパラメータは、フレームバッファの最後で

レイヤFIFOへのデータのプリフェッチを停止するのに使用されます。

# レイヤのプログラム可能なパラメータ

14

## マルチレイヤ・ブレンディング

- アルファ値使用のブレンディングが常にアクティブな状態

- ブレンディングの順序はボトムアップに固定

- ボトムレイヤのバックグラウンド・カラーはプログラム可能

LTDCではブレンディング係数を設定できます。ブレンディングの順序はボトムアップに固定されています。2つのレイヤが有効になっている場合、レイヤ1は最初にバックグラウンドカラーとブレンドされ、次にレイヤ2が前回のブレンド結果とブレンドされます。

# レイヤのプログラム可能なパラメータ

15

## デフォルト色の設定

- デフォルト色(ARGB)は定義したレイヤウィンドウの外や、レイヤが無効のときに使用される

- 注意が必要な使用例:

- レイヤ1が有効

- レイヤ2が無効で、デフォルト色は黒

- ブレンディング係数が定数アルファ(0xFF)に設定されている場合、画像は表示されない

黒いウィンドウのみが表示(レイヤ2のデフォルト色は黒です)

- デフォルト色をバイパスするには、ブレンディング係数を透明なアルファ値(0x00)に設定

すべてのレイヤはARGBフォーマットでデフォルト色を設定することができます、デフォルト色は定義したレイヤウィンドウの外またはレイヤが無効のときに使用されます。

注意が必要な使用例:

- レイヤ1が有効

- レイヤ2が無効で、デフォルト色は黒

ブレンディング係数が定数アルファ(0xFF)に設定されている場合、画像は表示されません。黒いウィンドウのみが表示されます(レイヤ2のデフォルト色は黒です)。

デフォルト色をバイパスするには、ブレンディング係数を透明な値であるアルファ=0x00にセットします。

# レイヤのプログラム可能なパラメータ

16

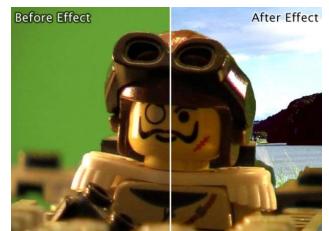

## カラーキーイング

- LTDC\_LxCKCRLレジスタでレイヤごとに透明色(RGB)を定義できる

- カラーキーイングを有効にすると、現在のピクセルがカラーキーと比較される

プログラムされたRGB値と一致した場合、そのピクセルのすべてのチャネル

(ARGB)が0にセットされる

- LTDC\_LxCRLレジスタの各レイヤの

カラーキーイングを動作中に有効化可能

カラーキー(RGB)の設定により、透明なピクセルを表せます。

カラーキーイングを有効にすると、現在のピクセル(フォーマット

変換後、ブレンド前)がカラーキーと比較されます。プログラムさ

れたRGB値と一致した場合、そのピクセルのすべてのチャネル

(ARGB)が0にセットされます。

カラーキー値を設定することにより、ランタイム時にその値を使

用してピクセルRGB値を置換することができます。

カラーキーイングは、LTDC\_LxCKCRLレジスタにより有効にしま

す。

16

| 割込みイベント    | 説明                                               |

|------------|--------------------------------------------------|

| ライン        | ライン割込みは、プログラムされた位置ラインに達したときに生成                   |

| レジスタリロード   | 垂直ブランкиング期間中にシャドウレジスタのリロードが実行されると、レジスタリロード割込みが生成 |

| FIFOアンダーラン | エンプティのレイヤFIFOからピクセルがリクエストされると、FIFOアンダーラン割込みが生成   |

| 転送エラー      | データ転送中にAXIバスエラーが発生すると、転送エラー割込みが生成                |

### ライン割込み:

- プログラムされたライン位置に達すると生成されます。

### レジスタリロード割込み:

- 垂直ブランкиング期間中にシャドウレジスタがリロードされると生成されます。

### FIFOアンダーラン割込み:

- エンプティのレイヤFIFOからピクセルがリクエストされると生成されます。

### 転送エラー割込み:

- データ転送中にAXIバスエラーが発生したときに生成されます。

# 低電力モード

18

| モード     | 説明                                          |

|---------|---------------------------------------------|

| RUN     | アクティブ                                       |

| SLEEP   | アクティブ<br>ペリフェラル割込みによって、デバイスはSLEEPモードを終了     |

| STOP    | 停止<br>ペリフェラル・レジスタの内容は保持                     |

| STANDBY | パワーダウン<br>ペリフェラルは、STANDBYモード終了後に再初期化する必要がある |

LTDCは、RUNモードとSLEEPモードでアクティブです。LTDC割込みにより、デバイスのSLEEPモードを終了させることができます。

デバイスは、STOPモードとSTANDBYモードでは通信できません。

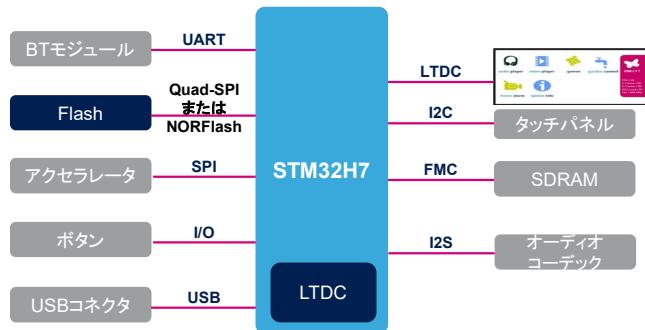

# アプリケーションの例

19

- 接続性とHMIを持つ家電機器

グラフィックアプリケーションには、高品質のユーザインタフェースが必要です。これは、STM32H7を使用しLCD-TFTコントローラでディスプレイに接続することで実現できます。さらに、FMCまたはQuad-SPIインターフェースを使用すれば、バックグラウンドイメージ、高解像度アイコン、複数言語をサポートするフォントなど、必要なすべてのグラフィックコンテンツを収めた外部Flashメモリにアクセスできます。

## 関連ペリフェラル

20

- 詳細については、LTDCに関する次のトレーニングを参照してください。

- リセットおよびクロック制御(RCC)

- 汎用入力／出力(GPIO)

以下は、LTDCモジュールに関するペリフェラルのリストです。

詳細については、必要に応じてこれらのペリフェラルトレーニング

を参照してください。

- リセットおよびクロック制御(RCC)

- 汎用入力／出力(GPIO)