こんにちは、STM32H7x5とSTM32H7x7デュアルコアラインART™(適応型リアルタイム)アクセラレータについてのプレゼンテーションへようこそ。

### 概要

- STM32H7x5およびSTM32H7x7の機能

- Cortex-M4コアのD1ドメイン・メモリへの命令フェッチ アクセスを高速化する256ビットの64キャッシュ・ライン

- 64ビットAXIマスタ・ポートで選択したコードを エンベデッド・キャッシュにロード可能

### アプリケーション側の利点

- Cortex-M4コアにコードを瞬時に使用可能

- メモリ待機状態による遅延を回避

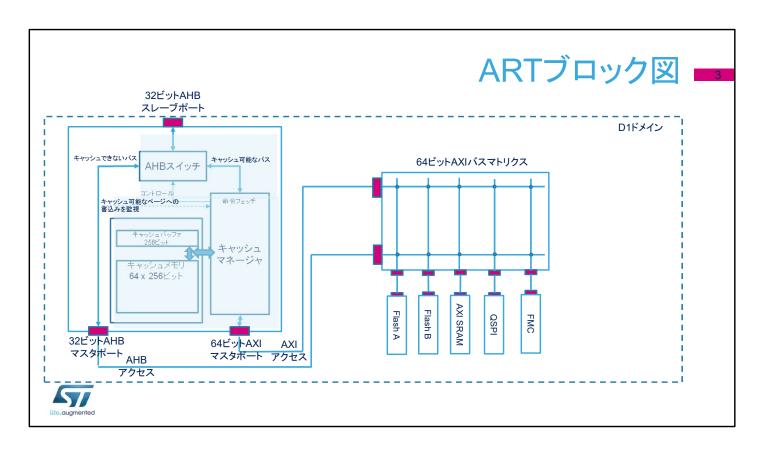

ART™(適応型リアルタイム)アクセラレータブロックは、Cortex-M4コアからD1領域の内部メモリ(Flash Aメモリ、Flash Bメモリ、AXI SRAM)、およびQSPI(Quad-SPI)コントローラとFMC (Flashメモリコントローラ)を介して接続されたD1領域の外部メモリへの命令フェッチアクセスを高速化します。

この高速化は、選択されたコードを組み込みキャッシュにロードし、Cortex-M4コアが即座に利用できるようにすることで実現しており、メモリの待ち時間による遅延を回避しています。

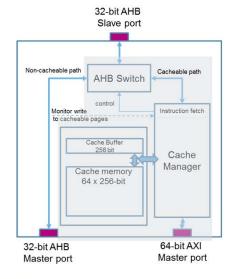

この図は、ARTアクセラレータのブロック回路図と環境を示しています。

命令フェッチアクセスは、キャッシュ可能なものとそうでないものに分けられます。

キャッシュメモリは、256ビットずつの64ラインで構成されています。各ラインには32ビットのセグメントが8つあります。各セグメントには、32ビットの命令コードが1つ、または16ビットの命令コードが2つ含まれます。キャッシュバッファは、256ビットのラインで、キャッシュラインのコピーを保持します。

キャッシュマネージャは、入力されたメモリ命令のフェッチアクセスがキャッシュ可能かどうかをチェックし、それに応じてAHBスイッチを制御します。キャッシュ可能なアクセスの場合、キャッシュヒット時にはキャッシュからの命令フェッチを許可し、キャッシュミス時にはキャッシュメモリラインのリフィル(命令コードのロード)を管理します。非キャッシュ可能なメモリアクセスの場合は、メモリから直接命令をフェッチします。

## 主な機能

- D2ドメインとのインタフェース用の32ビットAHBスレーブ・ポート

- 32ビットAHBマスタ・ポート(キャッシュ不可能なメモリ・アクセス用)

- 64ビットAXIマスタ・ポート (メモリからキャッシュへのコード・ロード用フルアソシアティブ・キャッシュ)

- 最近使用されたものから順に置換するポリシー

- 内容の一貫性をチェックするプログラマブルなキャッシュ可能なページ

#### ART™アクセラレータの機能

- D2ドメインとのインタフェース用に32ビットAHBスレーブポート

- キャッシュ不可能なメモリアクセス用の32ビットAHBマスタポート

- 64ビットAXIマスタポートは、メモリからキャッシュに コードを読み込みます。

- 256ビットの64キャッシュライン

- 完全自動調整キャッシュ

- プログラム可能なキャッシュページ

- キャッシュ内容の整合性チェッカ

# ARTオペレーション

- 命令フェッチ・アクセスは可能(MPU属性に応じて):

- キャッシュ可能

- キャッシュ不可

- 命令フェッチは以下の通り:

- アクセスがキャッシュ可能として設定されている場合のキャッシュ可能アクセス・パス

- キャッシュできないアクセスの場合のマスタAHBポート

- キャッシュは次のように整理される

- 1つのメモリ・ブロック:256ビット×64ライン

- キャッシュ・バッファ:256ビット

- これにより、対応するバッファソースラインがリフィル進行中に、コアによる命令コードのフェッチが可能

命令フェッチアクセスは、MPUの属性に応じてキャッシュ可能 か非キャッシュ可能かを判断します。

キャッシュ可能なアクセスの場合、命令フェッチはキャッシュ可能なアクセスパスに従います。非キャッシュ可能なアクセスは、非キャッシュ可能なアクセスパスに従って、マスタAHBポートに導かれます。適切なアクセスパスは、キャッシュマネージャが制御するAHBスイッチによって選択されます。

キャッシュメモリは、256ビット×64ラインで構成されています。 各ラインには32ビットのセグメントが8つあります。各セグメント には、32ビットの命令コードが1つ、または16ビットの命令コー ドが2つ含まれます。キャッシュバッファは、キャッシュラインの コピーを保持する256ビットの追加ラインです(バッファソースラ イン)。これにより、対応するバッファソースラインのリフィルが 進行している間に、コアが命令コードをフェッチすることができ ます。

## ARTオペレーション

- キャッシュの一貫性を確保するために、以下のような操作が検出された場合、 すべてのキャッシュラインが無効になる:

- 書込みアクセスが、キャッシュ可能なページのデータの一部を変更

- ソフトウェアがARTアクセラレータのコントロール・レジスタ内のキャッシュ可能なページ・インデックスを変更した場合

- キャッシュ・バッファおよび/またはキャッシュ・メモリ・ラインのリフィル中にデータ転送エラーが発生

以下のような場合、キャッシュ内のコードと、アドレス指定されたメモリの対応するアドレスのコードが一致しなくなることがあります。

- 書込みアクセスは、アドレス指定されたメモリのキャッシュ 可能なページのデータを変更するものである。

- ソフトウェアは、ARTアクセラレータのコントロールレジスタ のキャッシュ可能なページインデックスを変更する。

- キャッシュバッファやキャッシュメモリラインのリフィル時にデータ転送エラーが発生する。

デバイスには、キャッシュの不整合によるソフトウェアの破損を防止するメカニズムが組み込まれています。上記のケースを検出し、すべてのキャッシュメモリ行とキャッシュバッファに無効なフラグを設定します。その結果、次のキャッシュ可能なアクセスはキャッシュミスを引き起こし、キャッシュラインは新しいデータを再入力します。