こんにちは。STM32H7x3/x5/x7マイクロコントローラ用のリセット およびクロック制御(RCC)のプレゼンテーションをご覧いただき ありがとうございます。RCCは、パワーコントローラブロック (PWR)にリンクされています。このスライドセットをご覧になる前 に、PWRブロックに関するスライドをご覧ください。

### 概要

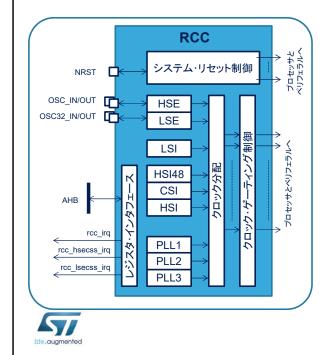

- STM32H7x3/x5/x7リセットおよびクロック制御 (RCC)の管理対象

- 全クロックの生成

- PLL、RC発振回路、クリスタル・オシレータなど

- 全クロックのゲーティング

- すべてのシステムとペリフェラルのリセットの制御

### アプリケーション側の利点

- 消費電力と精度の要件を満たすための クロックソース選択の高い柔軟性

- 安全で柔軟なリセット管理

STM32H7x3/x5/x7リセットおよびクロック制御は、各種のリセット メカニズムならびにシステムおよびペリフェラルのクロックの生成 を管理します。

STM32H7x3/x5/x7デバイスには、内部発振回路が4個、外部クリスタルまたはレゾネータ用の発振回路が2個、フェーズロックループ(PLL)が3個搭載されています。

多くのペリフェラルには、システムクロックから独立した個々のカーネルクロックが備わっています。

STM32H7x3/x5/x7のRCCによって、クロックソース選択に高い柔軟性がもたらされ、それによってシステム設計者は、消費電力と精度の両方の要件を満たすことが可能となります。

独立したペリフェラルクロックが数多くあるため、設計者は、通信ボーレートに影響を与えることなくシステム消費電力を調整し、さらに、低電力モードで特定のペリフェラルをアクティブに保つことが可能です。

# リセットの主な機能

### 外部コンポーネント不要で安全かつ柔軟なリセット管理

- RCCはいくつかのタイプのリセットを生成

- パワーオン・リセット(rst por)

- システム・リセット(nreset)

- バックアップ・ドメイン・リセット(rst vsw)

- ドメイン・リセット(rst d1、rst d2)

外部コンポーネント不要な安全かつ柔軟なリセット管理により、ア プリケーションのコストを削減できます。

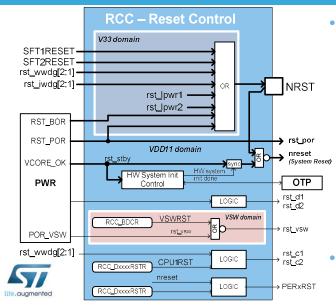

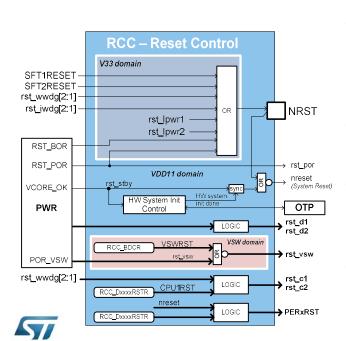

RCCは、電源リセット、システムリセット、D1とD2ドメインリセット、 ローカルリセット、バックアップドメインリセットといったさまざまな タイプのリセットを管理します。

### リセット・ソース

### 内部フィルタと電源モニタリングにより外部コンポーネントが不要 システム・リセット・ソースが外部コンポーネントをリセット可能

- システム・リセット・ソース:

- パワーオン・リセット(rst por)

- ブラウンアウト・リセット

- NRSTピンのローレベル(外部リセット)

- WWDG[2:1]タイムアウト・イベント

- IWDG[2:1]タイムアウト・イベント

- ソフトウェア・リセット(SFT[2:1]RESET)

- 低電力モード・セキュリティ・リセット(rst lpwr[2:1])

- STANDBYの終了

- パワーオン・リセット・ソース(rst por)

- VDDとVDD11の電圧コンパレータ

PWRブロックに含まれる電圧モニタリング機能、NRSTパッドに組み込まれたフィルタ、およ びRCCリセット制御により、外付け部品はNRST端子に接続された1つの外付けコンデンサ に削減されています。

1つ目のリセットはシステムリセットで、リセット&クロックコントローラとパワーコントローラの 一部のレジスタを除くすべてのレジスタをリセットします。また、バックアップドメインはリセッ トされません。

多くのソースでシステムリセットが発生します。

- VDDまたはVCOREの電源電圧が無効(詳細はPWRブロック参照)

- ブラウンアウト機能によるVDDの無効電圧。ブラウンアウト機能では、VDD電源のしき い値をユーザーが自由に選択することができます(詳細はPWRブロックを参照)

- STANDBYモードからの解除

- NRSTパッドのローレベル

- 独立ウォッチドッグの1つからのタイムアウト(IWDG[2:1])

- リセットスコープビットで許可されている場合は、ウィンドウ・ウォッチドッグの1つからの タイムアウト(WW[2:1]RSC)

- Cortex-M7(名称: CPU1)またはCortex-M4(名称: CPU2)からのソフトウェアリセット要 求

- 低電力モードのセキュリティリセット(STOPまたはSTANDBYモードに入ったときに発生 するが、オプションバイトの設定により禁止されている)

また、システムリセットではNRSTパッドがアサートされるので、これを使ってボード上の外部 コンポーネントをリセットすることができます。リセットソースフラグは、RCCコントロール&ス テータスレジスタにあります。

V<sub>DD</sub>またはV<sub>CORE</sub>の電圧が特定の電圧しきい値よりも低い場合、パワーオンリセットが生成さ れます。

4

### リセット・ソース \_\_\_

- バックアップ・ドメイン・リセット・ソース

- RCC BDCRレジスタのBDRSTビット設定

- 両方の電源がオフになっているときに、 $V_{DD}$ または $V_{BAT}$ の電源がオンとなる

- ドメイン・リセット・ソース

- DSTANDBYモードからの解除

- ペリフェラル・リセット・ソース

- RCCレジスタのPERxRSTビット

- ・システム・リセット

- RCCは、リセット元を識別するために フラグを提供

バックアップドメインのリセットが発生するのは下記の通りです。

- 図に示すように、RCC\_BDCRレジスタのBDRSTビットがアプリケーションによって'1'に設定されるとき。

- 両方の電源がオフになっている場合に、V<sub>DD</sub>とV<sub>BAT</sub>の電源が 入るとき。

D1またはD2ドメインのリセットは、2つのドメインのいずれかがオフになると発生します。

また、ペリフェラルには個別のリセット制御ビットが用意されています。

また、CPU1とそれに付随するウィンドウ・ウォッチドッグ WWDG1(rst\_c1)をリセットしたり、CPU2とそれに付随するウィンドウ・ウォッチドッグWWDG2(rst\_c2)をリセットしたりすることも可能です。

- パワーオン・リセットによって、VDDドメインとVCOREドメインにあるすべてのロジックがリセットされ、バックアップ・ドメインのロジックは、影響を受けない

- システム・リセットによって、特定のRCCレジスタ、PWRレジスタ、バックアップ・ドメインを除くすべてのレジスタがリセットされる

- **バックアップ・ドメイン・リセット**によって、バックアップ・ドメインRTCレジスタ、バックアップ・レジスタ、RCC\_BDCRレジスタがリセットされる

- ドメイン・リセットは、ドメインのV<sub>CORE</sub>供給ライン(D1またはD2)上のすべてのロジックをリセットする

パワーオン・リセットは、カバー範囲が最大のリセットです。 RTCと外部低速発振回路が含まれているVBATから電源を供給されているバックアップドメインのロジックを除いて、パワーオン・リセットによって、VDDドメインとVCOREドメインにあるすべてのロジックがリセットされます。

パワーオン・リセットによりシステムリセットもトリガされますので、 パワーオン・リセット中にはNRSTパッドがアサートされることに注 意してください。

システムリセットによって、RCCブロックとPWRブロックの中にあるいくつかのリソースを除いて、V<sub>DD</sub>とV<sub>CORE</sub>ドメインにある大半のロジックがリセットされます。バックアップドメインは、このリセットの影響を受けません。

バックアップドメインリセットによって、RTCと外部低速発振回路が含まれているVBATから電源を供給されているバックアップドメインがリセットされます。

ドメインリセットは、対応する電源スイッチが作動したときに、D1およびD2ドメイン全体をリセットします。

#### どのプロセッサが最初に起動するかを選択することが可能!

- HOLD BOOT機能は、システム・リセット後やシステムがSTANDBYモードを 終了したときに、2つのCPUのうち1つを保留にすることが可能

- Hold Boot機能は、1つのCPUがシステムのマスタとなり、2つ目のCPUを 起動する前に製品全体の初期化(システム・クロック、電圧スケーリングなど)を 完了させる構成をサポートするために提供される

ホールド・ブート機能を使用すると、システム・リセット後、または スタンバイ・モードからの終了後に、2つのプロセッサーの1つを HOLDに設定できます。

この関数は、システム初期化を実行する場合など、1つのプロ セッサが事前にBOOTを実行する必要がある場合に役立ちます。 いずれかのプロセッサーがHOLD状態の場合、システムがスタン バイ・モードに入ることを妨げることはできません。

### 低電力、精度、性能に対するクロックソースの選択

- 4つの内部クロックソース

- 高速内部64MHz RC発振回路(HSI)

- 高精度内部48MHz RC発振回路(HSI48)

- 低電力内部4MHz RC発振回路(CSI)

- 低速内部32kHz RC発振回路(LSI)

- 2つの外部発振回路

- クロック・セキュリティ・システム付き高速外部4MHz~48MHz発振回路(HSE)

- クロック・セキュリティ・システム付き低速外部32.768kHz発振回路(LSE)

- それぞれ3本の独立出力を備えた3つのPLL

RCCによってクロックソースの選択対象が拡大し、低電力、精度、性能に対する要件に基づいて選択が可能です。

STM32H7x3/x5/x7デバイスには、以下に示す4つの内部RC発振回路が組み込まれています。

- 64、32、16、8MHz動作が可能な高速内部RC発振回路(HSI)

- 4MHzで動作する低電力内部RC発振回路(CSI)

- 48MHzで動作する高精度RC発振回路

- 低速内部32kHz RC発振回路(LSI)

STM32H7x3/x5/x7デバイスには、外部のクリスタルまたはレゾネータとと もに使用する発振回路が2個搭載されています。

- クロックセキュリティシステム付き高速外部4~48MHz発振回路(HSE)

- クロックセキュリティシステム付き低速外部32.768kHz発振回路(LSE)

STM32H7x3/x5/x7デバイスには、フェーズロックループも3個搭載されており、さまざまな周波数で各種ペリフェラルにクロックを供給するための独立出力が3本ずつ備わっています。

# 高速内部発振回路(HSI)

### 1%精度、高速、高速復帰時間

- HSI64MHz、工場出荷時調整済み、ユーザ調整可能

- HSIを選択可能な用途

- STOPモードからのウェイクアップ・クロック

- クロック・セキュリティ・システム(CSS)用バックアップ・クロック

- STOPモード終了時に自動的に起動可能

- 起動時間低減のため、STOPモード中は有効のまま 維持することが可能

- 一部のペリフェラルでは、ウェイクアップ・イベントの 状態を検出するためにカーネル・クロックが必要な ときに、STOPモード中にHSIを有効に出来る

| パラメータ    | 値         |

|----------|-----------|

| 起動時間     | 2μs(最大)   |

| 消費電流(標準) | 300µA(標準) |

高速内部発振回路(HIS)は、高速ウェイクアップ時間を提供する 64MHz RC発振回路です。HSIは、製造テスト中にトリミングされ ていますが、ユーザーによるトリミングも可能です。

専用の分周は32、16または8MHzのクロックを生成することができ ます。

HSIは、システムSTOPからの復帰時のクロックとしても、クロック セキュリティシステムによってHSEの障害が検出された場合の バックアップクロックとしても選択可能です。

HSIは、復帰時間を高速化するために、システムがSTOPモード になった場合にも電源はオンのままとすることが可能です。

I2CやU(S)ART/LPUARTなどの特定のペリフェラルは、ウェイク アップイベントを生成するためにシステムSTOPモードでHSIのア クティベーションを要求できます。

HSIは、ウェイクアップシーケンスの検出時にのみペリフェラルに よって有効となり、このウェイクアップシーケンス以外では無効の ままとなります。

#### 低電力、高速復帰時間

- CSI4MHz、工場出荷時調整済み、ユーザ調整可能

- CSIはSTOPモードからウェイクアップ・クロックとして 選択することが可能

- STOPモードを終了すると自動的に起動可能

- 起動時間低減のため、STOPモード中は有効のまま 維持することが可能

- 一部のペリフェラルでは、ウェイクアップ・イベントの 状態を検出するためにカーネル・クロックが必要な ときに、STOPモード中にCSIを有効に出来る

| パラメータ    | 値        |

|----------|----------|

| 起動時間     | 1μs(標準)  |

| 消費電流(標準) | 23µA(標準) |

低電力内部発振回路(CSI)は、4MHzの発振回路で、高速起動 時間を実現しています。CSIは、製造テスト時に調整されますが、 ユーザによる調整も可能です。

CSIは、システムSTOPからの復帰時のクロックとして選択できま す。

CSIは、システムがSTOPモードになっても、電源を入れたままに しておくことで、復帰時間が早くなります。

I2CやU(S)ART/LPUARTなどの特定のペリフェラルは、システム STOPモード時にCSIの起動を要求して、ウェイクアップイベントを 発生させることができます。

CSIは、ウェイクアップ・シーケンスの検出時のみペリフェラルに よって有効となり、このウェイクアップ・シーケンス以外では無効と なります。

# 高速外部発振回路(HSE)

#### 安全なクリスタル・システム・クロック

| • | HS | <b>L</b> 4 | ~ | 48 | VI | HZ |

|---|----|------------|---|----|----|----|

|   |    |            |   |    |    |    |

- 外部ソース(バイパスモード) 最大50MHz

- 外部クリスタル/レゾネータ (4~48MHz)

- クロック・セキュリティ・システム(CSS)

- HSE障害の自動検出

- ノンマスカブル割込みの生成

- TIM1/TIM8/TIM15/TIM16/TIM17に対するブレーク入力 =>モータ制御などの重要なアプリケーションを安全な状態にすることが可能

- バックアップ・クロックはHIS

- =>クリスタルの障害の場合もアプリケーション・ソフトウェアは 停止しない

- パラメータ 値 起動時間 2ms(標準) 消費電力\*(標準) 0.45mA(標準)

- VDD=3V、Rm=30Ω、CL=10pF:16MHz時

高速外部発振回路(HSE)により、安全なクリスタルシステムク ロックが得られます。

HSEは4~48MHzの外部クリスタルまたはレゾネータ、バイパス モードの外部ソースをサポートします。

クロックセキュリティシステムは、HSEの故障を自動的に検出しま す。検出されるとノンマスカブル割込みが発生し、タイマにブレー ク入力を送ることで、モータ制御などの重要なアプリケーションを 安全な状態にすることができます。HSE故障を検出すると、シス テムクロックは自動的にHSIに切り替わり、水晶振動子が故障し てもアプリケーションソフトが停止しないようになっています。

### 超低消費電力の内部32kHzオシレータ VBATモードを除くすべてのモードで使用可能

• LSIは、RTC、LPUART、LPCM、およびIWDGに使用可能

|          | LSI 32kHz |

|----------|-----------|

| 精度(標準)   | +/-1.8%   |

| 消費電流(標準) | 130nA     |

STM32H7x3/x5/x7デバイスは、超低消費電力32kHz RC発振回 路(LSI)を内蔵しており、VBATモードを除くすべてのモードで使 用可能です。

LSIは、RTC、LPUART、低消費電力タイマ、および独立型ウォッ チドッグのクロックに使用することができます。LSIの精度は ±1.8%です。LSIの消費電力は標準で130nAです。

### 低電力と高駆動能力に設定可能な32.768kHz すべての電源モードとVBATモードで使用可能

- LSEは、外付けオシレータもしくはレゾネータ、またはバイパス・モードの 外部クロック・ソースで使用可能

- LSEのクロック・セキュリティ・システム: VBATを除くすべてのモードで使用可能

- LSEは、RTC、U(S)ART、LPUART、LPTMに使用可能

| モード     | 最大限界ゲイン<br>gm(µA/V) | 消費電流(nA) |

|---------|---------------------|----------|

| 超低電力    | 0.5                 | 290      |

| 中~低駆動能力 | 0.75                | 390      |

| 中~高駆動能力 | 1.7                 | 550      |

| 高駆動能力   | 2.7                 | 900      |

32.768kHz低速外部発振回路(LSE)は、外付けクリスタルもしくは レゾネータ、またはバイパスモードの外部クロックソースで使用可 能です。発振回路の駆動能力はプログラム可能です。消費電流 がわずか290nAの超低電力モードから高駆動能力モードまで4 モードが使用可能です。

クロックセキュリティシステムは、LSE発振回路の障害をモニタし ています。障害が生じた場合には、アプリケーションは、RTCク ロックから選択されたLSIクロックに切換え可能です。

クロックセキュリティシステムは、VBATを除くすべてのモードで機 能します。リセット中も機能します。

LSEは、RTC、USARTまたは低電力UARTペリフェラル、および低 電力タイマのクロックに使用できます。

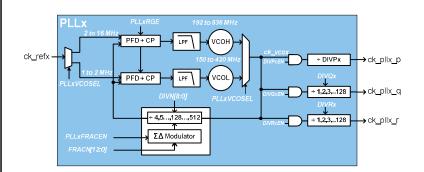

#### 広い入力範囲、高精度の出力周波数

#### • 3つのPLL:

- 広い入力周波数範囲

- VCOLを使用した1~2MHz

- VCOHを使用した2~16MHz

- 広いVCO出力周波数範囲

- VCOLを使用した150~420MHz

- VCOHを使用した192~836MHz

- 13ビット分数乗算係数

- プログラム可能なオンザフライ

- PLLごとの3つの出力

- 1~128の後段分周回路付き

STM32H7x3/x5/x7デバイスに内蔵されたPLLは、システムクロックやペリフェラルクロックに必要な周波数を柔軟に生成することができます。 1~16MHzの幅広い入力周波数範囲を提供します。

入力周波数が1~2MHzの場合、ユーザはVCOLパスを選択する必要があります。

入力周波数が2~16MHzの場合、ユーザはVCOHパスを選択する必要があります。

2つのVCOには、VCOLの場合は150~420MHz、VCOHの場合は192~836MHzというスマートな周波数範囲もあります。

またPLLは、すべて後段分周器(DIVP、DIVQ、DIVR)を介してVCO出力から派生した3つの異なる出力を提供します。

さらに、PLLを無効にすることなく、後段分周器の値を変更することもできます。アプリケーションは、対応する後段分周器を無効にし、除算比を変更し、 後段分周器を再度有効にする必要があります。

50%に近いデューティサイクルを取得するために、アプリケーションは偶数の値に後段分周器をプログラムする必要があります。

また、VCO周波数で高精度にするため、分数モードに切り替えることができます。

13ビットの分数分割は、PLLを無効にしなくても変更できます。この機能は正確なクロックドリフト補正を実行するために使用することができます。

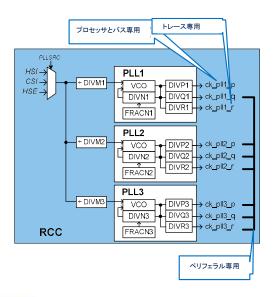

# 簡素化されたクロック分布

#### PLLで生成されるクロック

- 可能なクロック・ソース: HSE、HSI、CSI

- 各PLLをオフからオンにする専用の前段分周器

- ペリフェラル・カーネル・クロックの生成に特化した 7つの出力

- ・ プロセッサやバス専用の出力が1つ

- デバッグ・トレース用の出力が1つ

PLLは同じクロックソースを共有しています。: HSI、CSI、HSEのい ずれかです。

各PLLの基準クロックを調整するために、各PLLには専用の前段 分周器が設けられています。

PLL2とPLL3は、ペリフェラル用のカーネルクロックの生成に特化 しています。SAIやUSBなどの特定のペリフェラルは、特定の周波 数を必要とする場合があります。

PLL1 P出力はプロセッサやバスのシステム・クロックとして、 PLL1 Rはデバッグ・トレース専用として、PLL1 Qはペリフェラルの カーネル・クロックとしても使用されます。

なお、いずれかのPLLがイネーブルになっている場合は、PLLの クロックソースを変更することはできません。

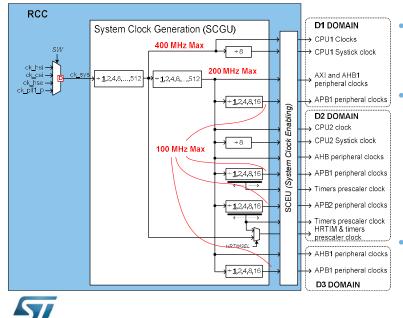

### 簡素化されたクロック・ツリー

- システム・クロック選択のための ダイナミック・スイッチ

- システム・クロック・ソースは

- HSI(リセット後のデフォルト)

- CSI

- HSE

- PLL1\_P出力

- ダイナミックな分周器により周波数 調整が容易

システムクロックは、HSI、CSI、HSE、またはPLL1のDIVP出力から得ることができます。

システムクロックを選択するためのスイッチは動的なもので、タイミング違反を起こさずに、その場で周波数を変更することが可能です。

また、図で紹介したプリスケーラはすべてダイナミック型なので、 オンザフライで変更することも可能で、周波数スケーリングの操 作が非常に簡単です。

CPU1のクロックは480MHzを超えません。

AHBクロックは、CPU2の速度と同様に240MHzを超えません。

APBクロックは120MHzを超えません

HRTIMと特定のタイマは、最大480MHzのクロック周波数を使用できます。

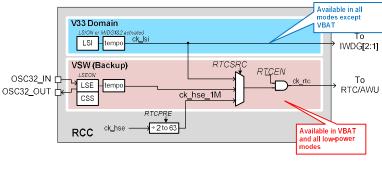

# 簡素化されたクロック・ツリー

RTC/AWUのクロック・ソースは

5/

・ LSE To RTC/AWU ・ HSE分周器

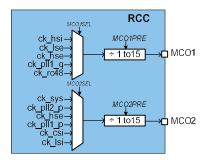

> 2つのクロック出力: MCO1とMCO2の2つのクロック出力により、クロック・ソースの選択肢が広がる

RTC/AWUのクロックは、LSE、LSI、HSE分周の中から選択できます。なお、HSE分周をRTC/AWUのカーネルクロックとして使用する場合、その周波数は1MHzを超えることはできません。

また、LSIをRTC/AWUのカーネルクロックとして使用している場合、 V<sub>DD</sub>とV<sub>CORE</sub>の供給を停止するとRTC/AWUはクロックを供給され なくなりますのでご注意ください。

RTC/AWUのカーネルクロックとしてHSE分周を使用している場合、 システムがSTOPモードになったり、V<sub>CORE</sub>の供給が停止したりす ると、RTC/AWUにクロックが供給されなくなります。

LSEは、すべての低電力モードとVBATモードで有効にしたままにできます。

RCCは、MCO1とMCO2の2つのクロック出力信号も提供します。 プリスケーラにより、アプリケーションは周波数をパッドの能力に 合わせることができます。

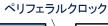

### ペリフェラルに影響を与えずにバス・スピードを変更可能

- ペリフェラルは、一般的に

- 1つまたは複数のバス・クロック

- 1つまたは複数のカーネル・クロック

- このバス・クロックにより、ペリフェラルの制御や データ・ストリームへのアクセスが可能

- カーネル・クロックは、一般的にペリフェラルが その外部インタフェースを処理するために 使用される:

I2S, SPI, USB, Ethernet...

多くのSTM32H7x3/x5/x7ペリフェラルは、プロセッサ・バス・インタフェース を介したデータ・ストリームとコントロール・ストリームのクロック、および特 定のペリフェラル・インタフェースのクロックが異なります。

一般的に、プロセッサ・バス・インタフェースを介したデータおよび制御スト リーム用のクロックは「バス・クロック」と呼ばれ、ペリフェラル専用インタ フェース用のクロックは「カーネル・クロック」と呼ばれます。

ペリフェラルクロックは、ペリフェラルが受信するクロックを表すもので、「バ スクロック」と「カーネルクロック」があります。

バスクロックとカーネルクロックを分離することで、アプリケーションはペリ フェラルに影響を与えることなく相互接続とプロセッサの動作周波数を変 更することができます。

特定のペリフェラルでは、ペリフェラルがシステムにデータを転送する必要 がない限り、バスクロックを無効にすることも可能です。

そのため、バス・プロセッサおよびメモリの周波数選択や、ペリフェラル・イ ンタフェースの実際のニーズに柔軟に対応することができます。

例えば、UARTには、シリアルインタフェース通信のボーレートジェネレータ などで使用されるカーネルクロックと、レジスタインタフェース用のAPBク ロックがあります。

また、特定のペリフェラルは、特定のイベントを検出するとカーネルクロック を要求することができます。

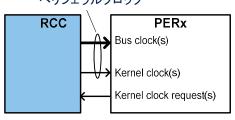

#### カーネル・クロックの切り替えは動的でグリッチ・フリー

- カーネル・クロックを受信するペリフェラルの多くは、 最適なカーネル・クロックを選択するためのクロック スイッチを備える

- クロック・スイッチは、動的でグリッチ・フリー

- ペリフェラルの要求に応じて、いくつかのクロック・ソースが 提案される

- カーネル・クロックの切り替えは、RCCレジスタで設定可能

このプレゼンテーションでは、カーネルクロックの配布については 詳しく説明していません。具体的な内容については、リファレンス マニュアルをご参照ください。

カーネルクロックを受信するペリフェラルの多くは、最適なクロック ソースを選択するための動的なクロックスイッチを備えています。 提案されているクロックソースは、一般的に以下を受信します。

- カーネルクロック生成用の7つのPLL出力のうちの1つ

- 内部または外部オシレータ:システムがSTOPモードの時にカー ネルクロックを必要とするペリフェラルには必須です。

- パッド:外部PHYを使用するペリフェラルなどに使用されますが、 オーディオでも外部デバイスからのクロックリファレンスを使用す るために使用されます

- ・その他の内部ペリフェラル:ブロック間の同期のため。

動的な切り替えにより、あるソースから別のソースへの移行が容 易になります。

RCCレジスタは、すべてのペリフェラルのカーネルクロックの設定 に使用されます。

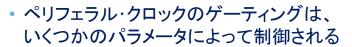

# ペリフェラル・クロック・ゲーティング 20

- イネーブル・ビット(C1\_PERxEN、C2\_PERxEN)

- 低電カイネーブル・ビット(C1\_PERxLPEN、 C2\_PERxLPEN)

- プロセッサとドメインの状態

- 自律ビット(D3 PERxAMEN)

- ビットC1\_PERxENを'1'にすると、CPU1に 対してペリフェラルPERxが有効であることを示す

- ビットC2\_PERxENを'1'にすると、CPU2の ペリフェラルPERxが有効であることを示す

- この操作をペリフェラルの「割当て」と呼ぶ

ペリフェラルは、一般的に以下を受信します。

- 1つまたは複数のバスクロック

- 1つまたは複数のカーネルクロック

各プロセッサは、RCC内の専用レジスタを介して、ペリフェラルクロックのクロックゲーティングを制御することができます。

ペリフェラルクロックのゲーティングは、いくつかのパラメータに依存します。

- クロック・イネーブル・ビットは、各プロセッサに専用のコントロール・ ビットが用意されており、簡略化してC1\_PERxENとC2\_PERxENと名付けられています。

- 低電力クロックイネーブルビット

- プロセッサの状態(CRUN、CSLEEP、CSTOP)

- D3ドメインに配置されたペリフェラルの自律ビット

ビットC1\_PERxENを '1' にすると、CPU1に対してペリフェラルPERxが有効であることを示します。

ビットC2\_PERxENを '1' にすると、CPU2のペリフェラルPERxが有効であることを示します。

この操作をペリフェラルの「割り当て」と呼びます。

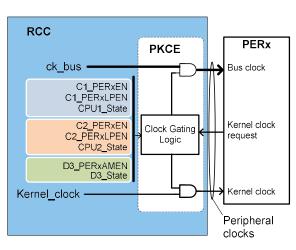

###

- 割当ては、CPU1またはCPU2がペリフェラルを有効に したことをRCCに通知 この情報は、低消費電力モードで使用

- ペリフェラルを使用する前に、CPUはそのペリフェラルを 割り当てる必要がある(つまり、有効にしなければいけない)

- FLASH、AXISRAM、ITCM、DTCM1、DTCM2は、CPU1に 暗黙のうちに割り当てられる(つまり、有効になっている)

- D2SRAM1, D2SRAM2, D2SRAM3は、CPU2に 暗黙のうちに割り当てられる(つまり、有効になっている)

- IWDG1、IWDG2、RCC、PWR、EXTI、D3SRAM4は、 両方のCPUに暗黙的に割り当てられている (つまり、有効になっている)

ここで重要なのは、RCCには2つのレジスタセットがあり、各プロセッサがペリフェラルを有効化 (または割り当て)できることです。

ペリフェラルの割り当ては、CPU1またはCPU2がペリフェラルを有効にしたことをRCCに知らせ ます。この情報は、RCCが低電力モードのクロック制御に使用します。

そのため、ペリフェラルを使用する前には、CPUがペリフェラルを割り当てなければなりません。

同じペリフェラルを両方のプロセッサに割り当てることができてしまうので、その際はアプリケー ション上でリソースの競合を考慮してください。

特定のペリフェラルは、暗黙のうちに特定のプロセッサに割り当てられます。

- FLASH、AXISRAM、ITCM、DTCM1、DTCM2は、CPU1に暗黙のうちに割り当てられており (=有効)、CPU2はそれらのいずれかを割り当てることができますが、デフォルトでは CPU2には割り当てられていません。

- D2SRAM1、D2SRAM2、D2SRAM3は、暗黙のうちにCPU2に割り当てられ(=有効化され)、 CPU1はそのうちのどれかを割り当てることができますが、デフォルトではCPU1には割り 当てられません。

他の一部のペリフェラルは、両方のプロセッサに割り当てられています。これは、IWDG1、 IWDG2、RCC、PWR、EXTI、D3SRAM4などが該当します。

CPUがペリフェラルを割り当てると、このペリフェラルは低消費電力モードのプロセッサの状態 に「リンク」されます。

RCCでは、CPUと、このCPUに割り当てられたペリフェラル、および関連する相互接続を、CPU サブシステムとみなしています。

D1とD2のドメインコア電圧はスイッチオフ可能です。

RCCがペリフェラルの割り当てをどのように使用するかの簡単な例を挙げると、あるドメインの ペリフェラルの1つが、スイッチオフされていない他のドメインのプロセッサで使用されている場 合、RCCはそのドメインのスイッチオフを許可しません。

| システムの状<br>態 | D1ステータス             | D2ステータス             | D3ステータス  |

|-------------|---------------------|---------------------|----------|

| RUN         | DRUN/DSTOP/DSTANDBY | DRUN/DSTOP/DSTANDBY | DRUN     |

| STOP        | DSTOP/DSTANDBY      | DSTOP/DSTANDBY      | DSTOP    |

| STANDBY     | DSTANDBY            | DSTANDBY            | DSTANDBY |

- ドメインは、そのバスマトリックスがクロックされると、DRUNになる CRUN/CSLEEP状態のCPUがこのドメインのペリフェラルを割り当てた場合、 そのバスマトリクスはクロック供給される

- ドメインは、そのバスマトリックスがクロック供給されなくなると、DSTOPになる このドメインのCPUがCSTOPになっている際、他のCPUがこのドメインに ペリフェラルを割り当てていないか、あるいはこのCPUもCSTOPになっている

• ドメインは、そのV<sub>CORF</sub>供給がスイッチオフされると、DSTANDBYになる

次の表は、システムの状態とドメインの状態を簡略化して表したものです。

- ドメインは、そのバスマトリクスがクロックされると、DRUN モードになります。CRUN/CSLEEPモードのCPUがこのドメインのペリフェラルを割り当てた場合、そのバスマトリクスはクロック供給されます。

- あるドメインは、そのバスマトリックスがクロックされなくなると、 DSTOPモードになります。もしこのドメインのCPUがCSTOP モードになっているなら、他のCPUがこのドメインにペリフェラ ルを割り当てていないか、あるいはこのCPUもCSTOPモード になっています。

- ドメインは、そのV<sub>CORE</sub>供給がスイッチオフされると、 DSTANDBYモードになります。

なお、D3ドメインだけをDRUNモードにして、他のドメインを DSTANDBYモードにすることも可能です。

システムステートの詳細については、PWRトレーニングスライドを ご参照ください。

- システムの再起動

- HSIをシステムおよびペリフェラル・クロックとして選択

- すべてのPLLをオフにする

- システムSTOP再起動

- アプリケーションは、システム・クロックとしてHSIまたはCSIを選択することが可能

- ペリフェラル・クロックとして、HSIまたはCSIを選択することが可能

- DSTOPもしくはCSTOP再起動

- DSTOP/STOPに移行する前のクロック設定が保持される

なお、システムリセット後などの再起動時には、システムおよびペ リフェラルクロックとしてHSIが選択されます。

CSI、HSI48、HSEはオフで、PLLもオフです。

LSIはまだ動作しています(以前に有効だった場合)。

システム停止後、PLLはオフになります。アプリケーションは、シ ステムクロックおよびペリフェラルクロックとして、HSIまたはCSIの いずれかを選択できます。

HSI48とHSEはオフになっています。

D1またはD2ドメインがDSTOPまたはCSTOPモードを終了した後. RCCは低電力モードに移行する前と同じクロック設定を維持しま す。

CSLEEPモードは、クロック設定には影響を与えず、クロックゲー ティングにのみ作用します。

#### D3ドメインのペリフェラルが自律的に動作可能

- 自律モードでは、D1ドメインとD2ドメインの両方がDSTOPまたはDSTANDBY モードであっても、D3ドメインに配置されたペリフェラルはペリフェラル・クロックを 受信することが可能

- 自律モードでのペリフェラルのクロックのゲーティングは、D3ドメインのモードに依存

- なお、D3ドメインは、ペリフェラルの活動状況に応じて、DRUNモードからDSTOP モード、またはDSTOPモードからDRUNモードに独自に切り替えることが出来る

自律モードでは、D3に配置されたペリフェラルに対しても、ペリフェラルクロックを供給することが可能です。

- 割り当てられたCPUがCSTOPモードの場合。

- D1とD2の両方のドメインがDSTOPまたはDSTANDBYモードの場合。

自律モードでのペリフェラルのクロックのゲーティングは、D3ドメインのモードに依存します。

- D3ドメインがDRUNモードの場合、ペリフェラルはそのペリフェラルクロックを受信

- D3ドメインがDSTOPモードの場合、ペリフェラル・クロックはゲートされますが、ペリフェラルがカーネル・クロックを要求する機能を持っていれば、ペリフェラルはカーネル・クロックを要求できます。

自律モードは、D3ドメインがDSTOPまたはDSTANDBYモードに入ることを妨げるものではありません。

D3ドメインは、ペリフェラルのアクティビティに応じて、DRUNモードからDSTOPモード、さらにDSTOPモードからDRUNモードへと交互に切り替えることができます。

例えば、システムがI2C4経由でメッセージを受信している場合、システム全体をSTOPモードにすることができます。

I2C4がSTARTビットを検出すると、「カーネルクロックリクエスト」を生成します。

このリクエストにより、HSIまたはCSIが有効になり、要求者にのみカーネルクロックが提供されます。そして、 I2C4は受信したメッセージをデコードします。

いくつかのケースが考えられます。

- 受信メッセージのデバイスアドレスが一致しない場合、I2C4は新たなSTART条件が検出されるまで、「カーネルクロック要求」を解除します。

- 入力されたメッセージのデバイス・アドレスが一致した場合、そのメッセージはD3のローカル・メモリに 保存されなければなりません。I2C4は、D3ドメインをDRUNモードに切り替えるために、アドレス一致時 にウェイクアップイベントを生成することができます。D3ドメインがDRUNモードになると、バス・インタ フェース・クロックが起動し、I2C4がDMA1を介してメッセージをメモリに転送できるようになります。

- D3のローカルメモリが満杯になっていなければ、D3ドメインは、CPUの起動なしにDSTOPモードに戻る。

- D3のローカルメモリが一杯になった場合、DMA1はCPU1またはCPU2を起動するためにウェイクアップイベントを生成することができます。

詳細はD3ドメイン低電カスライドセットをご参照ください。

### カーネル・クロック要求 25

- UARTやI2Cなどの一部のペリフェラルは、処理のためにカーネル・クロックを 要求するイベントを非同期的に検出することが可能

- RCCは、ペリフェラルを割り当てているCPUがCSTOPにある場合や、システムが STOPモードにある場合に、必要に応じてペリフェラルにカーネル・クロックを供給す ることができる

- カーネル・クロックの要求は、選択されているカーネル・クロックがHSIまたはCSIにな る起動時間を短縮するために、システムSTOPモード中にHSIまたはCSIの起動を 維持することが出来る

- システムSTOPモードでは、LSIとLSEのクロックはペリフェラルに利用可能

UARTやI2Cなどの特定のペリフェラルは、処理のためのカーネル クロックを要求するイベントを非同期的に検出することができます。 RCCは、ペリフェラルを割り当てているCPUがCSTOPモードにあ る場合や、システムがSTOPモードにある場合に、必要に応じて ペリフェラルにカーネルクロックを供給することができます。 カーネルクロックリクエストは、選択されているカーネルクロックが HSIまたはCSIです。

起動時間を短縮するために、システムSTOPモード中にHSIまた はCSIの起動を維持することができます。

システムSTOPモードでは、LSIとLSEのクロックはペリフェラルに 利用可能です。

### ペリフェラル・クロック・ゲーティング

- カーネル・クロックは、以下のいずれかの条件を満たす場合に、D1またはD2ドメインのペリフェラルPERxに供給される

- 1. ペリフェラルが割り当てられているCPUがCRUNモードで、かつPERxEN='1'のとき

- 2. ペリフェラルが割り当てられているCPUがCSLEEPモードで、かつPERxLPEN='1'のとき

- 3. ペリフェラルが割り当てられているCPUがCSTOPモードで、かつPERxAMEN='1'のとき、 さらにペリフェラルがカーネル・クロック要求を生成しており、かつカーネル・クロックソースが HSIまたはCSIのとき

- 4. ペリフェラルが割り当てられているCPUがCSTOPモードで、かつPERxAMEN='1'のとき、 さらにペリフェラルのカーネル・クロックソースがLSEまたはLSIのとき

- バス・インタフェース・クロックは、条件1または2が満たされたときにのみ ペリフェラルに供給される

D1またはD2ドメインに配置されたペリフェラルに対して、以下の条件が満たされた場合にカーネルクロックが供給されます。

- 1. ペリフェラルが割り当てられているCPUがCRUNモードで、かつそのイネーブルビットが'1'に設定されている場合。

- 2. ペリフェラルが割り当てられているCPUがCSLEEPモードで、 かつそのLP-イネーブルビットが'1'に設定されている場合。

- 3. ペリフェラルが割り当てられているCPUがCSTOPモードで、 かつそのLP-イネーブルビットが'1'に設定されており、さらに ペリフェラルがカーネルクロック要求を生成しており、かつ カーネルクロックソースがHSIまたはCSIである場合。

- 4. ペリフェラルが割り当てられているCPUがCSTOPモードで、 かつそのLP-イネーブルビットが'1'に設定されており、さらに ペリフェラルのカーネルクロックソースがLSEまたはLSIであ る場合。

バスインタフェースクロックは、条件1または2が満たされたときにのみペリフェラルに供給されます。

### ペリフェラル・クロック・ゲーティング 27

- **D3**ドメインのペリフェラルPERxに**カーネル・クロック**が供給されるのは、 以下のいずれかの条件を満たす場合

- 1. ペリフェラルが割り当てられているCPUがCRUNモードで、かつPERxEN='1'のとき

- 2. ペリフェラルが割り当てられているCPUがCSLEEPモードで、かつPERxLPEN='1'のとき

- 3. ペリフェラルが割り当てられているCPUがCSTOPモードで、かつD3ドメインがDRUNモードのとき、 さらにPERxAMEN='1'のとき

- 4. ペリフェラルが割り当てられているCPUがCSTOPモードで、かつD3ドメインがDSTOPモードで、 さらにPERxAMEN='1'のとき、 さらにペリフェラルがカーネル・クロック要求を生成しており、かつカーネル・クロック・ソースが HSIまたはCSIのとき

- 5. ペリフェラルが割り当てられているCPUがCSTOPモード、かつD3ドメインがDSTOPモードで、かつPERxAMEN='1'、さらにペリフェラルのカーネル・クロック・ソースがLSEまたはLSIの場合

- バス・インタフェース・クロックは、条件1、2、3が満たされたときにのみ ペリフェラルに供給される

D3ドメインのペリフェラルPERxにカーネルクロックが供給されるのは、 以下のいずれかの条件を満たす場合です。

- ペリフェラルが割り当てられているCPUがCRUNモードで、そのイネーブルビットが'1'に設定されている場合。

- 2. ペリフェラルが割り当てられているCPUがCSLEEPモードで、 PERxLPEN='1'のとき。

- 3. ペリフェラルが割り当てられているCPUがCSTOPモードで, D3ドメインがDRUNであり, そのLP-イネーブルビットが'1'に設定されている場合。

- 4. ペリフェラルが割り当てられているCPUがCSTOPモードで、D3ドメインがDSTOPであり、そのLP-イネーブルビットが'1'に設定されており、ペリフェラルがカーネルクロック要求を生成しており、カーネルクロックソースがHSIまたはCSIである場合。

- 5. ペリフェラルが割り当てられているCPUがCSTOPモードで, D3ドメインがDSTOPモードであり, そのLP-イネーブルビットが'1'に設定されており, ペリフェラルのカーネルクロックソースがLSEまたはLSIである場合。

バスインタフェースクロックは、条件1、2、3が満たされたときにのみペリフェラルに供給されます。

# 割込み 28

| - | ı | - |    |  |

|---|---|---|----|--|

| м | ) | С | )  |  |

| _ | а | т | ١. |  |

| 割込みイベント           | 説明                     |

|-------------------|------------------------|

| LSEクロックセキュリティシステム | LSE発振回路で障害が検出されたときにセット |

| HSEクロックセキュリティシステム | HSE発振回路で障害が検出されたときにセット |

| PLL1レディ割込みフラグ     | PLL1ロックに起因するクロックレディ    |

| PLL2レディ割込みフラグ     | PLL2ロックに起因するクロックレディ    |

| PLL3レディ割込みフラグ     | PLL3ロックに起因するクロックレディ    |

| HSEレディ            | HSE発振回路に起因するクロックレディ    |

| HSIレディ            | HSI発振回路に起因するクロックレディ    |

| CSIレディ            | CSI発振回路に起因するクロックレディ    |

| HSI48レディ          | HSI48発振回路に起因するクロックレディ  |

| LSEレディ            | LSE発振回路に起因するクロックレディ    |

| LSIレディ            | LSI発振回路に起因するクロックレディ    |

このスライドでは、RCCの割込みについて説明します。LSEとHSE のクロックセキュリティシステム、PLLレディ、6つのオシレータレ ディ信号は、割込みを発生させることができます。

# 関連ペリフェラル 29

- 必要に応じて、このペリフェラルに関連する以下のトレーニングをご参照ください。

- STM32H7電源コントロール(PWR)

- STM32H7非同期割込み/イベントコントローラ(EXTI)

このトレーニングに加えて、電源制御と割込みコントローラのトレーニングが役に立つと思います。