STM32H7低電力タイマ(LPTIM)のプレゼンテーションにようこそ。 ここでは、タイミング機能群を備えており、低電力モードでも波形 生成が可能であるこのペリフェラルの機能の説明を行います。

## 概要

2

LPTIM は 16ビット・タイマ クロック・ソースの多様性により、LPTIM は STM32H7マイクロコントローラで利用可能な 多くの低電力モードで実行し続けることが可能

#### 機能概要

- 非同期動作機能

- 超低消費電力

- 低電力モードからのウェイクアップのための タイムアウト機能

STM32H7マイクロコントローラに搭載されている低電力タイマペリフェラルには、低電力モードでも動作可能な 16ビット タイマが備わっています。これは、柔軟性の高いクロック供給スキームにより可能となりました。低電力タイマペリフェラルには、基本汎用タイマ機能が備わっています。低電力タイマの主要機能の 1 つは、非同期カウントモードに設定された場合に、どの内部クロックソースもアクティブではなくとも動作し続ける能力です。

- 多数の選択可能クロック・ソースを通じた柔軟性の高いクロック供給スキーム

- 内部クロックソース:LSE、LSI、PCKL1、PLL2P、PLL3R、PER\_CK クロック

- LPTIM「LPTIM\_IN1」入力経由の外部クロック・ソース(オンチップ・オシレータが実行していないときに動作、パルス・カウンタ・アプリケーションによって使用)

- 最大8つの外部トリガ

- アクティブ・エッジは次から設定可能:立ち上がりエッジ、立ち下がりエッジ、両エッジ

- 誤ったトリガを回避するためのデジタル・グリッチ・フィルタ

- 2 種類の動作モード: 連続とワンショット

低電力タイマの主な機能は、ほとんどすべてのクロックソースがオフになっている場合であっても動作し続ける能力です。低電力タイマには、非常に柔軟性の高いクロック供給スキームがあります。LSE、LSI、PCKL1、PLL2P、PLL3R、PER\_CK の各オンチップクロックソースからクロック供給を受けることができます。あるいは、低電力タイマの「LPTIM\_IN1」入力経由の外部クロックソースからクロック供給を受けることも可能です。この後者の機能は、「パルスカウンタ」アプリケーションの構築に用いられ、ガスメータなどのような計量アプリケーションに対する主要機能となります。低電力タイマは、設定可能な極性を持つ最大8つの外部トリガソースに対応しています。外部トリガ入力は、ノイズの多い動作環境で発生するおそれのある誤ったトリガをキャンセルするデジタルフィルタを備えています。

低電力タイマは、連続モードとワンショットモードのいずれかで動作するように設定できます。ワンショットモードはパルス波形の生成に用いられ、連続モードは PWM 波形の生成に用いられます。

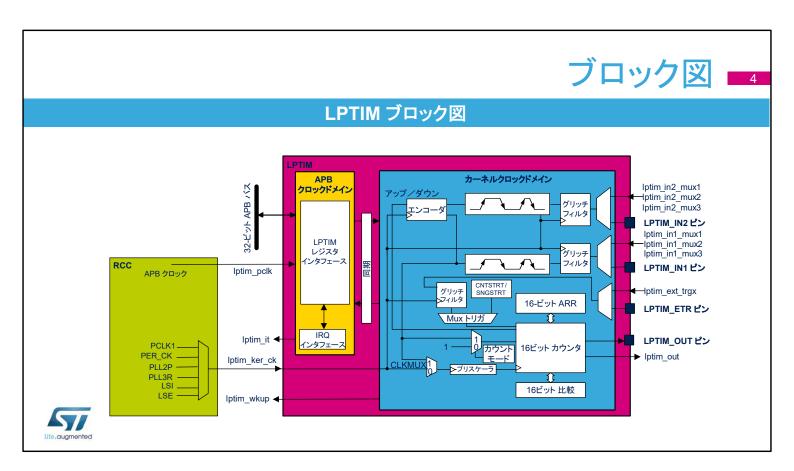

低電力タイマは、2 つのクロックドメインを持つペリフェラルです。 APB クロックドメインには、ペリフェラルの APB インタフェースが 含まれています。カーネルクロックドメインには、低電力タイマペ リフェラルのコア機能が含まれています。カーネルクロックドメイ ンは、タイマの「LPTIM\_IN1」入力経由の外部クロックソースから の内部クロックソースによってクロック供給を受けることができま す。

低電力タイマペリフェラルには、2 のべき乗プリスケーラを通じて供給される 16ビット タイマが搭載されています。低電力タイマペリフェラルには、タイマの「LPTIM\_OUT」出力上の PWM 波形信号出力のために、周期とデューティーサイクルの設定にそれぞれ用いられる 16ビット 自動リロードレジスタと 16ビット 比較レジスタが搭載されています。

低電力タイマは、ペリフェラルの「lptim\_in1\_mux」入力と「lptim\_in2\_mux」入力を用いて、インクリメンタル直交エンコーダセンサとのインタフェースに使用できるエンコーダモード機能を備えています。どちらの入力もグリッチフィルタ回路を備えています。

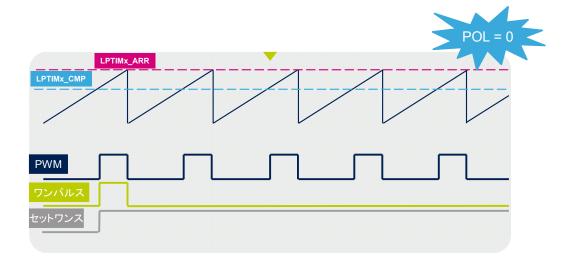

LPTIM\_CFGR レジスタのビットフィールド 'WAVE' および LPTIM\_CR レジスタの 'SNGSTRT' との組み合わせにより、 LPTIM\_CMP レジスタと LPTIM\_ARR レジスタが出力波形の制御に使用されます。

出力波形は、周期とデューティーサイクルが LPTIM\_ARR レジスタと LPTIM\_CMP レジスタによってそれぞれ制御される典型的 なPWM 信号です。あるいは、最後の出力状態が設定された波形によって定義される単一パルスとなります。

最後の出力状態がその波形の最初のものと同じである場合には、 ワンパルスモードが設定されます。

そうではない場合には、セットワンスモードが設定されます。 低電力タイマの出力極性は、LPTIM\_CFGR レジスタの 'WAVPOL' ビットフィールドを通じて制御されます。

### タイマ・カウンタのリセット

- タイマ・カウンタのリセットによって、LPTIM CNT レジスタの内容がリセットされる

- 2種類のカウンタ・リセット・メカニズムが可能

- 同期カウンタ・リセット・メカニズム

- LPTIM CR レジスタの COUNTRST ビットが'1'にセットされると、LPTIM\_CNT レジスタの内容は リセットされる このリセットは、3カーネル・クロック・サイクル分の同期遅延の後に行われる

(Iptim ker ck カーネル・クロック信号は APB クロックとは異なることがあります)

- 非同期カウンタ・リセット・メカニズム

- LPTIM CR レジスタの RSTARE ビットが'1'にセットされると、LPTIM CNT レジスタに対する あらゆる読出しアクセスによって、LPTIM CNT レジスタの内容が非同期にリセットされる

低電力タイマは、LPTIM CNT レジスタの内容を '0' にリセットす るカウンタリセット機能を備えています。

同期カウンタリセットメカニズムと非同期カウンタリセットメカニズ ムの2種類のカウンタリセットメカニズムが可能です。

COUNTRST ビットをセットすることによって、同期カウンタリセット が行われます。このリセットの同期的な性質のため、3LPTIM カーネルクロックサイクル分の同期遅延の後にリセットが行われ ます。

RSTARE ビット がセットされていると、LPTIM CNT レジスタに対 する次回の APB 読出しアクセスで、非同期カウンタリセットが行 われます。

# エンコーダ・モード

#### エンコーダ・モード

- 汎用タイマにおけるエンコーダ・モードと同一の動作モード

- 連続モードで LPTIM が動作中のみ使用可能

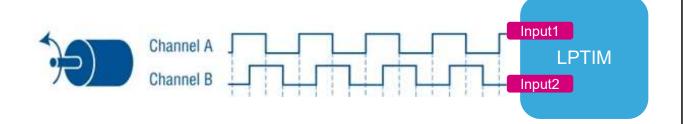

低電カタイマは、ペリフェラルの「Input1」入力と「Input2」入力を用いて、インクリメンタル直交エンコーダセンサとインタフェース可能なエンコーダモード機能を備えています。どちらの入力もグリッチフィルタ回路を備えています。

エンコーダ機能は、汎用タイマに搭載されているものに類似しています。

エンコーダモード機能を使用するためには、低電力タイマが連続モードで動作中である必要があります。

注意すべき重要な点は、低電力タイマ1と2のみにエンコーダモード機能が搭載されているということです。

| 割込みイベント                | 説明                                                                                             |

|------------------------|------------------------------------------------------------------------------------------------|

| 比較一致                   | カウンタ・レジスタ(LPTIM_CNT)の内容が比較レジスタ(LPTIM_CMP)の内容と<br>一致したときに、割込みフラグが立つ                             |

| 自動リロード一致               | カウンタ・レジスタ(LPTIM_CNT)の内容が自動リロード・レジスタ(LPTIM_ARR)の<br>内容と一致したときに、割込みフラグが立つ                        |

| 外部トリガイベント              | 外部トリガが検出されたときに、割込みフラグが立つ                                                                       |

| 自動リロード・レジスタ<br>への書込み完了 | LPTIM_ARR レジスタへの書込み動作が完了したときに、割込みフラグが立つ                                                        |

| 比較レジスタへの書込<br>み完了      | LPTIM_CMP レジスタへの書込み動作が完了したときに、割込みフラグが立つ                                                        |

| 方向の変更                  | エンコーダ・モードに使用され、方向の変更を強調するために、アップカウント方向の変更を強調するアップフラグとダウンカウント方向の変更を強調するダウンフラグの2つの割込みフラグが内蔵されている |

低電力タイマペリフェラルは、6種類の割込みソースを備えています。

- カウンタレジスタ LPTIM CNT の内容が比較レジスタ LPTIM CMP の内容と一致するか、それよりも大きい場合に、「比較一致」割込 みが立ちます。

- カウンタレジスタの内容が自動リロードレジスタの内容と一致した ときに、「自動リロード」割込みが立ちます。

- 有効な外部トリガが検出されたときに、「外部トリガイベント」割込 みが立ちます。

- 異なる 2 つのクロックドメインに含まれているペリフェラルの APB インタフェースロジックからペリフェラルのコアロジックへの、 LPTIM ARR レジスタと LPTIM CMP レジスタそれぞれの内容の 転送が完了したときに、「自動リロードレジスタへの書き込み完 了」割込みと「比較レジスタへの書込み完了」割込みが立ちます。 これら2つの割込みは、APB インタフェースクロックと比べてペリ フェラルコアクロックが遅すぎる場合に、これら2つのレジスタへ の書込みのステータスをポーリングするオーバヘッドの緩和に役 立ちます。

- エンコーダモード機能が有効であり、カウント方向がアップからダ ウンへ、またはその反対に変更されたときに、「アップ/ダウン方 向の変更」割込みが立ちます。低電力タイマのカウンタのカウント 方向は、直交センサの回転方向を反映しています。

# 低電力モード 📑

| モード     | 説明                                                             |

|---------|----------------------------------------------------------------|

| RUN     | アクティブ                                                          |

| SLEEP   | アクティブ<br>ペリフェラル割込みによって、デバイスは SLEEP モードを終了                      |

| STOP    | アクティブ<br>ペリフェラル・レジスタの内容は保持され、ペリフェラルの割込みにより、デバイスが<br>STOPモードを終了 |

| STANDBY | パワーダウン<br>ペリフェラルは、STANBY モード終了後に再初期化する必要がある                    |

RUN、SLEEP、STOP の各電源モードにおいて、低電力タイマペリフェラルがアクティブとなります。

低電カタイマは、SLEEP モードと STOP モードからマイクロコントローラをウェイクアップできます。

参照

10

- 詳細と追加情報については、以下をご参照ください

- アプリケーションノート AN4865: Low-power timer (LPTIM) applicative use-cases on STM32 MCUs

詳細については、弊社ウェブサイトから入手可能な以下の関連資料をご参照ください。