STM32 ダイレクトメモリアクセスコントローラ(DMA)のプレゼンテーションへようこそ。ここでは、STM32 ペリフェラルのデータ転送の処理に広く使われている本モジュールの主な特徴を説明します。

### 概要

- DMA1/2 の特徴

- デュアル AHB マスタバス

- 柔軟な設定

- ハードウェアおよびソフトウェアの優先順位管理

- 設定可能なデータ転送モード

- ペリフェラルからメモリ、メモリからペリフェラル、メモリからメモリのモード

#### アプリケーション側の利点

- D2 ドメインのタイマ、A/D コンバータ、および通信ペリフェラルの DMA サポート

- CPU からデータ転送管理負荷を軽減

- 簡単な統合

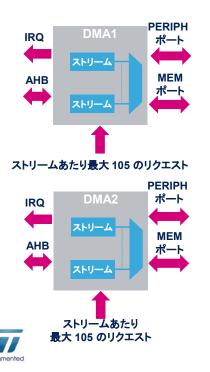

STM32MP1 シリーズに組込まれたダイレクトメモリアクセスの 2 つの同一インスタンス(DMA1 および DMA2)は、ペリフェラルとメモリ間およびメモリとメモリ間の高速データ転送を実現するために使用されます。 DMA により、CPU を動作させずに、データを高速で移動することができます。 これによって CPU リソースを他の動作のために確保できます。

この DMA コントローラでは、高機能なバスマトリックスアーキテクチャに基づいて強力なデュアル AHB マスタバスアーキテクチャと、独立した FIFO を組み合わせて、システムのバンド幅を最適化しています。

- DMA1 と DMA2 にわたって 16 の独立した設定可能なストリーム

- ストリームは転送元と転送先の間の単方向転送リンクを提供

- それぞれのストリームに対するハードウェアリクエストまたはソフトウェアトリガ

- ソフトウェアでプログラム可能な優先順位(等しい場合はハードウェアによる優先順位)

- 独立した柔軟性の高いストリーム設定

- 完全にプログラム可能な転送(データ形式、インクリメントタイプ、アドレス)

- 独立したストリーム割込みフラグ(1/2 転送、転送完了、転送エラー、...)

- ストリームごとの専用の 4x32bit FIFO メモリ(FIFO モードは有効化/無効化が可能)

- サーキュラバッファおよびダブルバッファ管理のサポート

- 次のエラーの場合、障害ストリームは自動的に無効化

- DMA 転送エラー、ダイレクトモードエラー

2 つの DMA コントローラ(DMA1 と DMA2)は合計 16 ストリームを搭載し、それぞれが多くのペリフェラルからのメモリアセスリクエストを管理します。各ストリームは柔軟なハードウェアリクエストを受け、ソフトウェアトリガをサポートしています。ストリームのソフトウェア優先順位はプログラム可能で、優先順位が等しい場合はハードウェア優先順位が使用されます。ストリームは個別に設定可能です。各ストリームでは、独自のデータ形式、インクリメントタイプ、転送元および転送先の両方のデータアドレスを保持します。

ストリームごとの 4ワードの FIFO によって、データのパッキング /アンパッキングおよびバースト転送を実行できます。 独立したストリーム割込みフラグによって、1/2 転送、転送完了、 転送エラーイベントをトリガすることができます。転送エラーの場合、障害ストリームは自動的に無効になり、他のアクティブな DMA ストリームに影響を及ぼしません。

## 個別の DMA ストリームの柔軟性 ■4

- プログラム可能な機能

- 独立した転送元および転送先のデータサイズ(8/16/32bit)

- 独立した転送元および転送先の転送タイプ:

- シングルまたはインクリメンタルバースト(4x、8x、または 16xビート)

- 独立した転送元および転送先アドレス

- 独立した転送元および転送先のポインタアドレスインクリメント

- プログラム可能な転送データ数:最大 65,535リクエスト

- サーキュラモード

- 連続データフローでサーキュラバッファを処理

- 転送元および転送先のアドレスは自動的にリロード

- データ転送サイズは自動的にリロード

- ダブルバッファモード(ダブルバッファモードは有効化/無効化が可能)

ストリームごとに、転送元および転送先のデータサイズ形式を個 別に設定可能です(8、16、または32bit パケット)。 転送元と転 送先の転送タイプは、シングルモードまたはバーストモードに個 別にプログラムできます。転送元および転送先のアドレスおよび ポインタのインクリメントも個別に設定可能です。転送データサイ ズは最大 65535 まで事前にプログラムできます。データの連続 フローをサポートするためにサーキュラバッファモードが使用でき ます。転送元と転送先のアドレスおよび転送データ数は、転送が 完了すると自動的にリロードされます。ダブルバッファモードでは、 2 つのメモリバッファ間の切り替えをハードウェアで処理できます。

- メモリ間モード

- ストリームが有効になるとすぐに転送開始します(ハードウェアリクエストなし)。

- ペリフェラルからメモリ、メモリからペリフェラル

- DMA ペリフェラルポートでの転送は、ハードウェアリクエストごとに発生します。

- 転送が完了すると、リクエストは確認応答されます。

- ペリフェラル DMA リクエスト信号は、DMA リクエストルータ(DMAMUX)を介して DMA コントローラのストリームリクエストラインにルーティングされます。

メモリ間モードでは、1 つのアドレス位置から別のアドレス位置に ハードウェアリクエストなしに転送ができます。ストリームが設定 されて有効になると直ちに転送が開始されます。ペリフェラルへ、 またはペリフェラルからデータが転送される場合、選択されたペリフェラルからのハードウェアリクエストを使用して、DMA ペリフェラルポートでのデータ転送がトリガされます。転送が完了すると、リクエストは確認応答されます。

# FIFO: データパッキング/アンパッキング

- サポートされている動作:

- 8bit / 16bit → 32bit / 16bit (パッキング)

- 32bit / 16bit → 8bit / 16bit (アンパッキング)

FIFO モードが有効になっている(ダイレクトモードが無効になっている)場合、DMA コントローラは転送元と転送先の間のデータ形式の違いを処理します(データのパッキングとアンパッキング)。 内部 FIFO によって、DMA ストリームではソフトウェアオーバーヘッドと AHB バス上のトランザクション数を削減できます。

- 閾値レベルによってメモリへの/メモリからのデータ転 送がトリガされます。

- 各ストリームには個別の設定可能な閾値レベルがあり。 ます。

- 使用可能な 4 つの閾値レベル: FIFO ½ フル、FIFO 1/2 フル、 FIFO ¾ フル、FIFO フル

- バーストモード:

- バーストモードは FIFO モードが有効なとき(ダイレクトモード無 効時)にのみ使用できます。

- 使用可能なバーストモード:

- INC4:1バースト = 4ビート(4ワード、8ハーフワード、または 16バイ

- INC8:1 $\vec{N}$ - $\vec{A}$ -

- INC16:  $1\vec{N} \vec{\lambda} = 16 \vec{E} \vec{k} (16 \vec{N} \vec{A} \vec{k})$

- FIFO 閾値はバーストサイズに適合している必要があります。

|           | 10     |

|-----------|--------|

| life.augm | nented |

| バーストサイズ      | 許容される閾値<br>レベル                                                       |

|--------------|----------------------------------------------------------------------|

| 4ビート(INC4)   | 1/4、1/2、3/4、フル                                                       |

| 8ビート(INC8)   | ½、フル                                                                 |

| 16ビート(INC16) | フル                                                                   |

| 4ビート(INC4)   | ½、フル                                                                 |

| 8ビート(INC8)   | フル                                                                   |

| 4ビート(INC4)   | フル                                                                   |

|              | 4ビート(INC4)<br>8ビート(INC8)<br>16ビート(INC16)<br>4ビート(INC4)<br>8ビート(INC8) |

シングルモードまたはバーストモードでは、FIFO 内のデータがメ モリに/メモリから転送されるタイミングが FIFO 閾値によって決 まります。

閾値レベルには、ストリームごとに「FIFO フルの 1/4」から「FIFO フル」までの4つの設定可能なレベルがあります。メモリポート の転送方向に応じて、FIFO 閾値に達したときに、FIFO はメモリ 位置からデータで充填されるか、またはメモリ位置へデータが排 出されます。

バーストモードは FIFO モードが有効なときにのみ使用できます。 バーストモードに設定している場合、FIFO 閾値はバーストサイ ズに適合している必要があります。そうすることで、DMA ストリー ムにおいて、FIFO でバーストデータを利用できるようになり、 バースト転送を実行することができます。

# サーキュラおよびダブルバッファモード

- サーキュラモード:

- このモードでは、すべての FIFO の機能と DMA イベント(TC、HT、TE)を使用できます。

- データ項目の数は、自動的にリロードされ、転送が再開されます。

- このモードはメモリ間転送では使用できません。

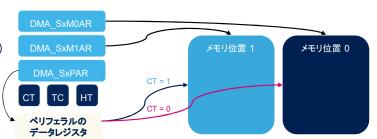

- ダブルバッファモード: (サーキュラモードのみ)

- 2 つのメモリアドレスレジスタを使用できます (DMA SxM0AR と DMA SxM1AR)。

- 2 つのメモリバッファ間の切り替えをハードウェアで 処理できます。

- メモリ間モードは禁止されています。

- どちらの転送先がデータ転送に使用されているかを 監視するために、フラグと制御ビット(CT)が利用でき ます。

- メモリ位置 0 または 1 への転送が完了したとき、TC フラグがセットされます。

DMA コントローラはサーキュラモードをサポートしており、一度に転送するデータ項目の数を設定し、転送完了イベント後に自動的に転送を再開できます。ダブルバッファモードは、サーキュラモードでのみ使用できます。それによって、転送完了イベントが発生するたびに、ハードウェアによって2つのメモリアドレス間の切り替えを自動的に行うことができます。ダブルバッファモードでは、どちらの転送先がデータ転送に使用されているかを監視するために、ステータスフラグと制御ビット(CT)が利用できます。

DMA コントローラでは、ストリームごとに最大 115チャネル(リクエスト)を備えた 8 つのストリームへのアクセスが提供されています。8 つのストリームのそれぞれは、専用のハードウェア DMAチャネル(リクエスト)に接続されます。

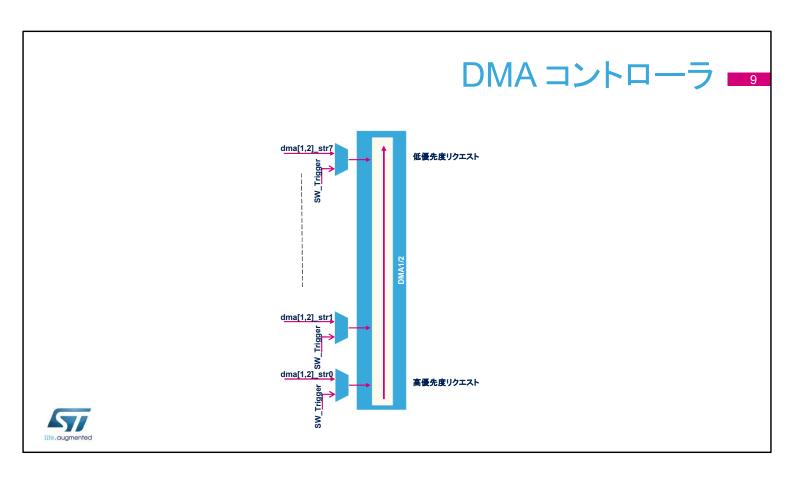

DMA ストリームリクエスト間の優先順位は、ソフトウェアによって プログラム可能です(最高、高、中、低の 4レベル)。レベルが等 しい場合はハードウェアによって決まります(リクエスト 0 はリク エスト 1 よりも優先、など)。

DMA コントローラのストリームリクエストのそれぞれは、DMA リクエストルータ(DMAMUX)によって最大 115 まで可能なペリフェラルからの DMA リクエストに接続することができます。この選択は、ソフトウェアによって設定可能であり、これによって多くのペリフェラルが DMA リクエストを発生できるようになります。各ストリームは、メモリ間転送のためのソフトウェアトリガもサポートしています。

#### 各チャネルの割込みイベント

| 割込みイベント     | 説明                                                                                                              |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| 1/2 転送      | データ転送サイズの半分が完了した時にセットされます。                                                                                      |

| 転送完了        | データ転送サイズの全部が完了した時にセットされ、MDMA または DMAMUX へのトリガとして使用できます。                                                         |

| 転送エラー       | データ転送中にバスエラーが発生した時にセットされます。                                                                                     |

| FIFO エラー    | FIFO アンダーラン/オーバーラン状態、または閾値-バーストサイズの不適合のときに<br>セットされます。                                                          |

| ダイレクトモードエラー | メモリインクリメントが無効になっているとき、ペリフェラルからメモリのモードで、ダイレクトモードにおいてのみ起き得ます。<br>新しいデータがメモリ位置に転送されようとしているが、前の転送がまだ完了していないことを示します。 |

各 DMA ストリームは、この割込みイベント群を使用して設計さ れています。データの半分が転送されると、1/2 転送割込みフラ グがセットされます。転送が完了すると、転送完了フラグがセット されます。データ転送中にエラーが発生すると、転送エラーフラ グがセットされます。FIFO エラーフラグは、DMA の FIFO アン ダーラン/オーバーラン状態が検出されるか、閾値-バーストサ イズの不適合がある場合にセットされます。ダイレクトモードエ ラーフラグは、ペリフェラルからメモリのモードで、ダイレクトモード において、メモリインクリメントが無効になっているときに、セットさ れます。これは、新しいデータがメモリ位置に転送されようとして いるが、前の転送がまだ完了していないことを示します。

# 関連ペリフェラル 📶

- このペリフェラルに関連している下記のトレーニングを参照してください。

- DMA request router (DMA リクエストルータ)

- Master direct memory access controller(マスタダイレクトメモリアクセスコントローラ)

詳しい情報については、DMA リクエストマルチプレクサ (DMAMUX)とマスタダイレクトメモリアクセス(MDMA)ペリフェラ ルに関連するトレーニングスライドをご参照ください。