# STM32MP1 – QUADSPI

Quad-SPI メモリインタフェース

1.0 版

STM32 Quad-SPI メモリインタフェースのプレゼンテーションに

ようこそ。ここでは、外部メモリをマイクロプロセッサに接続するた

めに幅広く使用されるこのインターフェースの機能について説明し

ます。

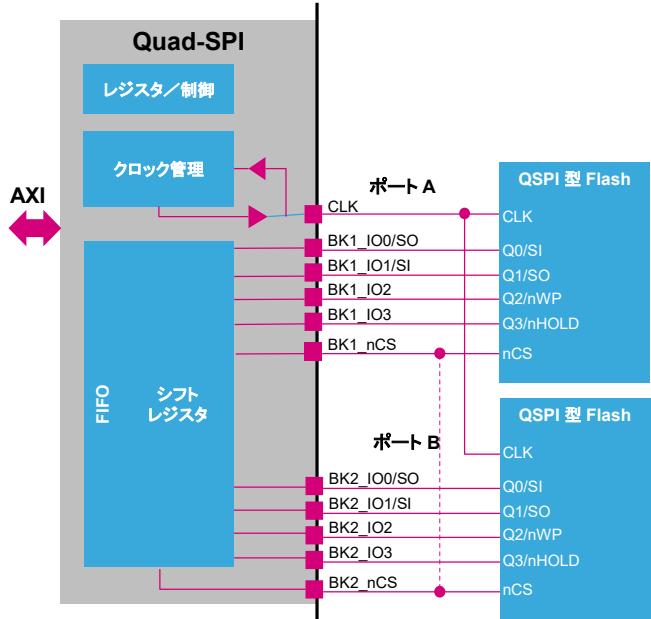

# シングルまたはデュアル Quad-SPI アクセス

2

## ピン数と性能を考慮した柔軟な選択

- Quad-SPI は、シングルおよびデュアル外部 Flash 操作をサポート(\*)。

- ポート A およびポート B は同じタイプと特性を持つ 2 つのメモリで同時に動作可能。

- ポート A およびポート B は異なるタイプの Flash メモリで異なるタイミングで動作(例:NOR + NAND)。

- 4bit または 8bit のデータバスを選択可能

\*:部品番号による。

STM32MP1 マイクロプロセッサ内に組み込まれている Quad-SPI メモリインタフェースには、マイクロコントローラで外部 SPI および Quad-SPI のメモリと通信可能です。

Quad-SPI メモリインタフェースは、1 つまたは 2 つの外部メモリの接続をサポートします。つまり、メモリとマイクロコントローラで 4bit または 8bit のデータバスでデータを転送できるということです。これによって、接続に必要なピン数(シングル接続の場合は 6、ダブル接続の場合は 10)と、データ転送の性能(シングル接続の場合は 4bit、ダブル接続の場合は 8bit)を考慮してユーザは柔軟に選択できます。

- 3 種類の動作モード

- インダイレクト

- ステータスポーリング

- メモリマップド

- 最大 100MHz の最適化された動作(\*\*)

- デュアル Flash モード\*(2 つの Flash メモリに並列にアクセスする 8bit)

- シングルデータレート(SDR)とデュアルデータレート(\*) (DDR) のサポート

\*:部品番号による。

\*\*:1.71~3.6V の全範囲に及ぶ VDD の場合です。

Quad-SPI メモリインタフェースには、3 種類の動作モードが備わっています。デュアル Flash モードのサポートによって外部メモリとの通信を最適化し、1 回の読み出しサイクルで 8bit のアクセスが可能です。また、シングルデータレートおよびデュアルデータレートの両方の動作をサポートしています。

## CPU の負荷を軽減する柔軟な動作モード

- インダイレクトモード

- すべての動作がレジスタで実行されます(従来の SPI)

- ステータスポーリングモード

- Flash ステータスレジスタを定期的に自動で読み出し、一致時に割込みを生成

- メモリマップモード

- 外部 Flash が読み出し時に内蔵メモリと同様にアクセス

Quad-SPI メモリインタフェースは、3 種類の動作モードで動作します。

1. インダイレクトモードでは、従来の SPI インタフェースとして動作し、すべての動作がレジスタで実行されます。

2. ステータスポーリングモードでは、Flash ステータスレジスタが割込みの生成を伴って定期的に読み出されます。

3. メモリマップモードでは、外部 Flash を読み出し時に内蔵メモリと同様にアクセスできます

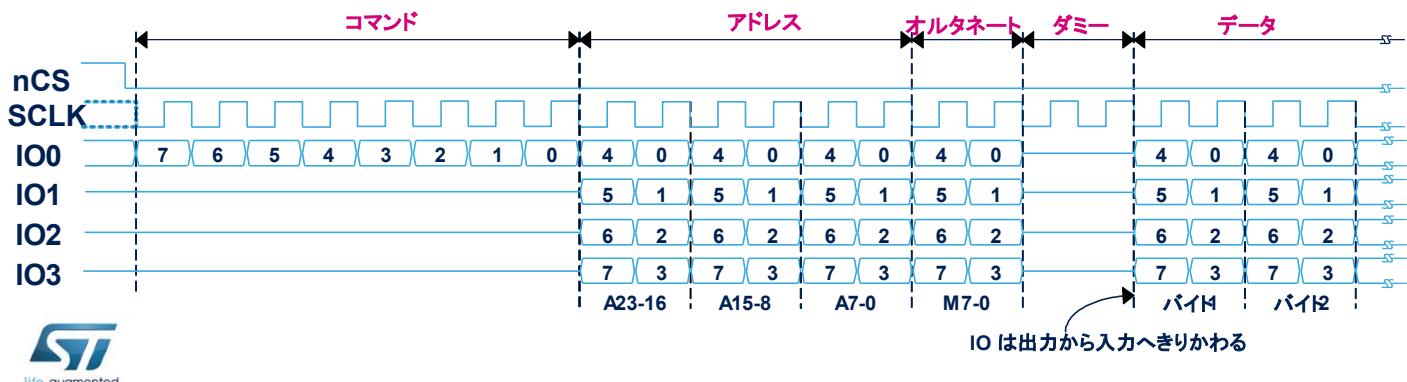

# フレームフォーマット

5

## シングル／デュアル／Quad-SPI のシリアル Flash メモリとの互換性

- Quad-SPI コマンドには、最大 5 個の設定可能なフェーズが含まれる

- フェーズはそれぞれ有効または無効に設定可

- 各フェーズの長さが設定可能

- 各フェーズのライン数が設定可能

Quad-SPI メモリインタフェースには、フレームフォーマット設定における高い柔軟性が備わっています。この機能により、どのようなシリアルFlashメモリにも対応できる柔軟性があります。Flash メモリにユーザは、5 つのフェーズをそれぞれ有効または無効にして、各フェーズの長さと使用されるライン数を設定できます。

# インダイレクト動作モード

6

## 従来の SPI インタフェース

- 従来の通信 IP と同じ使用方法

- データはデータレジスタの書き込みや読み出しで転送

- バイト数はデータ長レジスタで指定

- データ FIFO の管理

- 割込みフラグ(転送完了フラグ)

- DMA サポート

- コマンドの起動

- 命令が必要な場合にのみ命令を書き込むとき

- 命令とアドレスが必要な場合にのみアドレスを書き込むとき

- データフェーズが必要な場合にデータを書き込むとき

インダイレクト動作モードで使用される Quad-SPI メモリインターフェースは、従来の SPI インタフェースのように動作します。転送されるデータは、FIFO 付きのデータレジスタを経由します。データのアクセスは、ソフトウェアまたは DMA コントローラによって駆動され、Quad-SPI ステータスレジスタの関連する割込みフラグを使用します。

各コマンドは、命令のコンテキストに応じて、アドレス、データ命令の書き込みによって起動します。

# ステータスポーリング動作モード

7

## 軽減されるソフトウェアの負荷

- ステータスレジスタのポーリング用の特定のモード

- プログラム可能なレジスタ長: 8/16/24/32bit

- 定義されたレートで読み出し動作を繰り返す

- 応答のマスクや一致した場合には割込みを生成

- マスクはプログラム可能(PSMCR レジスタ)

- マスクされた値は、一致レジスタ(PSMAR)とビットごとに比較

- 比較の結果は、論理積または論理和を指定可能

- 成功時、割込みが生成(一致フラグで停止)

- 一致が発生した場合に自動停止

特別なモードが Quad-SPI インタフェースには実装されており、外部 Flash メモリでステータスレジスタを自律的にポーリングします。また、Quad-SPI インタフェースは、外部 Flash メモリのレジスタを定期的に読み出すようにも設定できます。返されるデータはマスクして、評価するビットを選択できます。選択されたビットは、一致レジスタに格納された必要な値と比較されます。比較の結果は次の 2 種類の方法で処理されます。論理積モードでは、選択されたビットすべてが一致している場合に、割込みが生成されます。論理和モードでは、選択されたビットの 1 つが一致している場合に、割込みが生成されます。一致が発生すると、Quad-SPI インタフェースを自動的に停止できます。

- プロジェクトへのシンプルなメモリの拡張

- 低電力での管理

- eXecute-in-Place (XiP) 用のプリフェッチ機能

- 外部 Flash がウェイターステートのある内部 Flash と認識

- 読出し動作は AXI インタフェースで自動的に生成

- フレームと OP コードは、インダイレクトモードで IP 設定中に定義

- ピン nCS がローに保持され、クロックが停止し、Quad-SPI バスをストールし、必要な場合にシーケンシャルな読出しを再開

- タイムアウトカウンタは、低電力の間はピン nCS をハイに解放

Quad-SPI メモリインタフェースには、メモリマップドモードもあります。このモードによる主なアプリケーションのメリットは、ウェイターステートの数を除き、内部や外部接続のメモリでの読出しアクセスに違いがないため、外部メモリ拡張が組み込みやすくなることです。

このモードは読出し動作にのみ適しており、外部メモリの低速を補うために外部 Flash メモリがウェイターステートのある内部 Flash とみなされます。このモードによってサポートされる最大サイズは 256MB に制限されます。

プリフェッチバッファが eXecute-in-Place (XiP)をサポートしているため、内部 RAM にダウンロードすることなく、外部メモリから直接コードを実行できます。

また、このモードは特定の Flash メモリによってサポートされる SIOO モード (Send Instruction Only Once) もサポートしており、コントローラで 1 回だけ命令を送信して、次のアクセスの命令フェーズを削除できます。

# 遅延データサンプリング

9

## ・信号が PCB レイアウトによって遅延している場合に役立つ機能

- ・サンプリングクロックは、 $\frac{1}{2}$ クロックサイクル分追加でシフト

- ・SDR モードでのみサポート

- ・出力データは、 $\frac{1}{2}$ システムクロックサイクル分シフト可能

- ・DDR モードでのみサポート

- ・さらに、専用の遅延ブロック DLYBQS によって、性能を向上させるためにサンプリングクロックのタイミングを微調整可能

遅延データサンプリングで、ユーザは PCB レイアウトの最適化における制約のために生じた信号の遅延を補正できます。これによって、アプリケーションは SDR モードで動作時にデータサンプリング時間を追加で  $\frac{1}{2}$  クロックサイクル分シフトできます。DDR モードでは、出力データを  $\frac{1}{2}$  システムクロックサイクル分シフトして、ホールドに関する制約を緩めることができます。QUADSPI 専用の遅延ブロックを有効にして、きめ細かい遅延をサンプリングクロックのタイミングに追加できます。

# 割込みおよび DMA

10

| 割込みイベント | 説明                                                          |

|---------|-------------------------------------------------------------|

| タイムアウト  | タイムアウトが発生するとセットされます。                                        |

| ステータス一致 | マスクされた受信データが一致レジスタの対応するビットと一致している場合に、自動ポーリングモードでセットされます。    |

| FIFO 閾値 | FIFO 閾値に達した場合にインダイレクトモードでセットされます。                           |

| 転送完了    | インダイレクトモードでプログラムされたデータ数が転送された場合や、任意のモードで転送が中断された場合にセットされます。 |

| 転送エラー   | インダイレクトモードで無効なアドレスにアクセスされているときにセットされます。                     |

- FIFO 閾値に達した場合に、インダイレクトモードで DMA リクエストを生成可能

Quad-SPI メモリインタフェースには、5 種類の割込みソースがあります。タイムアウト、自動ポーリングモードでのステータス一致（マスクされた受信データが一致レジスタの対応するビットと一致している場合）、FIFO 閾値、転送完了、転送エラーです。 FIFO 閾値に達した場合に、インダイレクトモードで DMA リクエストを生成できます。

# 低電力モード

11

| モード            | 説明                                            |

|----------------|-----------------------------------------------|

| RUN            | アクティブ。                                        |

| SLEEP          | アクティブペリフェラル割込みによって、デバイスは SLEEP モードを終了します。     |

| STOP + LP-Stop | 停止。ペリフェラルレジスタの内容を保持します。                       |

| LPLV-Stop      | 停止。ペリフェラルレジスタの内容を保持します。                       |

| STANDBY        | パワーダウン状態ペリフェラルは、STANDBY モード終了後に再初期化する必要があります。 |

Quad-SPI メモリインタフェースは、RUN モードおよび SLEEP モードではアクティブです。Quad-SPI 割込みによって、デバイスは SLEEP モードを終了します。STOP モードでは、Quad-SPI メモリインタフェースは停止し、レジスタの内容は保たれます。STANDBY モードでは、Quad-SPI はパワーダウン状態となり、後で再初期化する必要があります。

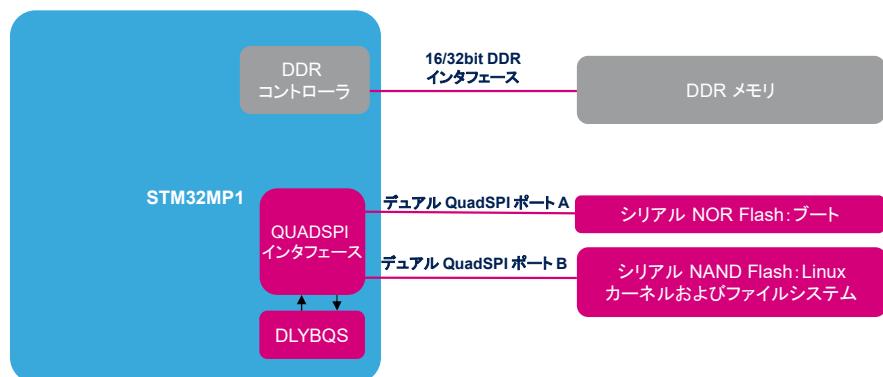

# アプリケーション例

12

- 外部 Quad-SPI はデュアル Flash モードで使用

- シリアル NOR: 初期段階ブートローダ (FSBL)

- シリアル NAND: ブートの 2 段階目 (カーネルとファイルシステムのロード) およびマストレージ

STM32MP1 マイクロプロセッサの Quad-SPI インタフェースは、サポートされているブートソースの 1 つです。これはデュアルクワッド設定で使用でき、1 つのポートはブートシークエンスの初期ステップでシリアル NOR Flash メモリにフックされ、もう 1 つのポートは Linux カーネルとファイルシステムを組み込んだ、アプリケーションのマストレージとして使用できるシリアル NAND Flash メモリに接続されます。インターフェースによってサポートされるハイスピードと、非常に少ないピン数のため、このようなセットアップによって最適化されたシステム組込みとコスト効率のよいソリューションが提供されています。

## 関連するペリフェラル

13

- 次のペリフェラルに関するトレーニングを参照してください。

- RCC(Quad-SPI クロック制御、Quad-SPI 有効化／リセット)

- 割込み(Quad-SPI 割込みマッピング)

- DMA および MDMA(Quad-SPI データ転送)

- GPIO(Quad-SPI 入出力ピン)

詳細については、RCC、割込み、DMA および GPIO に関するトレーニングスライドを参照してください。

# STM32 シリーズ全体の比較

14

| QUADSPI の機能 | STM32F4 | STM32F7 | STM32MP1 |

|-------------|---------|---------|----------|

| インスタンス数     | 1       | 1       | 1        |

| 最大速度        | 90MHz   | 100MHz  | 100MHz   |

| デュアル Flash  | 対応      | 対応      | 対応       |

| ソフトウェア互換性   |         |         | (*)      |

\* このインターフェースが Arm® Cortex®-M4

コアで管理されている場合

ローレベルドライバ

ソフトウェアの互換性:

■ 完全、またはほぼ完全

■ 部分

■ 互換性なし

Quad-SPI インタフェースは、STM32L4 および STM32F7 のシリーズと完全な互換性があり、このインターフェースが Arm Cortex-M4 コアで管理されている場合、このデバイスで開発されたアプリケーションをそのまま再利用できます。