こんにちは、STM32 HDMI-CEC コントローラモジュールのプレゼンテーションへようこそ。このプレゼンテーションでは、ユーザ環境にあるさまざまなオーディオビジュアル製品について、それらすべての間で高品位な制御機能を実現するコントローラの主な機能を説明します。

- デバイス管理インタフェースの提供

- HDMI-CEC v1.4 仕様に準拠

- 2 つのクロックソースオプションを用いた 32kHz CEC カーネル

- 複数の論理アドレスをサポート(OAR)

- 設定可能な Rx 許容誤差マージン

- ・ 受信エラー検出

- ・ 送信エラー検出

### アプリケーション側の利点

- 必要なのは 1ピンのみ

- バス固有のシーケンシング、 プロトコル、アービトレーション、タイミングを制御

- さまざまなオーディオビジュアル製品とデバイスパラ メータを交換

STM32 マイクロコントローラ内に統合された HDMI-CEC コントローラはハードウェア管理インタフェースを提供するもので、これにより STM32 はユーザ環境でさまざまな製品とデバイスパラメータを交換できるようになります。

この目的に沿って、設定可能なクロックソース、ペリフェラルアドレス、および多数の受信/送信イベントフラグが使用されます。 アプリケーションは、デバイスパラメータの交換に使用されるピン数の少ない標準インタフェースから恩恵を受けられます。

HDMI-CEC は、「High-Definition Multimedia Interface」「Consumer Electronics Control」の略です。コントローラは

HDMI-CEC v1.4 仕様に準拠しています。さまざまなオーディオ

ビジュアル製品とのインタフェースに必要な機能を提供します。

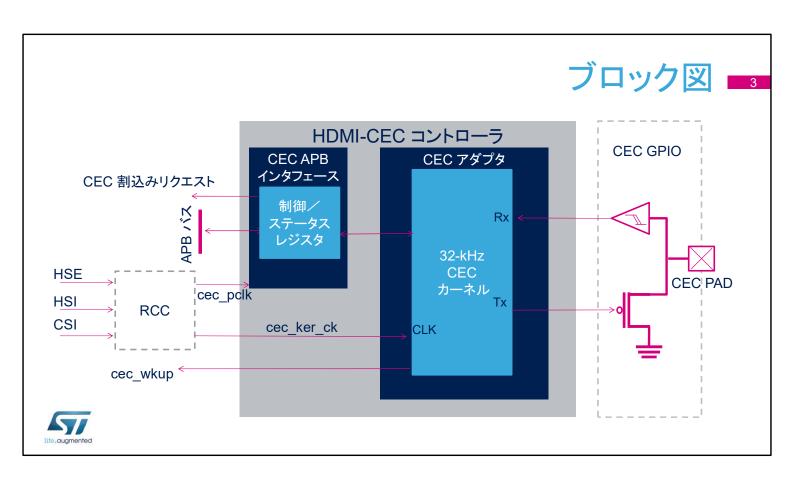

「CEC アダプタ」と「CEC アドバンストペリフェラルバス(APB)インタフェース」で構成されています。

「CEC アダプタ」はフレームのデコードやチェックなどの機能を提供し、「CEC APB インタフェース」は制御およびステータスレジスタ、データインレジスタとデータアウトレジスタ、および同期割込みリクエストを管理します。

HDMI-CEC コントローラには、「APB インタフェース」用の APB クロック(CEC\_PCLK)と「CEC アダプタ」用の 32kHz カーネルクロック(CEC\_KER\_CK)の 2 つのクロックを使用します。カーネルクロックは、HSE、CSI、または HSI クロックソースから取得できます。

## メッセージの構造

#### サポートするフレームフォーマット

- ・ メッセージ:

- 単一フレームで送信されます。このフレームは、スタートビットとそれに続くヘッダブロックによって構成され、これにオプションとして OP コードと可変長のオペランドブロックを含めることもできます。

ハイインピーダンス スタートビット ヘッダ OPCODE オペランド オペランド ・・・・ オペランド ハイインピーダンス

- ヘッダ、OP コード、オペランドブロック:

- 8bit ペイロード 最初に最上位ビットが送信され、その後にメッセージ終了(EOM)ビットと確認 応答(ACK)ビットが送信されます。

サポートされているフレームフォーマットは、スタートビットとそれに続くヘッダブロックによって構成され、これにオプションとしてOPコードと可変長のオペランドブロックを含めることもできます。ヘッダ、OPコード、オペランドブロックは8bitペイロードで構成され(最上位ビットが最初に送信される)、その後にメッセージ終了(EOM)ビットと確認応答(ACK)ビットが送信されます。

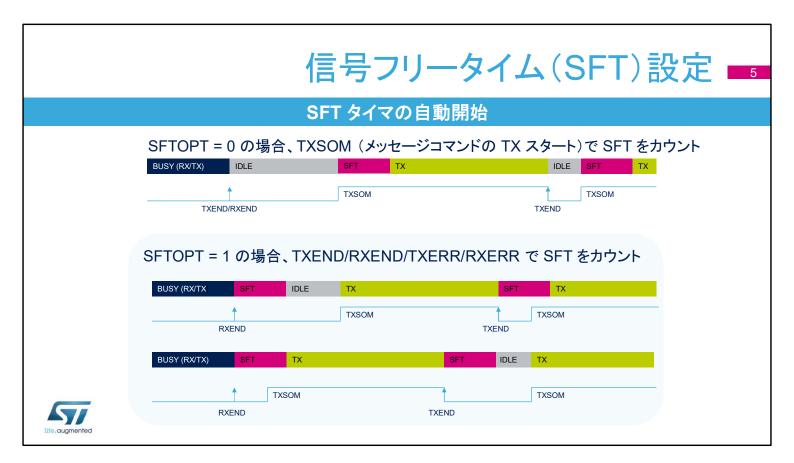

送信コマンドが送られると、HDMI-CEC は、プログラムされた信号フリータイム(SFT)値に依存する非アクティブの公称データビット周期数が経過した後にスタートビットを送信します。 SFT=0x0 設定では、HDMI-CEC コントローラが SFT 値を自動的に計算し、HDMI-CEC 規格への準拠を保証します。また、さまざまな固定値に設定することもできます。

SFTOPT ビットが "0" にセットされている場合、送信開始コマンドがソフトウェアによりセットされる(TXSOM ビットが "1" にセットされる)と、HDMI-CEC コントローラは SFT 値のカウントを開始します。

SFTOPT ビットが "1" にセットされている場合、バスアイドル条件またはラインエラー条件が検出されると、HDMI-CEC コントローラは SFT 値のカウントを開始します。TXSOM ビットが "1" に設定されている場合、SFT タイマが完了すると遅延なく直ちに送信が開始されます。

## RX 許容誤差マージン

#### RxTol ビット

- 標準許容誤差(CEC 仕様に準拠)

- スタートビット: ±200ms 立ち上がりと立ち下がり

- データビット: ±200ms 立ち上がり、±350ms 立ち下がり

- ・ 拡張された許容誤差

- スタートビット: ±400ms 立ち下がりと立ち下がり

- データビット: ±300ms 立ち上がり、±500ms 立ち下がり

HDMI-CEC コントローラは、2 つの RX 許容誤差マージンモードをサポートします。

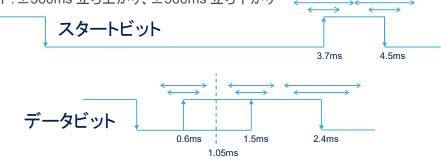

1番目の CEC 仕様に準拠した標準許容誤差モードは、スタート ビットの立ち上がりと立ち下がり時間で ±200µs、データビットの 立ち上がりエッジで ±200µs、データビットの立ち下がりエッジで ±350µs です。

2番目のモードは拡張された許容誤差モードです。このモードでは、立ち上がりと立ち下がり遷移のスタートビットのタイミングが ± 400µs、データビットの立ち上がりエッジで ±300µs、データビットの立ち下がりエッジで ±500µs に拡張されます。

## エラー処理

- エラーは、立ち下がりエッジ間の周期が最小のデータビット周期よりも短い場合(つまり、有効なビットとしては短すぎる場合)に定義されます。その他のタイミングエラーは CEC 仕様の対象外です ユーザがアクションを定義します。

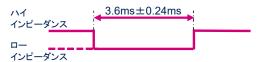

- エラー通知(エラービット)は、CEC ラインにおいて公称データビット周期(公称値で 3.6ms)の 1.4 倍から 1.6 倍の長さで続くローインピーダンスの周期です。

- メッセージは喪失したものとみなされ、以下の条件により再送信することができます。

- メッセージは、直接アドレス指定されたメッセージでは確認応答されません。

- メッセージは、ブロードキャストメッセージでは否定応答されます。

- CEC ライン上で予期しないローインピーダンスが検出されました(ラインエラー)。

受信データビット(スタートビットを除く)は、次の場合に無効と見なされます。

- 立ち上がりエッジと立ち下がりエッジの間の周期が、HDMI-CEC 仕様で定義されている許容誤差マージンを超えている。この場合、 ビットタイミングエラー(BTE)が発行されます。

- 立ち下がりエッジの間の周期が、HDMI-CEC 仕様で定義されている許容誤差マージンを超えている。この場合、ビット周期エラー (BPE)が発行されます。

BTE エラーまたは BPE エラーが検出された場合、CEC ペリフェラルは、エラービットを生成して他のフォロワおよび主にイニシエータに通知します。エラービットは、CEC ラインにおいて公称データビット周期(公称 3.6ms)の 1.4 倍から 1.6 倍の長さで続くローインピーダンスの周期です。

メッセージは喪失したものとみなされ、以下の条件により再送信することができます。

- メッセージは、直接アドレス指定されたメッセージでは確認応答されません。

- メッセージは、ブロードキャストメッセージでは否定応答されます。

- CEC ライン上で予期しないローインピーダンスが検出されました (ラインエラー)。

#### ビットタイミングエラー検出 データビット 0.6ms 2.4ms 1.5ms 1.05ms 立ち上がり 0.0 "0" RxTol = 0"1" RxTol = 1 BRE BRE "1" "0" 立ち下がり <del>・</del> 0.0 0.3 0.4 RxToI = 0SBPE RxTol = 1 LBPE

- BRE:Bit Rising Error(ビット立ち上がりエラー)

- SBPE: Short Bit Period Error(ショートビット周期エラー)

- ・ LBPE:Long Bit Period(ロングピット周期)

このスライドでは、メッセージ受信時のさまざまなビットタイミングエ ラーについて説明します。

- ビット立ち上がりエラー(BRE)は、RxTol で設定された Rx ウィンドウの外のデータビット内で立ち上がりエッジが検出されたときにハードウェアによって設定されます。BRE の検出時にビットBRESTP が "1" の場合、CEC メッセージの受信はオプションで中止され、ビット BREGEN が "1" の場合、CEC ラインでエラービットがオプションで生成されます。

- ショートビット周期エラー(SBPE)は、RxTol マージンによる予想よりも前にデータビットを終了する立ち下がりエッジが検出されるとと、ハードウェアによって設定されます。SBPE が検出されるとCEC ラインでエラービットが常に生成され、受信が中止されます。CEC ラインが再びアイドルになると、CEC は次のスタートビットの待機を開始します。

- ロングビット周期エラー(LPBE)は、最大 RxTol マージンの後に 立ち上がりエッジまたは立ち下がりエッジが検出されたときに ハードウェアによって設定されます。LBPE 検出メッセージにより、 LPBPEGEN が "1" に設定されている場合、受信は常に中止され、CEC ラインでエラービットがオプションで生成されます。

# HDMI-CEC 割込み(1/2) 🗾

| 割込みイベント | 説明              |

|---------|-----------------|

| RXBR    | Rx バイト受信        |

| RXEND   | 受信終了            |

| RXOVR   | Rx オーバーラン       |

| BRE     | Rx ビット立ち上がりエラー  |

| SBPE    | Rx ショートビット周期エラー |

| LBPE    | Rx ロングビット周期エラー  |

| RXACKE  | Rx 確認応答喪失エラー    |

ここでは、HDMI-CEC の受信割込みイベントの概要を示します。 受信ブロック転送が完了したか、または受信エラーが発生した場 合、受信中に割込みが生成されます。

# HDMI-CEC 割込み(2/2) 1010

| 割込みイベント | 説明            |

|---------|---------------|

| ARBLST  | アービトレーション喪失   |

| TXBR    | Tx バイトリクエスト   |

| TXEND   | 送信終了          |

| TXUDR   | Tx バッファアンダーラン |

| TXERR   | Tx エラー        |

| TXACKE  | Tx 確認応答喪失エラー  |

ここでは、HDMI-CEC の送信割込みイベントの概要を示します。 送信ブロック転送が完了するか、または送信エラーが発生した場 合、送信中に割込みが生成されます。

## 低電力モード 💶

| システムモード                              | 説明                                                                               |

|--------------------------------------|----------------------------------------------------------------------------------|

| RUN                                  | アクティブ                                                                            |

| SLEEP (MPU または<br>MCU がサブシステム<br>状態) | アクティブ                                                                            |

| STOP + LP-STOP                       | ペリフェラルはアクティブではありませんが、HDMI-CEC コントローラからの v により、デバイスはデータ受信時に STOP モードからウェイクアップします。 |

| LPLV-STOP                            | 非アクティブ。ペリフェラルレジスタの内容は保持されます。                                                     |

| STANDBY                              | ペリフェラルはパワーダウンされ、STANDBY モード終了後に再初期化する必要があります。                                    |

HDMI-CEC ペリフェラルは、RUN モードおよび SLEEP モード でアクティブとなります。

STOP モードではアクティブではありませんが、このペリフェラル には CPU クロックとは独立したクロックドメインがあるため、 HDMI-CEC コントローラからの割込みにより、データ受信時にデ バイスは STOP モードからウェイクアップします。

STANDBY モードでは、ペリフェラルはパワーダウン状態であり、 STANDBY を終了した後に再初期化する必要があります。

## 関連ペリフェラル 12

- ・以下は、HDMI-CEC コントローラに関連するペリフェラルのリストです。詳細については、必要時にこれらのトレーニングを参照してください。

- リセットおよびクロック制御(RCC)

- 割込み(NVIC)

- · 汎用入力/出力(GPIO)

これは、HDMI-CEC モジュールに関連するペリフェラルのリストです。ユーザは、HDMI-CEC インタフェースを正しく構成して使用するために、これらのペリフェラル間のすべての関係を良く理解する必要があります。