STM32 汎用 I/O インタフェースのプレゼンテーションにようこそ。 汎用入出力インタフェースと、それが STM32 マイクロコントローラの周辺環境に対するコネクティビティを可能とする方法の説明を行います。

- 外部環境との相互作用に対するインタフェースを提供

- 完全に設定可能

- 割込みとウェイクアップの機能

- AHB2 ブリッジに直接接続

### アプリケーション側の利点

- マイクロコントローラを直接ウェイクアップ

- 広範囲な電源電圧に対応

- AHB2 への直接接続により高速なトグル反応が可能

STM32 製品の汎用 I/O ピンは、外部環境とのインタフェースを提供します。この設定可能なインタフェースは、MCU とその他すべての搭載ペリフェラルによって、デジタルとアナログの両方の信号を用いたインタフェースに使用されます。

アプリケーション側の利点の中には、広範囲な I/O 電源電圧対応や、MCU を低電力モードから外部的にウェイクアップ可能であることなどが含まれます。

- 最大 72\* 本の I/O ピンの双方向動作

- GPIOA~GPIOE および GPIOH という名称の 6 つのGPIOx ポートで共有され、ポート当たりの I/O ピンは最大 16 本

- すべて外部割り込みとウェイクアップの機能に対応

- BSRR レジスタと BRR レジスタを用いたビット単位のセット/リセット操作

- 各 I/O ピンを独立に設定可能

- リセット後の I/O ピンはアナログモード

- GPIO レジスタインタフェースは AHB2 バスに直接接続

- ほとんどの I/O ピンは、V<sub>DD</sub> が 1.62V 以上であれば 5V 耐圧

- 独立したI/O 電源

- V<sub>DDUSB</sub> ドメインにおいて最大 3\* 本の I/O ピン

\*:製品型番とパッケージによります

汎用 I/O ポートは、入力メモリマップに従った双方向動作を行います。

I/O ポートは AHB2 バスに直接接続されています。そのため、それぞれの I/O ピン は独立に設定可能であり、トグルや出力など、I/O ピンの高速動作が可能です。GPIOA~GPIOE およびGPIOH という名称の 6ポートに共有されており、それぞれのポートに最大 16 本の I/O ピンがあります。リセット後には、消費電力を低減するために、すべての GPIO がアナログモードにセットされます。

I/O ポートは、BSSRR レジスタと BRR レジスタを用いたビット単位のセット/リセット操作に対応しています。これにより、2クロックサイクルごとに I/O トグルが可能です。

ほとんどの I/O ピンは、VDD 電源が 1.62V 以上であれば 5V 耐圧です。

VDDUSB 電圧ドメインは最大 3 本の I/O ピンより外部電圧供給されます。この電源は、MCU に供給される VDD から独立しています。ユーザは、この機能を用いて、MCU の I/O ピンのロジックレベルを、異なる電源ドメインから供給されている可能性のある外部ロジックに必要なレベルに、外部レベルシフタの必要なしに適応させることが可能です。

#### 柔軟性の高い動作モードによりアプリケーションのニーズに最適対応

- 入力モード

- フローティング(プルアップ/ダウン抵抗なし)、プルアップ/ダウン付き入力、アナログ入力モード

- ・出力モード

- プルアップ/ダウンオプション付きのプッシュプルモードとオープンドレインモード

- 出力時のスルーレートを設定可能

- オルタネート機能モード(AF モード)

- I/O ポート設定を固定するロック機構(GPIOx\_LCKR)

汎用 I/O ピンは、いくつかの動作モードに設定可能です。

I/O ピンは、フローティング入力モード、内部プルアップ/プルダウン抵抗付きの入力モード、またはアナログ入力に設定可能です。

さらに、I/O ピンは、内部プルアップ/プルダウン抵抗付きのプッシュプル出力モード、またはオープンドレイン出力モードに設定することもできます。

最高速度と I/O スイッチングによるエミッションのバランスや、アプリケーションの EMI 性能を調整するために、それぞれの I/Oピンに対して、スルーレートは 4 種類の異なるレンジから選択可能です。

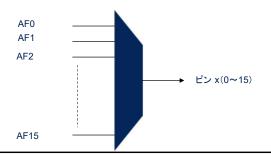

I/O ピンは、その他の搭載ペリフェラルが外部環境とインタフェースするためにも使用されます。オルタネート機能レジスタは、この場合のペリフェラルの設定選択に用いられます。

I/O ポートの設定をロックして、アプリケーションの堅牢性を向上することができます。一旦、ロックレジスタに正しい書込みシーケンスを適用して設定をロックすると、I/O ピンの設定は次のリセットまで修正できなくなります。

#### I/O ピンの構造はインタフェースとして他の搭載ペリフェラルから使用

- 複数の搭載ペリフェラルが同じ I/O ピンを共有

- USARTx TX、TIMx CHx、SPIx MISO、EVENTOUT など

- オルタネート機能(AF)マルチプレクサが I/O ピンに接続されるペリフェラルを選択

- ある特定の I/O ピンには、一度に 1 つのオルタネート機能のみ接続可能

- GPIOx AFRL レジスタと GPIOx AFRH レジスタにより設定可能

外部環境とのインタフェースのため、USART、タイマ、SPI など複数の内蔵ペリフェラルが同じ I/O ピンを共有します。 1本の I/O ピンに対して一度に接続されるペリフェラルは 1 つのみで、ペリフェラルはオルタネート機能マルチプレクサを通じて設定されます。また、この選択は、GPIOx\_AFRL レジスタとGPIOx\_AFRL レジスタを通じて、アプリケーションの動作中に変更可能です。

#### 独立した V<sub>DDUSB</sub> により複数電源環境を提供

- V<sub>DDUSB</sub> 電源ドメインは V<sub>DD</sub> から独立

- V<sub>DDUSB</sub> 電源ドメインのピンは、USB のように V<sub>DD</sub> 以外の電圧レールから電源供給を受けている他の回路との通信に使用可能

- 最大3本のI/Oピン

## アプリケーション側の利点

外部のレベルシフタの必要がなく、2種類の異なる電源供給/電源電圧を備えるアプリケーションに最適

独立した VDDUSB 電源ドメインによって、複数の異なるロジック電源電圧が存在する環境での動作が可能となります。これにより、STM32 は異なるロジック電源との通信が可能です。このドメインの最大 3 本の I/O ピンを用いて、USB など VDD 以外の電圧レールから電源供給を受けている他のロジック回路との通信が可能です。

独立した電圧の電源を使用することで、設計における外部電圧シフタの必要性がなくなります。

# I/Oピンに関する特筆事項

#### リセット時はデバッグピンのみがAFモードを維持

- リセット中とリセット後は、オルタネート機能は有効ではありません。

- I/O ポートのデフォルト状態は入力モード

- 消費電流を削減するため IO はアナログモードに設定可能

- AF プルアップ/プルダウン設定では、JTAG/SWD デバッグピンのみが有効に維持されます。

• PA13: JTMS/SWDIO

• PA14: JTCK/SWCLK

PA15:JTDIPB3:JTDO

• PB4:NJTRST

リセット中とリセット後は、オルタネート機能は有効ではありません。デバッグピンのみAF モードで有効を維持します。 AF 設定モードで維持される JTAG/SWD デバッグピンは、このスライドにリストアップされています。

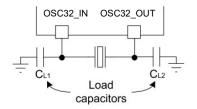

## LSE ピンに関する特筆事項

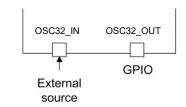

#### オシレータピンを標準 I/O ピンとして使用可能

- オシレータが OFF された場合、関連ピンは I/O ピンとして動作

- LSE に対して有効

- この状態がリセット後のデフォルト

- 外部クロックモードが使用される場合、2番目のピンは I/O ピンとして動作

- OSC32 IN のみクロックソースとして使用

- OSC32 OUT は標準 I/Oピン

外部オシレータが OFF の場合、このオシレータに関連するピン は標準 I/O ピンとして使用できます。これは、デバイスリセット後 のデフォルト状態となります。

水晶発振回路の代わりに外部クロックソースが使用されている 場合、OSC32 IN ピンのみがクロックに用いられ、

OSC32 OUT ピンは標準 I/O ピンとして使用できます。

STM32WB のハイスピードオシレータピンは、OSC IN と

OSC OUT の機能専用であり、標準 I/O 機能は備えていません。

#### 一部の I/O ピンは異なる電源から供給可能

- 新しい I/O ピン電源供給スキームにより、新規の I/O ピン構造と名称を導入

- TTとFTの定義は新規の略称サフィックスで拡張されます。

- 最大 V<sub>IN</sub> は、特定の I/O ピンの構造に接続された最小電源電圧によって定義されます。

- たとえば、FT a ピンに対しては、V<sub>IN</sub> < min (V<sub>DD</sub>, V<sub>DDA</sub>) + 4.0V の式が適用されます。

| 略称サフィックス | 説明                            | 例          |

|----------|-------------------------------|------------|

| _f       | VDD から電源供給を受ける Fm+ 機能の I/O    | FT_f、FT_fa |

| ال       | VLCD から電源供給を受ける LCD 機能の I/O   | FT_I       |

| _a       | VDDA から電源供給を受けるアナログ機能 のI/O    | FT_a、TT_a  |

| _u       | VDDUSB から電源供給を受ける USB 機能の I/O | FT_u       |

I/O ピンの新しい複数電源供給スキームにより、新規の I/O ピン構造が導入されています。これまで使用されてきた FT および TT という名称は、FT と TT の各 I/O ピンに対する別電源を強調する略称サフィックスで拡張されています。

Fm+ 機能のピンに対してこれまで使用されてきた FTf という名称は FT\_f に変更されました。新規の \_I サフィックスが LCD 電源から供給を受けるピンの印として追加され、\_a サフィックスが アナログ電源から供給を受けるピンに、\_u サフィックスが USB電源から供給を受けるピンに、それぞれ用いられています。各 I/O ピンに対する絶対最大定格は、各 I/O ピンにリストアップされた電源の中の最小電圧によって定義されます。

# 低電力モード 📶

| モード       | I/O の説明                                          |  |

|-----------|--------------------------------------------------|--|

| RUN       | 有効。                                              |  |

| SLEEP     | 有効。                                              |  |

| 低電力 RUN   | 有効。                                              |  |

| 低電力 SLEEP | 有効。                                              |  |

| STOP 1    | 有効。                                              |  |

| STOP 2    | 有効。                                              |  |

| STANDBY   | 内部プルアップ、プルダウン、フローティングの入力としてのみ。                   |  |

| SHUTDOWN  | 内部プルアップ、プルダウン、フローティングの入力としてのみ。<br>終了すると設定が失われます。 |  |

| リセット      | MCU のリセット中は強制的にアナログ入力モードとなります。                   |  |

STANDBY と SHUTDOWN を除くすべてのモードで I/O ピンは有効に維持され、使用可能な設定は、内部プルアップ/プルダウン抵抗付きの入力とフローティング入力のみとなります。 SHUTDOWN モードを終了すると、I/O 設定は失われます。 MCU のリセット中には、I/O ピンは強制的にアナログ入力モードとなります。