こんにちは。STM32 Universal Synchronous/Asynchronous Receiver/Transmitter インタフェースのプレゼンテーションへようこそ。 ここでは、組込みシステムのシリアル通信に広く使用されている、この USART インタフェースの主な機能について説明します。

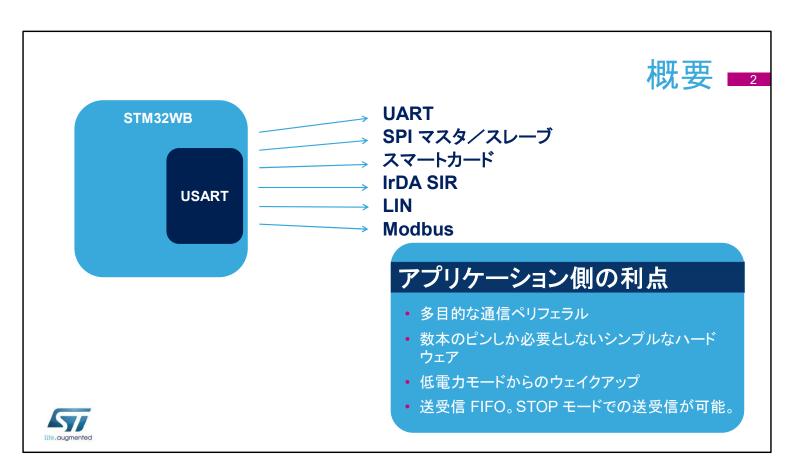

USART は非常に柔軟性の高いシリアルインタフェースであり、以下をサポートします。

- 非同期 UART 通信

- SPI(シリアルペリフェラルインタフェース)マスタモード

- LIN(ローカル相互接続ネットワーク)モード

また、ISO/IEC 7816 スマートカードおよび IrDA デバイスにも対応します。

Modbus 通信を実装する際に役立つ特定の機能も提供します。

USART を利用するアプリケーションは、少数のピンしか必要としない容易で安価なデバイス間の接続という利点を活用できます。

さらに、USART ペリフェラルは、低電力モードで機能します。 送受信 FIFO を備えているため、STOP モードでの送受信が 可能です。

- 完全にプログラム可能なシリアルインタフェース

- データは、7、8、または 9bit

- 偶数、奇数、パリティなし

- 0.5、1、1.5、および 2ストップビット

- データ順をプログラム可能(MSB ファースト/LSB ファースト)

- プログラム可能なボーレートジェネレータ

- 16 または 8 倍で設定可能なオーバーサンプリング方法

- データ送信および受信用の2つの内部 FIFO

- RS-232 および RS-485 ハードウェアフロー制御をサポート

- デュアルクロックドメイン可能:

- UART 機能と低電力モードからのウェイクアップ

- PCLK の変更から独立したボーレートプログラミング

USART は詳細にプログラム可能なシリアルインタフェースであ り、以下の設定可能なパラメータが特長です。

- データ長

- パリティ

- ストップビットの数

- データ順序

- ボーレートジェネレータ

- 8 または 16 倍で設定可能なオーバーサンプリングモード

USART は FIFO モードで動作でき、送信 FIFO と受信 FIFO を 備えています。

また、CTS(Clear To Send)信号とRTS(Request To Send)信 号を用いた基本的な RS-232 フロー制御を使用することもできま す。

RS-485 DE(Driver Enable)信号もサポートされます。

USART はデュアルクロックドメインをサポートするため、STOP モードからのウェイクアップと、ペリフェラルクロック(PCLK)に依 存しないボーレートプログラミングが可能です。

このため、通信を中断せずに、ペリフェラルクロックをコアクロック に合わせて減速できます。

### 主な機能(2/2) 4

- マルチプロセッサ通信

- 単線半二重通信

- 自動ボーレート検出

- レシーバタイムアウト機能

- 以下もサポート

- ・ LIN モード

- 同期モード(マスタモード)

- IrDA SIR エンコーダデコーダ

- スマートカード(ISO/IEC 7816 T=0 および T=1 プロトコル)

- Modbus/RTU および Modbus/ASCII プロトコルを実装するための基本

USART はマルチプロセッサモードが特長であり、これにより、 USART はアドレス指定されていないときにはアイドル状態 のままです。

全二重通信のほかに、単線半二重モードもサポートされます。 USART は、ほかにも、自動ボーレート検出、レシーバタイム アウトなど多くの機能を備え、いくつかのモードをサポートし ます。これらは、このプレゼンテーションで後述します。

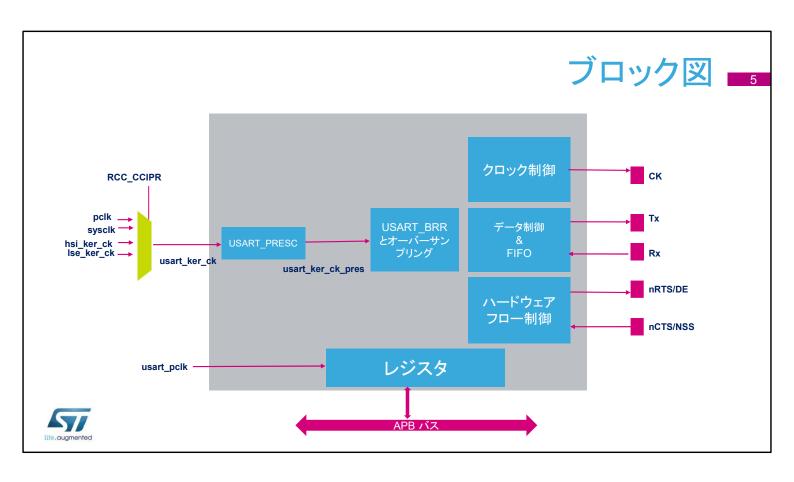

これは USART のブロック図です。

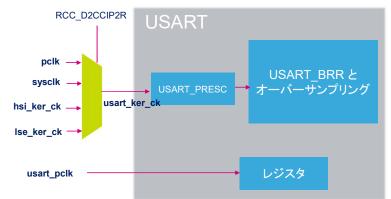

USART クロックソース(usart\_ker\_ck)は、いくつかのソースから選択できます。ペリフェラルクロック(APB クロック)、システムクロック、高速内部 RC オシレータ(HSI)、または低速外部オシレータ(LSE) USART クロックソースは、USART\_PRESC レジスタのプログラム可能な係数によって分周できます。

Tx および Rx ピンは、データ送信とデータ受信に使用されます。 nCTS および nRTS ピンは、RS-232 ハードウェアフロー制御に使用されます。

ドライバイネーブル(DE)ピンは、nRTS と同じ I/O で使用でき、RS-485 モードで使用されます。

スレーブ選択(NSS)ピンは同期スレーブモードで使用され、nCTSと同じ I/O で使用できます。

クロック出力(SK)には2つの目的があります。

- USART が同期マスタ/スレーブモードで使用されるとき、スレーブデバイスに供給されるクロックは、CKピンの出力/入力です。

- USART がスマートカードモードで使用されるとき、カードに供給されるクロックは、CK ピンの出力です。

### デュアルクロックドメイン

### PCLK の再プログラミングから独立したボーレートプログラミング

- 選択可能なクロックソースによる柔軟な クロッキング方式

- pclk クロック

- システムクロック

- · hsi ker ck

- lse\_ker\_ck

- レジスタへのアクセスは常に ペリフェラルのバス速度で。

USART は、柔軟なクロッキング方式を備えています。 クロックソースは RCC で選択でき、ペリフェラルクロック (APB クロック)、システムクロック、高速内部 RC オシレータ (HSI)、または低速外部オシレータ(LSE)から選択できます。 USART クロックソースは、USART PRESC レジスタのプロ グラム可能な係数によって分周できます。 レジスタは APB バスを介してアクセスされ、カーネルは APB クロックから独立した usart ker ck(プレスケールあり、また

はなし)でクロック供給されます。

### オーバーサンプリング

#### ユーザ設定可能なさまざまなオーバーサンプリング技法

オーバーサンプリングの選択は、速度とフレーミングトレランスに影響:

|    | 8 倍のオーバーサンプリング          | 16 倍のオーバーサンプリング               |

|----|-------------------------|-------------------------------|

| 利点 | 最大速度 usart_ker_ck/8 を達成 | クロック偏差に対する最大レシーバ耐性が増加。        |

| 欠点 | クロック偏差に対する最大レシーバ耐性が減少。  | 最大速度が usart_ker_ck/16 に制限される。 |

最大ボーレートは、選択されたクロックおよびオーバーサンプリングに 依存: クロックソースが 64MHz、オーバーサンプリングが 8 倍で設定 されたとき、8Mbaud。

USART レシーバは、有効な着信データとノイズを区別すること によってデータを復元する、ユーザ設定可能なさまざまなオー バーサンプリング技法を実装しています。

これにより、最大通信速度とノイズ/クロック精度の耐性の間で トレードオフができます。

8 倍のオーバーサンプリングを選択すると、より高い速度(最大 で usart\_ker\_ck\_pres/8)を達成できます。ここで、

usart ker ck pres は USART クロックソース周波数です。この 場合、クロック偏差に対するレシーバの最大トレランスは減少し ます。

16 倍のオーバーサンプリングを選択すると(OVER8 = 0)、ク ロック偏差に対するレシーバの許容誤差が増加します。この場合、 最大速度は usart ker ck pres/16 に制限されます。

クロックソースが 100MHz で、8 倍のオーバーサンプリングが設 定されているとき、達成できる最大ボーレートは 12.5Mbaudです。 他のクロックソースで、より高いオーバーサンプリング比の場合、 最大速度が制限されます。

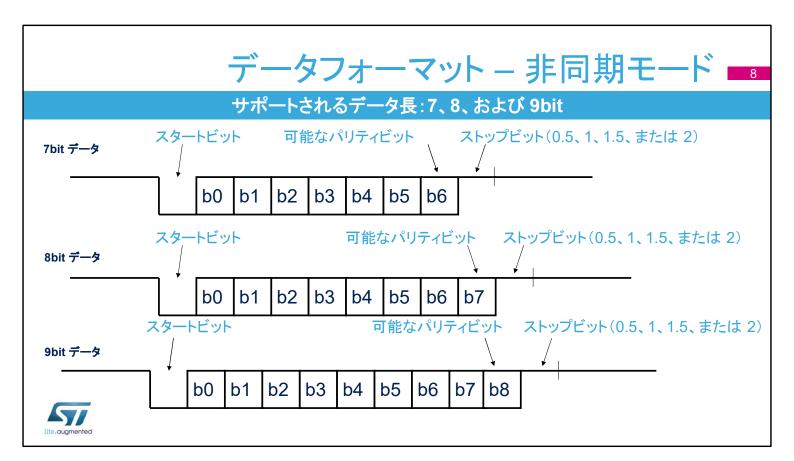

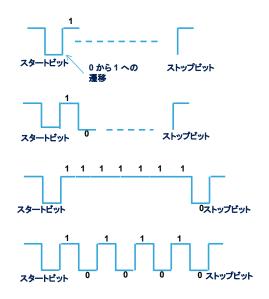

非同期モードで使用されるフレームフォーマットは、一連のデータビットと、同期のためのビットに加えて、オプションでエラーチェックのためのパリティビットで構成されます。 USART は、7、8、または 9bit データ長をサポートします。フレームは 1bit のスタートビットで始まり、ラインは 1bit 周期だけローに駆動されます。これがフレームの開始を通知し、同期のために使用されます。

スタートビットの後に、7、8、または 9bit のデータビットが続きます。パリティ制御が有効な場合、パリティビットは最後のデータビットとして送信され、データ長カウントに含まれます。 最後に、いくつかのストップビット(0、1、1.5、または 2)があり、ラインはハイに駆動され、フレームを終了します。

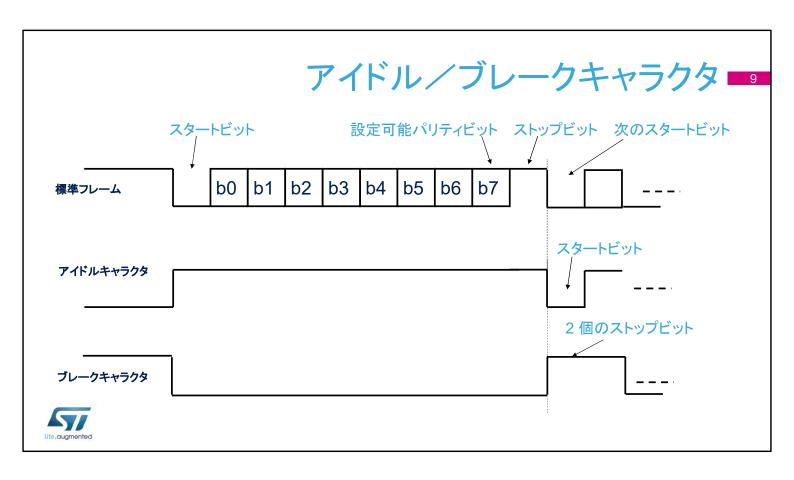

標準のフレームは、前のスライドで説明しました。 このスライドは、1bit のストップビットとともに構成された 8bit のデータフレームの例を示しています。 アイドルキャラクタは、すべてが「1」のフレームとして解釈されます(「1」の数にはストップビットの数が含まれます)。 ブレークキャラクタは、フレーム周期中に「0」を受信することと解釈されます。ブレークフレームの終わりに、2 個の ストップビットが挿入されます。

### 全二重/半二重モード

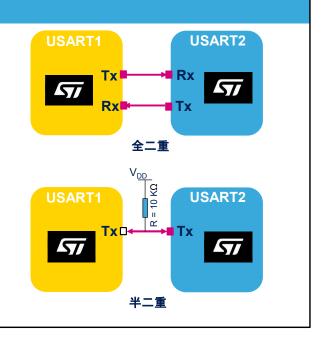

全二重:二線半二重:単線

- USART 全二重通信:

- Tx および Rx ラインが他方のインタフェースの Rx および Tx ラインとそれぞれ接続されます。

- USART 単線半二重プロトコル

- Tx ラインと Rx ラインが内部接続されます。

- Tx ピンは、送信と受信の両方に使用されます。

USART は全二重通信をサポートしています。Tx および Rx ラインが他方のインタフェースの Rx および Tx ラインとそれ ぞれ接続されます。

USART は、単線半二重のプロトコルに従うように設定できます。この場合、Tx ラインと Rx ラインは内部接続されます。この通信モードでは、Tx ピンだけが送信と受信の両方に使用されます。

Tx ピンはデータが送信されないときには常にリリースされるため、アイドルまたは受信モードでの標準 I/O として機能します。

つまり、Tx ピンが外部プルアップ付きの代替機能オープンドレインとして設定されるように、I/O を設定する必要があります。

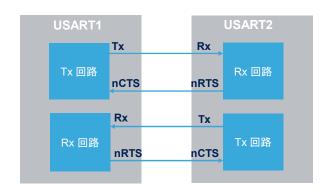

### データアンダーラン/オーバーランを避けるためのハードウェアハンドシェイク

- RS-232 ハードウェアフロー制御

- nRTS(Request to Send) 出力のアサートは、レシーバがデータを受け入れる準備ができたことを意味します。

- nCTS(Clear to Send) 入力のアサートは、 トランスミッタが通信を続行できることを意味します。

- 特に半二重システムで有用です。

RS-232 通信では、nCTS 入力と nRTS 出力を使用することによって、2 つのデバイス間のシリアルデータフローを制御できます。この 2 つのラインにより、レシーバとトランスミッタは互いに状態をアラートできます。次の図は、このモードで 2 つのデバイスを接続する方法を示しています。このアイデアは、半二重通信の場合のドロップバイトまたは競合を防止します。両方の信号がアクティブローです。

### RS-485 ハードウェアフロー制御 I

#### ハードウェアハンドシェイク

- マスタが方向信号を生成してトランシーバ(物理層(PHY))を制御する必要がある 半二重システムで有用です。この信号は PHY に送信または受信モードで動作し なければならないかどうかを通知します。

- DE(Driver Enable)ピンを使用して、外部 RS-485 バスドライバを有効化します。

- DE および nRTS 信号は、同じピンで使用できます。

RS-485 のようなシリアル半二重通信プロトコルでは、マスタは方向信号を生成してトランシーバ(物理層)を制御する必要があります。この信号は物理層に送信または受信モードで動作しなければならないかどうかを通知します。

RS-485 モードでは制御ラインが使用されます。外部トランシーバ制御を有効にするために、ドライバイネーブル(Driver Enable)ピンが使用されます。DE は nRTS とピンを共有します。

#### 複数のデバイス間の通信

- マルチプロセッサ通信では、目的のメッセージ受信者だけがメッセージを 積極的に受信することが望ましいです。

- アドレス指定されていないデバイスはミュートモードになります。

- ミュートモードを制御するには2つの方法があります。

- アイドルライン検出

- アドレスマーク検出

複数のプロセッサ間の通信を単純化するために、USART は マルチプロセッサモードをサポートします。

マルチプロセッサ通信では、目的のメッセージ受信者だけが メッセージを積極的に受信することが望ましいです。

アドレス指定されていないデバイスはミュートモードになりま す。

USART がミュートモードに入退出するには、2 つの方法の いずれかを使用します。

- アイドルライン検出

- アドレスマーク検出

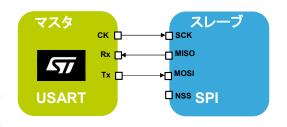

#### SPI マスタ/スレーブとして使用される USART

- 全二重またはシンプレックス同期通信モード:

- SPI マスタ/スレーブモード

- プログラム可能なクロックの極性(CPOL)と位相(CPHA)

- データ順をプログラム可能 (MSB ファースト/LSB ファースト)

- CK ピンでのクロック出力/入力。

- スタートビットとストップビット間にクロックパルスなし

- 送信アンダーランエラー(SPI スレーブモードのみ)。

- NSS 管理(ソフトウェアまたはハードウェア管理)(SPI スレーブモードのみ)

USART は同期通信も行うことができます。

SPI としてマスタまたはスレーブモードで動作でき、プログラム可能なクロック極性(CPOL)および位相(CPHA)と、プログラム可能なデータ順(MSB または LSB ファースト)を備えています。

クロックは CK ピンで出力(マスタモードの場合)または入力 (スレーブモードの場合)されます。スタートビットとストップ ビット間には、クロックパルスは供給されません。

USART が SPI スレーブモードで設定されているときには、 送信アンダーランエラーと NSS ハードウェアまたはソフトウェ ア管理をサポートします。

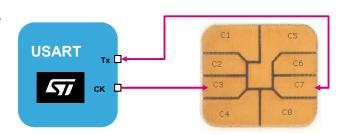

### ISO/IEC 7816 モード

#### スマートカードとセキュリティアクセスモジュール用の USART インタフェース

- 半二重モード

- スマートカードへのクロック供給は CK ピン

- プログラム可能なクロックプリスケーラにより、幅広いクロック入力を保証

- ISO/IEC 7816 T=0 および T=1 プロトコル をサポート

- ダイレクトとインバースの両方のコンベンションを使用可能

USART は、半二重通信に基づき、スマートカードモードで使用できます。

クロックは CK ピンよりスマートカードに出力されます。 T=0 プロトコルをサポートし、多くの機能を備えているため、 T=1 のサポートも可能です。

ダイレクトとインバースの両方のコンベンションがハードウェアによって直接サポートされます。

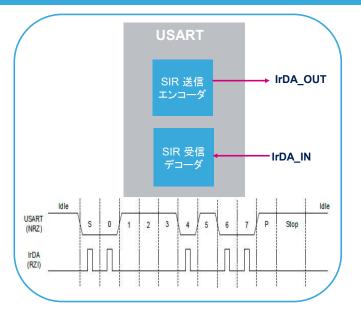

## IrDA SIR エンコーダデコーダ

#### 赤外線ワイヤレス接続用の USART インタフェース

- 半二重通信

- USART とやり取りされるデータは NRZ (Non Return to Zero)フォーマットで表現されます。

- IrDA の場合、必要なフォーマットは RZI (Return to Zero Inverted)。

- SIR Tx エンコーダは信号が USART を出る前に変調します。同様に、入力信号は SIR Rx デコーダで復調されます。

- 最大ビットレートは 115.2Kbits/s

- パルス幅は、通常モードで 3/16bit 周期

USART は、半二重通信プロトコルである IrDA 仕様をサポートします。

USART とやり取りされるデータは NRZ(Non Return to Zero)フォーマットで表され、信号値はビット周期全体を通じて同じレベルです。 IrDA の場合、必要なフォーマットは RZI (Return to Zero Inverted)であり、「1」はラインをローに保持することによって通知され、「0」は短いハイパルスによって通知されます。

SIR 送信エンコーダは、USART から出力される NRZ(Non Return to Zero)送信ビットストリームを変調します。SIR 受信デコーダは、赤外線検出回路からの RZ(Return to Zero)ビットストリームを復調し、受信した NRZ シリアルビットストリームを USART に出力します。

USART は、SIR ENDECについて、最大 115.2Kbits/s のビットレートのみをサポートします。

通常モードでは、送信されるパルス幅は、ビット周期の 3/16 として指定されます。

#### 自動ボーレート設定 - USART レシーバ

- USART は、1 キャラクタの受信に基づいて、ボーレートを自動的に判断可能

- 受信されるキャラクタは、次のいずれか:

- 「1」のビットで始まるキャラクタ

- 10xx パターンで始まるキャラクタ

- 0x7F

- 0x55

USART レシーバは、1 キャラクタの受信に基づいて、ボーレートを検出し、自動的に設定することができます。

受信されるキャラクタは、次のいずれかです。

- 1 のビットで始まるキャラクタ。この場合、USART はスタート ビットの時間を測定します(立ち下がりエッジから立ち上がり エッジまで)。

- 10xx パターンで始まるキャラクタ。この場合、USART はスタートビットと最初のデータビットの時間を測定します。低速な信号傾斜の場合の精度を高めるために、測定は立ち下がりエッジから立ち下がりエッジまでの時間で行われます。

- 0x7F キャラクタフレーム。この場合、ボーレートは、最初はスタートビットの終了時に更新され、次にビット6の終了時に更新されます。

- 0x55 キャラクタフレーム。この場合、ボーレートは、最初はスタートビットの終了時に更新され、次にビット 0 の終了時に更新され、最後にビット 6 の終了時に更新されます。並行して、RX ラインの中間遷移ごとに別のチェックが行われます。

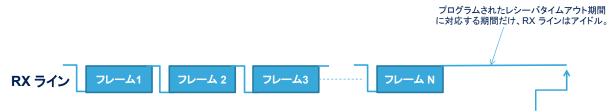

## レシーバタイムアウト 18

USART レシーバが、プログラムされた時間の間、新しいデータを受信しないとき、 これをレシーバタイムアウトイベントによってアプリケーションに通知できます。

USART レシーバタイムアウトカウンタは、 次の時点からカウントを開始します。

通知される。

-バタイムアウトイベントが

- 1 および 1.5ストップビット設定の場合、最初のストップビットの終了から。

- 2ストップビット設定の場合、2番目のストップビットの終了から。

- 0.5ストップビット設定の場合、ストップビットの開始から。

USART はレシーバタイムアウト機能をサポートします。 USART が、プログラムされた時間の間、新しいデータを受信 しないときには、レシーバタイムアウトイベントが通知され、有 効な場合、割込みが生成されます。

USART レシーバタイムアウトカウンタは、次の時点からカウントを開始します。

- 1 および 1.5ストップビット設定の場合、最初のストップビットの終了から。

- 2ストップビット設定の場合、2番目のストップビットの終了から。

- 0.5ストップビット設定の場合、ストップビットの開始から。

#### STOP モードでも送受信

- FIFO モードは、ソフトウェアによって有効/無効にされます。

- 送信 FIFO(TXFIFO)と受信 FIFO(RXFIFO)

- TXFIFO と RXFIFO のサイズは 16データビット

- FIFO モードは、IrDA および LIN モードでは使用できません。

- FIFO はカーネルクロックドメインにある → STOP モードでも送受信可能。

- TXFIFO と RXFIFO の閾値

USART は、ソフトウェアによって有効化/無効化される FIFO モードで動作できます。デフォルトでは無効です。 USART は送信 FIFO(TXFIFO)と受信 FIFO(RXFIFO)を 備え、それぞれ 16ワードの深さです。

IrDA および LIN モードが使用されるとき、FIFO モードはサポートされません。

TXFIFO と RXFIFO がカーネルクロックによってクロック供給される場合、STOP モードでもデータの送信と受信が可能です。

TXFIFO と RXFIFO の閾値を設定することができ、主に STOP モードからのウェイクアップ時のアンダーラン/オーバーラン問題を回避するために設定されます。

### STOP モードからのウェイクアップ ZO

- USART は、USART クロックソースが以下のとき、MCU を STOP モードからウェイクアップできます。

- HSI

- LSE

- ウェイクアップのソースは以下のいずれかです。

- 以下によってトリガされる特定のウェイクアップイベント

- スタートビット

- アドレス一致

- 受信データ

- FIFO 管理が無効なときの標準 RXNE 割込み

- FIFO 管理が有効なときのFIFO イベント割込み: RXFIFO フル、TXFIFO エンプティ、または RXFIFO/TXFIFO がプログラムされた閾値に達したとき。

USART は、USART クロックソースが HSI、LSE、または CSI クロックのとき、MCU を STOP モードからウェイクアップできます。

ウェイクアップのソースは以下のいずれかです。

- スタートビットまたはアドレス一致または受信データに よってトリガされる特定のウェイクアップイベント

- FIFO 管理が無効なときの RXNE 割込み

- FIFO 管理が有効なときのFIFO イベント割込み:

- 受信 FIFO フル割込み

- 送信 FIFO エンプティ割込み

- 受信 FIFO 閾値割込み

- o 送信 FIFO 閾値割込み

| 割込みイベント               | 説明                                                 |

|-----------------------|----------------------------------------------------|

| 送信データレジスタ<br>エンプティ    | 送信データレジスタが空のときにセットされます。                            |

| 送信完了                  | データ送信が完了し、データレジスタとシフトレジスタの両方が空のときにセットされます。         |

| стѕ                   | nCTS 入力がトグルしたときにセットされます。                           |

| 受信データレジスタ<br>ノットエンプティ | 受信データレジスタにデータがあるときにセットされます。                        |

| アイドルライン               | アイドルラインが検出されたときにセットされます。                           |

| キャラクター致               | 受信データがプログラムされたアドレスに一致したときにセットされます。                 |

| レシーバタイムアウト            | プログラムされたタイムアウトに等しい期間、Rx ラインでアクティビティがなかった時にセットされます。 |

### いくつかのイベントが割込みを提供できます。

- 送信データレジスタエンプティフラグは、送信データレジスタが空であり、書込み準備ができているときにセットされます。

- 送信完了フラグは、データ送信が完了し、データレジスタとシフトレジスタの両方が空のときにセットされます。

- CTS フラグは、nCTS 入力がトグルしたときにセットされます。

- 受信データレジスタノットエンプティフラグは、受信データレジスタにデータがあり、読取り準備ができているときにセットされます。

- アイドルラインフラグは、アイドルラインが検出されたときにセットされます。

- キャラクター致フラグは、受信データがプログラムされた アドレスに一致したときにセットされます。

- レシーバライムアウトフラグは、Rx ラインで、プログラムされた期間、アクティビティがなかったときにセットされます。

| 割込みイベント                | 説明                            |

|------------------------|-------------------------------|

| ブロックの終了                | 完全なブロックが受信されたときにセットされます。      |

| STOP モードからのウェイク<br>アップ | ウェイクアップイベントが確認されたときにセットされます。  |

| LIN ブレーク               | LIN ブレークフレームが検出されたときにセットされます。 |

| 送信 FIFO ノットフル          | 送信 FIFO がフルでないときにセットされます。     |

| 送信 FIFO エンプティ          | 送信 FIFO が空のときにセットされます。        |

| 送信 FIFO 閾値             | プログラムされた閾値に達するとセットされます。       |

| 受信 FIFO ノットエンプティ       | 受信 FIFO が空でないときにセットされます。      |

| 受信 FIFO フル             | 受信 FIFO がフルのときにセットされます。       |

| 受信 FIFO 閾値             | プログラムされた閾値に達したときにセットされます。     |

ブロック終了フラグは、完全なブロックが受信されたときに セットされます。

STOP モードからのウェイクアップフラグは、ウェイクアップイ ベントが確認されたときにセットされます。

LIN ブレークフラグは、LIN ブレークフレームが検出されたと きにセットされます。

送信 FIFO ノットフルフラグは、送信 FIFO がフルでないとき にセットされます。

送信 FIFO エンプティフラグは、送信 FIFO が空のときにセッ トされます。

送信 FIFO 閾値フラグは、プログラムされた閾値に達したと きにセットされます。

受信 FIFO ノットエンプティフラグは、受信 FIFO が空でない ときにセットされます。

受信 FIFO フルフラグは、受信 FIFO がフルのときにセットさ れます。

受信 FIFO 閾値フラグは、プログラムされた閾値に達したと きにセットされます。

- DMA リクエストは以下によってトリガされます。

- FIFO 管理が無効なとき、送信データレジスタエンプティおよび受信データレジスタフル。

- FIFO 管理が有効なとき、送信 FIFO ノットフルおよび受信 FIFO ノットエンプティ。

DMA リクエストは、FIFO 管理が無効なときには、受信バッ ファノットエンプティまたは送信バッファエンプティフラグがセッ トされたときに生成されます。

DMA リクエストは、FIFO 管理が有効なときには、送信 FIFO ノットフルおよび受信 FIFO ノットエンプティフラグがセットされ たときにも生成されます。

| 割込みイベント    | 説明                                  |

|------------|-------------------------------------|

| オーバーランエラー  | オーバーランエラーが発生したときにセットされます。           |

| パリティエラー    | パリティエラーが発生したときにセットされます。             |

| フレーミングエラー  | フレーミングエラーが発生したときにセットされます。           |

| ノイズエラー     | 受信フレームでノイズが検出されたときにセットされます。         |

| 自動ボーレートエラー | ボーレート測定が失敗したときにセットされます。             |

| アンダーランエラー  | 同期スレーブモードでアンダーランエラーが発生したときにセットされます。 |

### いくつかのエラーフラグが生成されます。

- オーバーランエラーフラグは、オーバーランエラーが発生 したときにセットされます。

- パリティエラーフラグは、パリティエラーが発生したときに セットされます。

- フレーミングエラーフラグは、フレーミングエラーが発生し たときにセットされます。

- ノイズエラーフラグは、受信フレームでノイズが検出され たときにセットされます。

- 自動ボーレートエラーフラグは、ボーレート測定が失敗し たときにセットされます。

- アンダーランエラーフラグは、同期スレーブモードでアン ダーランエラーが発生したときにセットされます。

| モード              | 説明                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------|

| RUN/低電力 RUN      | アクティブ                                                                                                   |

| SLEEP/低電力 SLEEP  | アクティブ。ペリフェラル割込みによって、デバイスは SLEEP モードを終了します。                                                              |

| STOP 0 / STOP 1  | USART が STOP モードで使用可能なオシレータによってクロック供給されている場合、<br>USART は STOP モードで機能し、割込みによってデバイスは STOP モードから復帰<br>します。 |

| STOP 2           | 停止。ペリフェラルレジスタの内容は保たれます。                                                                                 |

| STANDBY/SHUTDOWN | パワーダウン状態です。STANBY または SHUTDOWN モード終了後にペリフェラル<br>を再初期化する必要があります。                                         |

USART ペリフェラルは、RUN および低電力 RUN、SLEEP および低電力 SLEEP モードでアクティブです。USART 割込 みによって、デバイスは SLEEP または低電力 SLEEP モー ドから復帰します。

USART が STOP モードで使用可能なオシレータによってク ロック供給されているとき、USART は MCU を STOP 0 また は STOP 1 モードからウェイクアップできます。STOP 2 モー ドでは、デバイスは通信を行うことができません。STANBY および SHUTDOWN モードでは、ペリフェラルはパワーダウ ン状態になり、STANBY または SHUTDOWN モードからの 復帰後に再初期化する必要があります。

# STM32WB USARTインスタンス機能 型

| USART の機能                        | USART1   |

|----------------------------------|----------|

| モデムのハードウェアフロー制御                  | х        |

| マルチプロセッサ通信                       | х        |

| 同期モード                            | х        |

| スマートカードモード                       | х        |

| 単線半二重通信                          | х        |

| IrDA SIR エンコーダ/デコーダ              | х        |

| LIN モード                          | х        |

| デュアルクロックドメインと STOP モードからのウェイクアップ | Х        |

| レシーバタイムアウト                       | х        |

| Modbus 通信                        | х        |

| 自動ボーレート検出                        | х        |

| ドライバイネーブル                        | х        |

| Tx/Rx FIFO                       | X(サイズ 8) |

STM32WB デバイスは、フル機能の USART インスタンスを 1つ内蔵します。

### 関連ペリフェラル 27

- 詳細については、このペリフェラルにリンクしている以下のトレーニングを参照してください。

- GPIO(オルタネート機能設定)

- リセットおよびクロックコントローラ(RCC)

- 電源コントローラ(PWR)

- 割込み(NVIC および EXTI)

- ダイレクトメモリアクセス(DMA)コントローラ

これは、USART に関連するペリフェラルのリストです。必要な場合、詳細については、これらのトレーニングを参照してください。

- 汎用入出力(GPIO)

- リセットおよびクロックコントローラ

- 電源コントローラ

- 割込みコントローラ

- ダイレクトメモリアクセスコントローラ