こんにちは。STM32 低電力ユニバーサル非同期レシーバ/トランスミッタインタフェースのプレゼンテーションへようこそ。ここでは、シリアル通信に広く使用されている、このインタフェースの主な機能について説明します。

#### 概要▮

- LPUART (Low Power Universal Asynchronous Receiver/Transmitter)

- 低速 32.768kHz の外部オシレータ(LSE)使用時、9600ボーでフル UART 通信。STOP モードからのウェイクアップ機能。

- 他のクロックソースでは、より高いボーレートも可能。

#### アプリケーション側の利点

- デバイス間の安価な通信リンク

- 数本のピンしか必要としないシンプルなハードウェア

- 低電力 のSTOP モードからウェイクアップ

- 送受信 FIFO。STOP モードでの送受信が可能。

低電力ユニバーサル非同期レシーバは、LPUART が低速の外部 32.768kHz オシレータ(LSE)を使用してクロック供給されているとき、9600ボーでのフル UART 通信を提供します。 LSE クロックとは別のクロックソースによってクロック供給すると、さらに高いボーレートを達成できます。

アプリケーションは、少数のピンしか必要としない容易で安価なデバイス間の接続を利用できます。さらに、LPUART ペリフェラルは、低電力モードで機能します。送受信 FIFO を備えているため、STOP モードでの送受信が可能です。

### 主な機能

3

- 完全にプログラム可能なシリアルインタフェース

- データは、7、8、または 9bit

- パリティ: 偶数、奇数、パリティなし

- ストップビット 1bit または 2bit

- データ順をプログラム可能(MSB ファースト/LSB ファースト)

- 送信と受信の信号極性をプログラム可能

- プログラム可能なボーレートジェネレータ

- ・ データ送信および受信用の 2 つの内部 FIFO

- RS-232 および RS-485 ハードウェアフロー制御をサポート

LPUART は完全にプログラム可能なシリアルインタフェースであり、データ長、自動的に生成およびチェックされるパリティ、ストップビットの数、データ順、送受信の信号極性、ボーレートジェネレータなどの機能を設定できます。

LPUART は FIFO モードで動作でき、送信 FIFO と受信 FIFO を備えています。

RS-232 および RS-485 ハードウェアフロー制御オプションを サポートします。

## 主な機能(続き)

- デュアルクロックドメイン設定可能:

- UART が STOP モードからのウェイクアップを駆動

- PCLK に依存しない便利なボーレートプログラミング

- マルチプロセッサ通信

- 単線半二重通信

LPUART はデュアルクロックドメインをサポートするため、 STOP モードからのウェイクアップと、ペリフェラルクロックに 依存しないボーレートプログラミングが可能です。 マルチプロセッサモードにより、LPUART はアドレス指定され ていないときにはアイドル状態のままです。 全二重通信のほかに、単線半二重モードもサポートします。

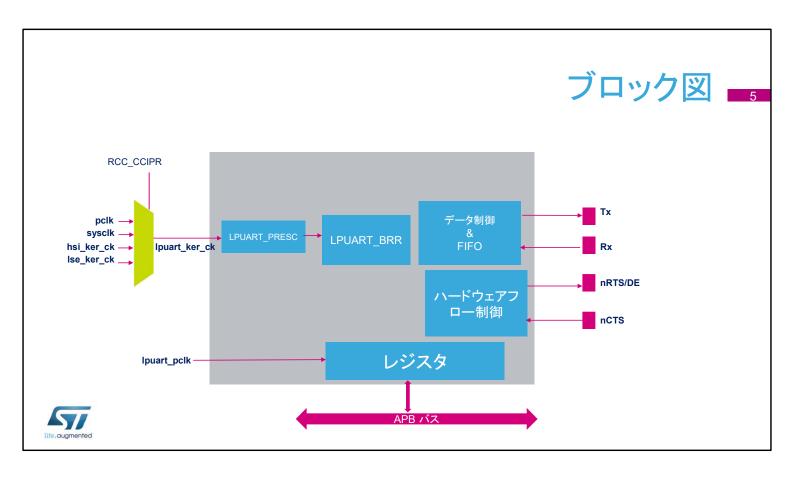

これは、LPUART のブロック図です。LPUART クロック (lpuart\_ker\_ck)は、ペリフェラルクロック(APB クロック)、システムクロック、高速内部 RC オシレータ(HSI16)、低速外部 32.768kHz クリスタルオシレータ(LSE)など、複数のソースから選択できます。

Tx および Rx ピンは、データ送信とデータ受信に使用されます。

nCTS および nRTS ピンは、RS-232 ハードウェアフロー制御に使用されます。

ドライバイネーブル(DE)信号は、nRTS と同じ I/O で使用でき、RS-485 モードで使用されます。

### デュアルクロックドメイン

#### PCLK 再プログラミングから独立したボーレートプログラミング

- 選択可能なクロックソースによる柔軟性の高いクロック制御スキーム

- pclk(デフォルト)

- システムクロック

- hsi ker ck

- lse\_ker\_ck

- レジスタへのアクセスは常にペリフェラルのバス速度

- 最大ボーレート:

- ・ Ipuart\_ker\_ck が LSE 32.768kHz のとき、9600 ボー

- Ipuart ker ck が 64MHz のとき、21Mボー

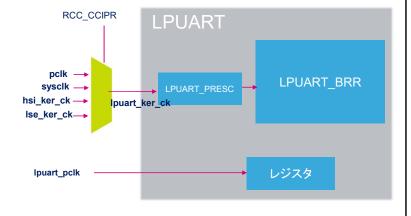

LPUART は、柔軟性の高いクロック制御スキームを備えています。

クロックソースは RCC で選択でき、ペリフェラルクロック (APB クロック)、システムクロック、高速内部 RC オシレータ (HSI16)、または低速外部 32.768kHz クリスタルオシレータ (LSE)から選択できます。

LPUART クロックソースは、LPUART\_PRESC レジスタのプログラム可能な係数によって分周できます。

レジスタは APB バスを介してアクセスされ、カーネルは APB クロックから独立した lpuart\_ker\_ck(分周設定可能)でクロック供給されます。

達成可能な最大ボーレートは、クロックソースが LSE のときには 9600ボー、クロックソースが 64MHz のときには 21Mボーです。

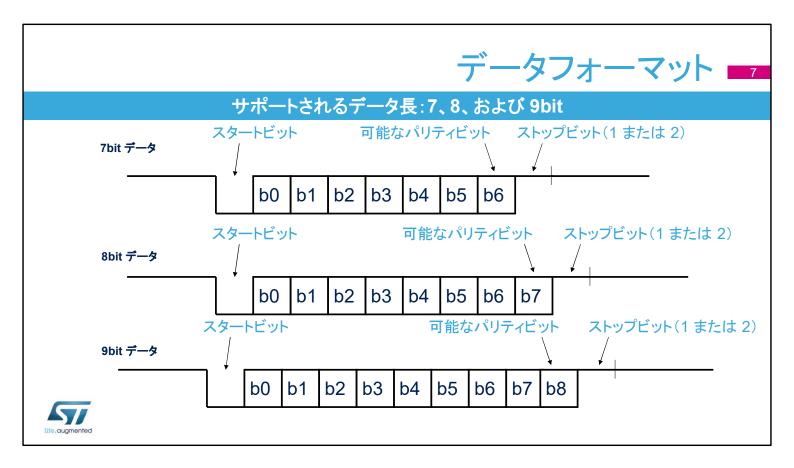

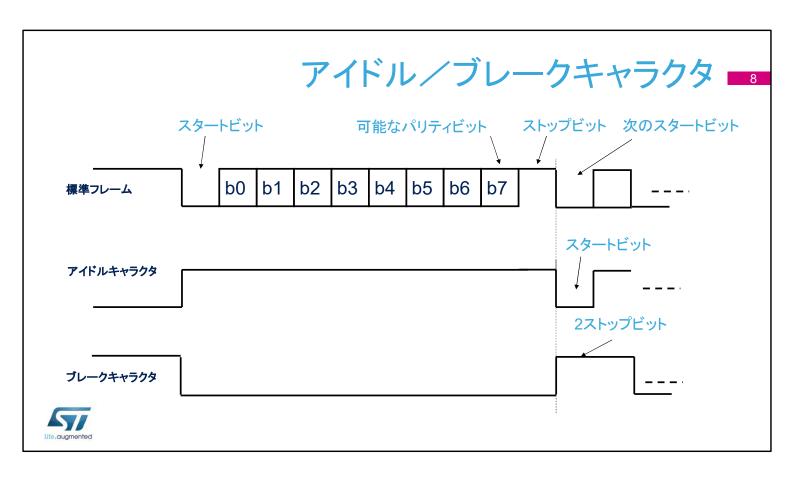

フレームフォーマットは、一連のデータビットと同期のための ビットに加えて、オプションでエラーチェックのためのパリティ ビットで構成されます。フレームはスタートビット 1bit(S)で始 まり、ラインは 1bit 周期だけローに駆動されます。これがフレームの開始を通知し、同期のために使用されます。 データ長は、パリティビットを含めた場合、9、8、または 7bit で設定できます。最後に、1 または 2bit のストップビットがあり、ここでラインはハイに駆動されて、フレームの終了を示します。

前のスライドでは、標準的なフレームを説明しました。このスライドは、1bit のストップビットで構成された 8bit データフレームの例を示しています。

アイドルキャラクタは、すべてが「1」のフレームとして解釈されます。「1」の数にはストップビットの数も含まれます。 ブレークキャラクタは、フレーム周期中、すべて「0」を受信することと解釈されます。ブレークフレームの終わりに、2ストップビットが挿入されます。

## 全二重/半二重モード

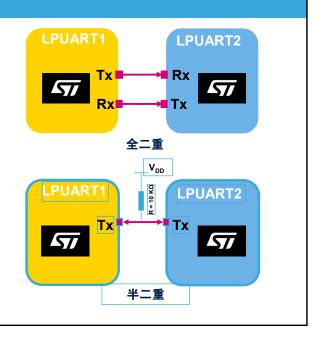

# 全二重:二線半二重:単線

- LPUART 全二重通信

- Tx および Rx ラインが他方のインタフェースの Rx および Tx ラインとそれぞれ接続。

- LPUART 単線半二重プロトコル

- Tx ラインと Rx ラインが内部接続。

- Tx ピンは、送信と受信の両方に使用。

LPUART は全二重通信をサポートしています。Tx および Rx ラインが他方のインタフェースの Rx および Tx ラインとそれぞれ接続されます。

LPUART は、単線半二重のプロトコルに従うように設定することもでき、Tx および Rx ラインは内部接続されます。この通信モードでは、Tx ピンだけが送信と受信の両方に使用されます。データが送信されないときには、Tx ピンは常に解放されます。したがって、アイドルまたは受信状態では、標準 I/Oとして機能します。この用途では、I/O は、代替機能のオープンドレインモードの Tx で、外部プルアップレジスタで設定する必要があります。

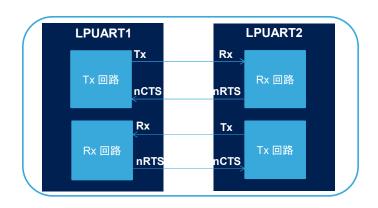

# RS-232 ハードウェアフロー制御

#### データアンダーラン/オーバーランを避けるためのハードウェアハンドシェイク

- RS-232 ハードウェアフロー制御

- nRTS(Request to Send)出力のアサートは、レシーバがデータを受け入れる準備ができたことを示す。

- nCTS(Clear to Send)入力のアサートは、 トランスミッタが通信を続行できることを示す。

- 特に半二重システムで有用。

RS-232 規格では、nCTS 入力と nRTS 出力を使用することによって、2 つのデバイス間のシリアルデータフローを制御できます。この 2 つのラインにより、レシーバとトランスミッタは互いに状態をアラートできます。このスライドは、このモードで2 つのデバイスを接続する方法を示しています。このアイデアは、半二重通信の場合の欠落またはデータの衝突を防止します。両方の信号がアクティブローです。

# RS-485 ハードウェアフロー制御 I

#### ハードウェアハンドシェイク

- マスタが方向信号を生成してトランシーバ(物理層(PHY))を制御する必要がある 半二重システムで有用です。この信号は物理層に送信または受信モードで動作し なければならないかどうかを通知。

- DE(Driver Enable)ピンを使用して、外部 RS-485 バスドライバを有効化。

- DE および nRTS 信号は、同じピンで使用可能。

RS-485 のようなシリアル半二重通信プロトコルでは、マスタは方向信号を生成してトランシーバ(物理層)を制御する必要があります。この信号は物理層に送信または受信モードで動作しなければならないかどうかを通知します。

RS-485 モードでは、外部トランシーバ制御を有効にするために、制御ライン「ドライバイネーブル」が使用されます。DE制御ラインは nRTS とピンを共有します。

#### 複数のデバイス間の通信

- マルチプロセッサ通信では、目的のメッセージ受信者だけがメッセージを積極的に 受信は禁止。

- アドレス指定されていないデバイスをミュートモードにすることが可能。

- ミュートモードを制御する2つの方法。

- アイドルライン検出

- アドレスマーク検出

複数のプロセッサ間の通信を単純化するために、LPUART は特殊なマルチプロセッサモードをサポートします。マルチプ ロセッサ通信では、目的のメッセージ受信者だけがメッセー ジを積極的に受信することが望ましいです。アドレス指定され ていないデバイスをミュートモードにするには、2 つの方法が あります。アイドルラインまたはアドレスマークです。 LPUART がミュートモードを有効または無効にするには、2 つの方法のいずれかを使用します。

- アイドルライン検出

- アドレスマーク検出

#### STOP モードでも送受信

- FIFO モードは、ソフトウェアによって有効/無効化が可能

- 送信 FIFO(TXFIFO)と受信 FIFO(RXFIFO)

- TXFIFO と RXFIFO のサイズは 16データビット

- FIFO はカーネルクロックドメインにある → STOP モードでも送受信可能

- TXFIFO と RXFIFO の閾値

LPUART は、ソフトウェアによって有効化/無効化される FIFO モードで動作できます。デフォルトでは無効です。 LPUART は送信 FIFO(TXFIFO)と受信 FIFO(RXFIFO)を 備え、それぞれ 16ワードの深さです。

TXFIFO は 9bit 幅です。RXFIFO のデフォルト幅は 12bit です。この理由は、レシーバは FIFO にデータを格納するだけでなく、各キャラクタに伴うエラーフラグ(パリティエラー、ノイズエラー、およびフレーミングエラーフラグ)も格納するためです。

TXFIFO と RXFIFO がカーネルクロックによってクロック供給される場合、STOP モードでもデータの送信と受信が可能です。

TXFIFO と RXFIFO の閾値を設定することができ、主に STOP モードからのウェイクアップ時のアンダーラン/オーバーラン問題を回避するために使用されます。

### STOP モードからのウェイクアップ 14

- LPUART は、LPUART クロックソースが以下のとき、MCU を STOP モードから ウェイクアップ可能

- 高速内部 RC オシレータ(HSI)

- 低速外部 32.768kHz クリスタルオシレータ(LSE)

- ウェイクアップのソースは以下のいずれか:

- 以下によってトリガされる特定のウェイクアップイベント

- スタートビット

- アドレス一致

- 受信データ

- FIFO 管理が無効なときの標準 RXNE 割込み

- FIFO 管理が有効なときのFIFO イベント割込み:RXFIFO フル、TXFIFO エンプティ、またはRXFIFO/TXFIFO がプログラムされた閾値に達したとき

LPUART は、LPUART クロックソースが HSI または LSE クロックのとき、MCU を STOP モードからウェイクアップできます。

ウェイクアップのソースは以下のいずれかです。

- スタートビットまたはアドレス一致または受信データに よってトリガされる特定のウェイクアップイベント

- FIFO 管理が無効なときの RXNE 割込み

- FIFO 管理が有効なときのFIFO イベント割込み

# 割込み 15

| 割込みイベント                | ·····································                      |  |

|------------------------|------------------------------------------------------------|--|

| 送信データレジスタエンプティ         | 送信データレジスタが空であり、書込み準備ができているときにセットされます。                      |  |

| 送信完了                   | データ送信が完了し、データレジスタとシフトレジスタの両方が空のときにセットされます。                 |  |

| стѕ                    | nCTS 入力がトグルしたときにセットされます。                                   |  |

| 受信データレジスタノットエン<br>プティ  | 受信データレジスタにデータがあり、読出し準備ができているときにセットされます。                    |  |

| アイドルライン                | アイドルラインが検出されたときにセットされます。                                   |  |

| キャラクター致                | 受信データがプログラムされたアドレスに一致したときにセットされます。                         |  |

| STOP モードからのウェイク<br>アップ | ウェイクアップイベント(スタートビットまたはアドレス一致または受信データ)が確認された<br>ときにセットされます。 |  |

この表は、割込みを生成する LPUART イベントを示していま す。

| 割込みイベント          | 説明                        |

|------------------|---------------------------|

| 送信 FIFO ノットフル    | 送信 FIFO がフルでないときにセットされます。 |

| 送信 FIFO エンプティ    | 送信 FIFO が空のときにセットされます。    |

| 送信 FIFO 閾値       | プログラムされた閾値に達するとセットされます。   |

| 受信 FIFO ノットエンプティ | 受信 FIFO が空でないときにセットされます。  |

| 受信 FIFO フル       | 受信 FIFO がフルのときにセットされます。   |

| 受信 FIFO 閾値       | プログラムされた閾値に達したときにセットされます。 |

この表は、FIFO 管理が有効なときの FIFO イベント割込み を示しています。

- DMA リクエストは以下によってトリガ

- FIFO 管理が無効なとき、送信データレジスタがエンプティおよび受信データレジスタがフル。

- FIFO 管理が有効なとき、送信 FIFO がフルでないおよび受信 FIFOがエンプティでない。

DMA リクエストは、FIFO 管理が無効なときには、受信バッ ファノットエンプティまたは送信バッファエンプティフラグがセッ トされたときに生成されます。

DMA リクエストは、FIFO 管理が有効なときには、送信 FIFO ノットフルおよび受信 FIFO ノットエンプティフラグがセットされ たときに生成されます。

# エラー割込み 18

| 割込みイベント   | 説明                                  |  |

|-----------|-------------------------------------|--|

| オーバーランエラー | オーバーランエラーが発生したときにセットされます。           |  |

| パリティエラー   | パリティエラーが発生したときにセットされます。             |  |

| フレーミングエラー | 同期外れまたは過剰ノイズが検出されたときにセットされます。       |  |

| ノイズエラー    | 受信フレームのスタートビットでノイズが検出されたときにセットされます。 |  |

いくつかのエラーフラグもまた、表に示されているように、 LPUART によって生成されます。

オーバーラン、パリティ、およびフレーミングエラーフラグは、 それぞれ対応するエラーが発生したときにセットされます。 ノイズエラーフラグは、受信フレームのスタートビットでノイズ が検出されたときにセットされます。

## 低電力モード 19

| モード                  | 説明                                                                                                |  |

|----------------------|---------------------------------------------------------------------------------------------------|--|

| RUN/低電力 RUN          | アクティブ。                                                                                            |  |

| SLEEP/低電力 SLEEP      | アクティブ。ペリフェラル割込みによって、デバイスは SLEEP モードを終了します。                                                        |  |

| STOP 0/STOP 1/STOP 2 | LPUART が STOP モードで使用可能なオシレータによってクロック供給されている場合、LPUART は STOP モードで機能し、割込みによってデバイスは STOP モードから復帰します。 |  |

| STANDBY/SHUTDOWN     | パワーダウン状態です。STANBY または SHUTDOWN モード終了後にペリフェラルを再初期化する必要があります。                                       |  |

LPUART ペリフェラルは、RUN モードでアクティブです。 LPUART 割込みによって、デバイスは SLEEP モードから復 帰します。

LPUART は、LPUART クロックが HSI または LSE クロック に設定されているとき、MCU を STOP モードからウェイク アップできます。

STANBY モードでは、ペリフェラルはパワーダウン状態にな り、STANBY または SHUTDOWN モードからの復帰後に再 初期化する必要があります。

## STM32WB LPUART の機能 20

| USART/LPUART の機能                     | USART    | LPUART   |

|--------------------------------------|----------|----------|

| モデムのハードウェアフロー制御                      | х        | х        |

| マルチプロセッサ通信                           | х        | х        |

| 同期モード                                | х        | -        |

| スマートカードモード                           | х        | -        |

| 単線半二重通信                              | х        | х        |

| IrDA SIR ENDEC                       | х        | -        |

| LIN モード                              | х        | -        |

| デュアルクロックドメインと STOP モードから<br>のウェイクアップ | х        | х        |

| レシーバタイムアウト                           | х        | -        |

| Modbus 通信                            | х        | -        |

| 自動ボーレート検出                            | х        | -        |

| ドライバイネーブル                            | х        | х        |

| Tx/Rx FIFO                           | x(サイズ 8) | x(サイズ 8) |

STM32WB デバイスは、1 つの LPUART インスタンスを内 蔵しています。USARTと比較して、LPUARTは同期、ス マートカード、IrDA、および LIN モードをサポートしません。レ シーバタイムアウト、modbus 通信、および自動ボーレート検 出機能もサポートしません。

### 関連ペリフェラル 型

- LPUART に関する以下のペリフェラルトレーニングを参照してください。

- GPIO(オルタネート機能設定)

- リセットおよびクロックコントローラ(RCC)

- 電源コントローラ(PWR)

- 割込み(NVIC および EXTI)

- ダイレクトメモリアクセス (DMA) コントローラ

これは、LPUART に関連するペリフェラルのリストです。必要な場合、詳細については、これらのペリフェラルトレーニングを参照してください。

- GPIO(General Purpose Input/Output、汎用入出力)

- リセットおよびクロックコントローラ

- 電源コントローラ

- 割込みコントローラ

- ダイレクトメモリアクセスコントローラ