# STM32WL5 - SYSCFG

システム設定コントローラ

レビジョン 1.0

システム設定コントローラのプレゼンテーションへようこそ。

### 概要

- すべての STM32WL5 デバイスは「システム設定コントローラ」を備えている

- ・ メモリ領域の再配置

- GPIO EXTI の多重化の管理

- 「堅牢性」機能の管理

- SRAM2 保護機能

- I2C 高速モードプラス設定

- 独立した CPU 割込みのプリマスキング

2

STM32WL5 デバイスは一組の設定レジスタを備えています。システム設定コントローラで利用できる機能として、Cortex-M4 アドレス 0 へのメモリ領域の再配置、内部相互接続 EXTI 信号へのGPIO の多重化、いくつかの堅牢性機能、SRAM2 の書込み保護と消去、I<sup>2</sup>C 高速モードプラスに使用する 20 mA 高駆動 I/Oの設定、2 つの CPU のペリフェラル割込みプリマスキングがあります。

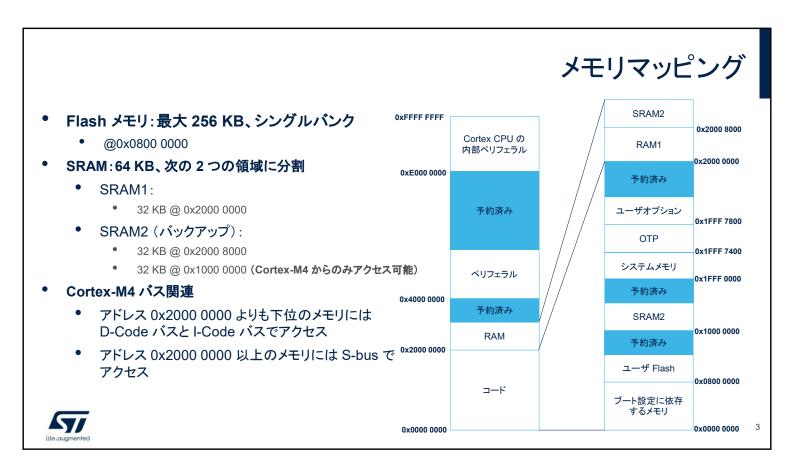

スライドの画像は、STM32WL5 マイクロコントローラの 4 GB リニア・アドレス・マッピングを示しています。

Flash メモリはシングルバンク設定で、最大 256 KB です。 SRAM の合計サイズは 64 KB であり、2 つの領域に分割されています。 SRAM1 は、アドレス 0x2000 0000 から始まる 32 KB です。 バックアップ RAM である SRAM2 は、アドレス 0x2000 8000 から始まる 32 KB であり、そのエイリアスが Cortex M4 のアドレス 0x1000 0000 に作成されます。 SRAM1 と SRAM2 はどちらも、S バス上で RAM 向けとした通常の ARM メモリ空間に配置されています。 SRAM2 には Cortex-M4 の D-Code バスと I-Code バスからも直接アクセスでき、ウェイトステートを伴わずにコードを実行できます。

### メモリの再配置

#### 性能の大幅な向上

- CPU1 Cortex-M4 アドレス 0x0000 0000 の再配置オプション(MEM MODE)

- メイン Flash メモリ

- システム Flash メモリ(ブートローダ)

- SRAM1

- システムバスではなく、I-Code バスと D-Code バスからアクセスすることによって性能が大幅に向上

4

CPU1 Cortex-M4 アドレス 0 でのメモリの再配置により、システムバスの代わりに命令バスとデータバスからアクセスすることで性能が大幅に向上します。

アドレス 0 でのメモリの再配置を選択するには、システム設定の再配置レジスタで MEM\_MODE ビットを使用します。これらのビットで、メイン Flash メモリ、システム Flash メモリ、またはSRAM1 を選択できます。

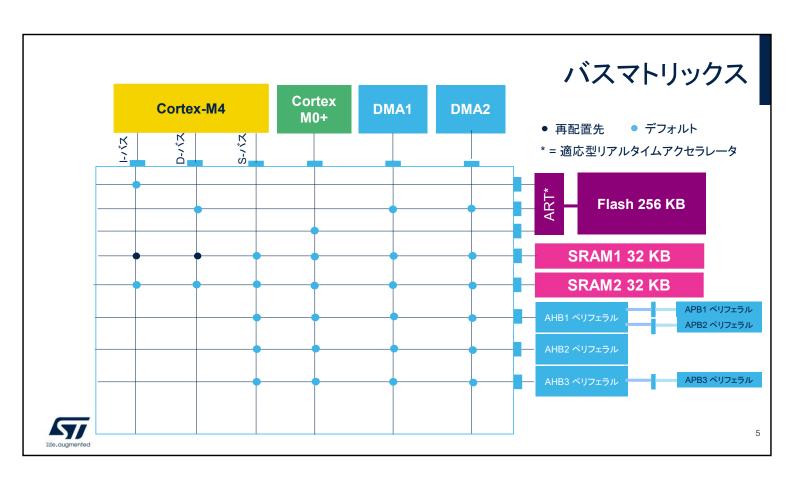

このスライドは、STM32WL5 のバスマトリックスを示しています。上部の Cortex-M4 コア、Cortex-M0+ コア、および 2 つの DMA コントローラはバ スマスタであり、丸印が表示された交点の右側に示されているバススレーブ と通信します。

Flash メモリの内容はアクセラレータ経由で読み出されます。Cortex-M4 の命令は命令バス経由でフェッチされ、リテラルプールはデータバス経由で読み出されます。SRAM1 には、デフォルトでシステムバスからアクセスしますが、アドレス 0 に再配置することで I-バスと D-バスからアクセスして性能の向上を図ることができます。この状態を濃い青色の丸印で示しています。SRAM2 には、I-バスと D-バス経由でアクセスして、ウェイトステートを伴わずにコードを実行できます。S-バス経由のアクセスも可能です。AHB1、AHB2、AHB3 の各ペリフェラルにも S-バスからアクセスできます。

Cortex-M0+ も、適応型リアルタイムアクセラレータ(ART)を介して Flash メモリを読み出し、SRAM1 と SRAM2 の両メモリおよび AHB1、AHB2、AHB3 の各共有ペリフェラルにアクセスできます。

2 つの DMA は、すべてのメモリとペリフェラルにアクセスできます。

複数のバスマスタがバスマトリックスを経由して複数のメモリとペリフェラルに同時にアクセスできるので、高性能な演算動作が実現します。複数のマスタから同一バスへの同時アクセスは、ラウンドロビン調停によって処理されます。

## Cortex-M4 のブートモード

• BOOT0 ピンまたは nBOOT0 オプション・ビットのどちらを使用するかは、nSWBOOT0 オプション・ビットで選択

|                          | ブート・モード選択                              |                              |                                                    |

|--------------------------|----------------------------------------|------------------------------|----------------------------------------------------|

| nBOOT1<br>(オプション<br>ビット) | BOOT0(ピン)<br>(または nBOOT0<br>オプション・ビット) | BOOT_LOCK<br>(オプション・<br>ビット) | CPU1 Cortex-M4 のブート・モード                            |

| 1                        | 0                                      | 0                            | ユーザ Flash メモリ                                      |

| 1                        | 1                                      | 0                            | システムメモリ(ブートローダ)                                    |

| 0                        | 1                                      | 0                            | SRAM1                                              |

| 0                        | 0                                      | 0                            | ホールド状態、Cortex-M4 はブートしない。<br>代わりに Cortex-M0+ をブート。 |

| х                        | x                                      | 1                            | ユーザ Flash メモリ                                      |

6

Cortex-M4 のブート・モードには、ユーザ Flash からのブート、システムメモリのブートローダからのブート、SRAM1 からのブートの 3 種類があります。このモードは、nBOOT0 オプション・ビットまたは BOOT0 ピン、nBOOT1 オプション・ビット、BOOT\_LOCK オプション・ビットで選択します。BOOT0、nBOOT1、BOOT\_LOCK の各オプション・ビットを 0 に設定すると、STM32WL5 によって Cortex-M4 がホールド状態になり、Cortex-M0+がブートします。STM32WL5 で標準的な方法では、ユーザ Flash から Cortex-M4 コアをブートします。この方法でブートするには、オプション・ビットの nBOOT1 を 1、BOOT0 と BOOT LOCK を 0 にそれぞれ設定します。

### Cortex-M0+ のブート・モード

- C2OPT オプションを使用すると、Cortex-M0+ のブート場所としてユーザ Flash または SRAM を選択可能

- BOOTO ピンまたは nBOOTO オプション・ビットのどちらを使用するかは、nSWBOOTO オプション・ビットで選択

| ブート・モード選択             |                                         |                          |                                         |

|-----------------------|-----------------------------------------|--------------------------|-----------------------------------------|

| nBOOT1<br>(オプション・ビット) | BOOT0 (ピン)<br>(または nBOOT0<br>オプション・ビット) | BOOT_LOCK<br>(オプション・ビット) | CPU2 Cortex-M0+ のブート・モード                |

| 1                     | x                                       | x                        | オプションのセキュア・ブート・リセット・ベクタ(SBRV)と<br>C2OPT |

| x                     | 1                                       | x                        | オプションのセキュア・ブート・リセット・ベクタ(SBRV)と<br>C2OPT |

| 0                     | 0                                       | 0                        | システムメモリ(セキュアファームウェアインストール)              |

| x                     | х                                       | 1                        | オプションのセキュア・ブート・リセット・ベクタ(SBRV)と<br>C2OPT |

7

Cortext-M0+ には 2 つのブート・モードがあります。1 つはセキュア・ブート・リセット・ベクタと CPU2 ブートオプションで定義するブート・モードです。もう 1 つはシステムメモリのセキュアファームウェアインストールでブートするブート・モードです。これらの 2 つのモードは、nBOOT0 オプション・ビットまたは BOOT0 ピン、nBOOT1 オプション・ビット、BOOT\_LOCK オプション・ビットで選択します。BOOT0、nBOOT1、BOOT\_LOCK の各オプション・ビットを 0 に設定すると、STM32WL5 によって Cortex-M4 がホールド状態になり、システムメモリに置かれた Cortex-M0+ セキュアファームウェアインストールでブートします。STM32WL5 で標準的な方法では、ユーザ Flash からCortex-M4 コアをブートし、次に Cortex-M0+ をブートします。この方法でブートするには、電源コントローラで C2BOOT ビットを設定します。

Cortex-M0+ をブートするメモリアドレスは、セキュア・ブート・リセット・ベクタと CPU2 ブートオプションで定義します。これにより、ユーザ Flash または SRAM メモリの中でワード整列している任意のアドレスから Cortex-M0+ をブートできます。

BOOT0 ピンまたは nBOOT0 オプション・ビットのどちらを使用するかは、別のオプション・ビットである nSWBOOT0 を使用して選択します。

## ブートローダ

| プロトコル | 1/0 とコメント                                                  | コメント |

|-------|------------------------------------------------------------|------|

| USART | USART1:PA9 ピンと PA10 ピン<br>USART2:PA2 ピンと PA3 ピン            |      |

| SPI   | SPI1:PA4、PA5、PA6、PA7 の各ピン<br>SPI2:PB12、PB13、PB14、PB15 の各ピン |      |

8

オンチップのブートローダを使用して、シリアル通信ペリフェラル 経由で Flash メモリをプログラムできます。サポートされているプロトコルは USART と SPI です。

# セキュアファームウェアインストール

• Cortex-M4 と Cortex-M0+ のソフトウェアをユーザ Flash に安全にインストール

9

オンチップのセキュアファームウェアインストールを使用して、 Cortex-M4 と Cortex-M0+ のソフトウェアを Flash メモリに安全 にインストールできます。

### SRAM2 の機能(1/2)

#### 性能、整合性、安全性(クラス B、SIL)、STANDBY 中に保持

- 32 KB Ø SRAM2

- Cortex-M4 の D-Code と I-Code によるアクセス:

- 再配置せずに最高のコード実行性能を実現

- S-バスによるアクセス:

- SRAM1 から連続する RAM アドレス空間

- HW パリティ・チェック:1 ワードあたり4ビット

- パリティ·エラー発生で NMI を生成

- ・ タイマへのブレーク入力(オプション)

- STANDBY 中にメモリの内容を保持(オプション)

10

32 KB の SRAM2 は、性能、整合性、安全性の確保と低消費電力動作に特に適しています。

メモリを再配置せずに、Cortex-M4 コアからデータバスと命令バス 経由で SRAM2 にアクセスするので、ウェイトステートを伴わずに コードを実行できます。両方の CPU から S-バス経由で SRAM2 メモリにアクセスできるので、SRAM1 メモリと SRAM2 メモリの間 で連続した RAM アドレスを使用できます。

SRAM2 はパリティ・チェックをサポートします。データバス幅が 36 なので、そのうち 4 ビットをパリティ・チェックに使用できます(1 バイトあたり 1 ビット)。これにより、クラス B や SIL の標準などで求められるメモリの堅牢性強化が実現します。クラス B と SIL は安全規格です。クラス B は生活家電向けの規格であり、SIL は「Safety Integrity Level」(安全度水準)の略語です。

パリティビットは、SRAM メモリに書き込むときに計算され、格納されます。その後、読み出すときに自動的にチェックされます。このチェックでビットが 1 つでもフェイルすると、ノンマスカブル割込み (NMI)が生成されます。同じエラーをタイマのブレーク入力にリンクすることもできます。

必要に応じて、STANDBY モード中に 32 KB の SRAM2 の内容を保持できます。

### SRAM2 の機能(2/2)

#### セキュアな SRAM

- 1 KB の粒度による書込み保護

- SYSCFG SWPRn 書込み保護レジスタ

- RDP による読出し保護と書込み保護

- RDP がレベル 1 からレベル 0 に変化すると消去を実行

- ソフトウェアリセットと、システムリセット時のハードウェアリセット(オプション)

- SRAM2ER ビットがセットされている場合は消去を実行

- ユーザ·オプション·バイトの SRAM2 RST に従ってシステム・リセット時に消去を実行

- Cortex-M0+ セキュリティ

- Cortex-M0+ から SRAM2 領域への排他的アクセス

SRAM2 メモリは、セキュアなアプリケーションにも適しています。 SRAM2 は、1 KB の粒度で書込み保護できます。

SRAM2 は、RDP オプション・バイトの設定によって読出し保護することもできます。システム Flash でのブートまたは SRAM メモリからのブートを選択している場合、保護状態の SRAM2 に対しては、JTAG とシリアル・ワイヤ・デバッグ(SWD)ポートのどちらからも読出しと書込みができません。読出し保護がレベル 1 からレベル 0 に変化すると SRAM2 は消去されます。詳細については、システムメモリ保護のトレーニングを参照してください。

SRAM2 のシステム設定で制御およびステータスレジスタの SRAM2ER ビットをセットすることによって、ソフトウェアで SRAM2 を消去できます。また、ユーザ・オプション・バイトのオプションビット SRAM2\_RST に応じて、システムリセットで SRAM2 を消去することもできます。

ユーザ・オプション・バイトを使用して Cortex-M0+ コアのみの排他的アクセスを付与することにより、SRAM2 の各領域をセキュリティで保護できます。

1.

### SYSCFG の他の機能

#### 安全性と堅牢性

- ・ 設定レジスタ 2 による安全性と堅牢性の機能

- SRAM2 パリティエラーフラグ

- ECC ロック: Flash ECC エラーを TIM1/15/16/17 のブレーク入力に接続

- PVD ロック: PVD 割込みを TIM1/16/17 のブレーク入力に接続

- SPL ロック: SRAM2 パリティエラーを TIM1/16/17 のブレーク入力に接続

- CLL ロック: Cortex-M4 ハードフォールト割込みを TIM1/16/17 のブレーク入力に接続

- => アプリケーションがクラッシュしたときにタイマを安全な状態に移行

12

システム設定レジスタ2には、SRAM2パリティエラーフラグなどの安全性と堅牢性にリンクしている制御ビットとステータス・ビットや、エラー検出イベントをタイマのブレーク入力に接続する制御ビットがあります。これにより、アプリケーションがクラッシュしたときに、タイマ出力を既知の状態に移行できます。プログラムした接続は、次回のシステムリセットまでロックされます。このような内部イベントとして、Flash エラーコード訂正イベント、電源電圧検出器イベント、SRAM2パリティエラーイベント、Cortex-M4 ハードフォールトなどがあります。

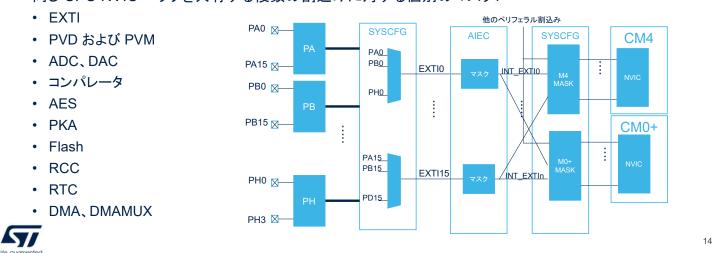

## SYSCFG の他の機能

- GPIOx(x=A~H)からの相互接続信号選択の管理

- 16 個のマルチプレクサにより、PA[n]、PB[n] ~ PH[n] (n=0 ~ 15)から EXTI[n] 信号を選択

- 次の目的で使用する GPIO[n] ピンの選択

- 内部相互接続トリガ信号(詳細については相互接続マトリックスを参照)

- CPU の割込みと STOP モードからのウェイクアップ(詳細については EXTI を参照)

- ・ 他の設定

- I2C GPIO 高速モードプラス 20 mA 駆動イネーブル

- I2C1 ピンと I2C3 ピンの高駆動は、これらのピンを I2C で使用しない場合でもイネーブル可能

- I/O アナログスイッチ電圧ブースタ

システム設定コントローラは、相互接続 EXTI 信号として使用する GPIO の選択を管理します。

この信号は、任意のマイクロコントローラを STOP 状態からウェイクアップする非同期外部割込みやイベントとして使用できるほか、ペリフェラルへの内部相互接続トリガ信号として使用することもできます。詳細については、相互接続マトリックスのトレーニングを参照してください。

ほかには、I2C1 と I2C3 の I/O に対する I<sup>2</sup>C 高速モード プラス 20 mA 駆動イネーブルの設定があります。この高 駆動モードは、これらのピンを I2C オルタネート機能で使 用しない場合でも使用できます。たとえば、LED の駆動 に使用できます。

I/O アナログスイッチ電圧ブースタも有効化できます。

# CPU 割込みのプリマスキング

- ペリフェラル割込みによって両方の CPU に対する割込みが発生しないように プリマスキングを用意

- 同じ CPU NVIC ベクタを共有する複数の割込みに対する個別のマスク:

同じ NVIC ベクタを共有する複数のペリフェラル割込みには、両方の CPU に対する割込みが生成されないようにプリマスクが用意されています。

# 関連ペリフェラル

- このペリフェラルにリンクされている次のトレーニングを参照:

- リセットおよびクロック制御(RCC)

- 電源コントローラ(PWR)

- 割込み(NVIC および EXTI)

- Flash メモリ(Flash)

- システムメモリの保護

- I<sup>2</sup>C (Inter-Integrated Circuit)

15

このトレーニングのほか、リセットおよびクロック制御、電源コントローラ、割込み、Flash、システムメモリの保護、I<sup>2</sup>C に関する各トレーニングを参照してください。

## 参考文書

- 詳細については、次のリソースを参照:

- AN2606:STM32 マイクロコントローラ システム・メモリ・ブート・モード

- AN4435: STM32アプリケーションでの UL/CSA/IEC 60730-1/60335-1 Class B 認定を取得するため のガイドライン

16

詳細については、アプリケーションノート AN2606 「STM32 マイクロコントローラ・システム・メモリ・ブート・モード」および AN4435 「STM32アプリケーションでの UL/CSA/IEC 60730-1/60335-1 Class B 認定を取得するためのガイドライン」を参照してください。